- DL manuals

- 4DSP

- Media Converter

- FMC204

- User Manual

4DSP FMC204 User Manual

Summary of FMC204

Page 1

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 1 - fmc204 user manual 4dsp llc, usa email: support@4dsp.Com this document is the property of 4dsp llc and may not be copied nor communicated to a third party without the written permission of 4dsp llc. © 4dsp llc 2014.

Page 2: Um008 Fmc204 User Manual

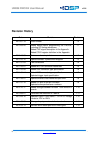

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 2 - revision history date revision revision 2010-07-19 initial release 1.0 2010-09-20 added details about programming the fmc204, including spi timing waveforms. Added fmc signal description in the appendix. Added cpld register definition in the ap...

Page 3: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 3 - table of contents 1 acronyms and related documents ............................................................................. 4 1.1 acronyms .......................................................................................................

Page 4: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 4 - 1 acronyms and related documents 1.1 acronyms adc analog-to-digital converter ddr double data rate eprom erasable programmable read-only memory fbga fineline ball grid array fmc fpga mezzanine card fpga field programmable gate array jtag join t...

Page 5: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 5 - 2 general description the fmc204 is a quad-channel d/a fmc. The fmc204 provides four 16-bit d\a channels that enable simultaneous sampling at a maximum rate of 1 gsps. The sample clock can be supplied externally through a coax connection or by ...

Page 6: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 6 - 3 installation 3.1 requirements and handling instructions the fmc204 daughter card must be installed on a carrier card compliant to the fmc standard. The fmc carrier card must support the high-pin count connector (hpc 400-pins). The carrier car...

Page 7: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 7 - 4 design 4.1 physical specifications 4.1.1 board dimensions the fmc204 card complies with the fmc standard known as ansi/vita 57.1. The card is a single-width, conduction-cooled mezzanine module (with region 1 and front panel i/o). 4.1.2 front ...

Page 8: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 8 - 4.2 electrical specifications the fmc204 uses high-speed lvds outputs. Revision 1 boards require +2.5v on vadj power supply (supplied by the carrier card). Revision 2 boards can operate with a vadj voltage range of 1.65v to 3.3v, but typically ...

Page 9: Um008 Fmc204 User Manual

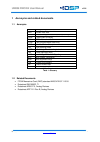

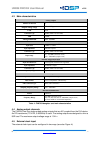

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 9 - # pairs # clock pairs # data pairs lvds clock 1 1 lvds trigger 1 1 lvds sync 1 1 dac #1 18 lvds clock 1 lvds sync 1 lvds data 16 dac #2 17 lvds clock 1 lvds sync 0 lvds data 16 2.5v or vadj level i/o routed to cpld (see board revision) 0 4 # to...

Page 10: Um008 Fmc204 User Manual

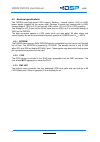

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 10 - 4.3 main characteristics analog outputs number of channels 4 output voltage range max. 1.0vp-p load 50Ω connector type ssmc (aep 7110-1511-000) thd -65dbc analog bandwidth max. 500mhz external clock/reference input input level -6dbm to +7dbm i...

Page 11: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 11 - 1. Sample clock input, connecting to the clock input of the ad9517. 2. Reference clock input, connecting to the reference input of the ad9517. 4.6 external trigger/sync input the external trigger input can be configured in different ways with ...

Page 12: Um008 Fmc204 User Manual

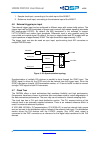

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 12 - clock to fmc vc(x)o 1.0 ghz xtal 100mhz loop filter dac 1 dac 0 rf switch rf switch clksrc_sel0 clksrc_sel1 clksrc_sel2 Π-attn figure 4: clock tree 4.7.1 control the clock tree contains two rf switches (adg918) and requires the following contr...

Page 13: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 13 - 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x 5 r x /5 t x figure 5: mgt interconnect topologies fmc 2 0 ,3 2 1 0 .0 0 7 .1 2 1 3 .7 1 fpga mictor 2 rx-tx 5-9 mictor 1 rx-t...

Page 14: Um008 Fmc204 User Manual

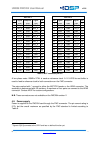

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 14 - mictor 1 mictor 2 pin signal midplate signal pin pin signal midplate signal pin 1 gnd gnd gnd 2 1 gnd gnd gnd 2 3 tx0_p * gnd rx0_p * 4 3 rx9_p gnd tx9_p 4 5 tx0_n * gnd rx0_n * 6 5 rx9_n gnd tx9_n 6 7 gnd gnd gnd 8 7 gnd gnd gnd 8 9 tx1_p * g...

Page 15: Um008 Fmc204 User Manual

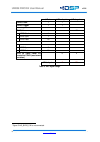

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 15 - voltage # pins max amps max watt +3.3v 4 3 a 10 w +12v 2 1 a 12 w vadj (+2.5v) 4 4 a 10 w vio_b (+2.5v) 2 1.15 a 2.3 w table 6: fmc standard power specification the power provided by the carrier card can be very noisy. Special care is taken wi...

Page 16: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 16 - fmc204 clock trigger/sync fmc204 clock trigger/sync fmc204 clock trigger/sync clock generation fs 50% fs/4 25% figure 7: synchronizing multiple cards 5 controlling the fmc204 5.1 architecture the fmc must be controlled from the carrier hardwar...

Page 17: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 17 - cpld dac0_n_cs dac1_n_cs clk_n_cs sclk sdio clksrc_sel[0:2] syncsrc_sel[0:1] refmon ld status vm_n_int and fmc_to_cpld(1) n_cs fmc_to_cpld(2) sdio fmc_to_cpld(0) sclk fmc side local side led src_sel reg0 reg1 reg2 shift register fmc_to_cpld(3)...

Page 18: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 18 - 8-bit pre-selection p6 p5 p4 p3 p2 p1 p0 r/w a6 a5 a4 a3 a2 a1 a0 8-bit instruction 8-bit register data d7 d6 d5 d4 d3 d3 d1 d0 n_cs sclk sdio p7 figure 9: write instruction to cpld registers a1:a0 8-bit pre-selection p6 p5 p4 p3 p2 p1 p0 r/w ...

Page 19: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 19 - 8-bit pre-selection p6 p5 p4 p3 p2 p1 p0 r/w w1 w0 a12 a11 a10 a9 a8 16-bit instruction 8-bit register data n_cs sclk sdio p7 d7 d6 d5 d4 d3 d3 d1 d0 a6 a5 a4 a3 a2 a1 a0 a7 figure 14: read instruction to ad9517 registers a12:a0 6 environment ...

Page 20: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 20 - 6.3 cooling two different types of cooling are available for the fmc204. 6.3.1 convection cooling the air flow provided by the fans of the chassis the fmc204 is enclosed in will dissipate the heat generated by the on board components. A minimu...

Page 21: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 21 - 9 warranty hardware software/firmware basic warranty (included) 1 year from date of shipment 90 days from date of shipment extended warranty (optional) 2 years from date of shipment 1 year from date of shipment.

Page 22: Um008 Fmc204 User Manual

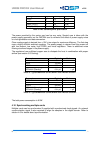

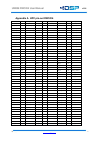

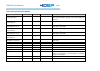

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 22 - appendix a hpc pin-out fmc204 av57.1 hpc pin fmc204 signal av57.1 hpc pin fmc204 signal av57.1 hpc pin fmc204 signal clk0_m2c_n h5 clk_to_fpga_n ha00_n_cc f5 n.C. Hb10_n k32 dac1_data_p clk0_m2c_p h4 clk_to_fpga_p ha00_p_cc f4 n.C. Hb10_p k31 ...

Page 23: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 23 - la18_n_cc c23 n.C. Ha22_n j22 n.C. Dp4_c2m_n a35 dp_c2m_n la18_p_cc c22 n.C. Ha22_p j21 n.C. Dp4_c2m_p a34 dp_c2m_p la19_n h23 dac0_data_p ha23_n k23 n.C. Dp4_m2c_n a15 dp_m2c_n la19_p h22 dac0_data_n ha23_p k22 n.C. Dp4_m2c_p a14 dp_m2c_p la2...

Page 24: Fmc204 User Manual

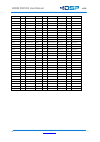

Fmc204 user manual r1.13 table 9: hpc signal description (fmc204) signal group direction i/o standard description clk_to_fpga_n clk_to_fpga_p d/a 0, d/a 1 output lvds clock to be used as reference clock for generating dac clock and data signals. Typically, half of the sample clock frequency. Dac0_dc...

Page 25: Um008 Fmc204 User Manual

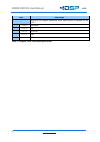

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 25 - appendix b cpld register map bit nr. Bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 name ‘0’ dacr clkr syncsrc clksrc table 10: register cpld_reg0 definition field description clksrc selection of clock source ‘000’ external clock ‘011’ intern...

Page 26: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 26 - field description dirx direction of front io transceiver (x = 0 to 3) ‘0’ signal x is input (fmc204 is receiver) ‘1’ signal x is output (fmc204 is transmitter) fanx power control for fan header (x = 0 to 3) ‘0‘ apply power to fan header x ‘1‘ ...

Page 27: Um008 Fmc204 User Manual

Um008 fmc204 user manual r1.14 um008 www.4dsp.Com - 27 - field description led_sel writing to this register determines which status signal is indicated by the led. ‘xxxx1‘ refmon ‘xxx10‘ ld ‘xx100‘ status ‘x1000‘ vm ‘10000‘ irq table 17: register cpld_reg2 description (write).