Conexant Fusion 878A Manual - Table Of Contents

100600B

Conexant

iii

Table of Contents

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Analog Video and Digital Camera Capture

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Vertical Blanking Interval Data Capture

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

C Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

TM

Functionality

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Operating Principles of UltraLock

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Y/C Separation and Chroma Demodulation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Summary of Fusion 878A

Page 1

Data sheet 100600b december 3, 1999 fusion™ 878a pci video decoder the fusion 878a is a complete, low cost, single-chip solution for analog broadcast signal capture on the pci bus. The fusion 878a takes advantage of the pci-based system’s high bandwidth and inherent multimedia capability. It is desi...

Page 2

100600b conexant information provided by conexant systems, inc. (conexant) is believed to be accurate and reliable. However, no responsibility is assumed by conexant for its use, nor any infringement of patents, copyrights, or other rights of third parties which may result from its use. No license i...

Page 3: Table Of Contents

100600b conexant iii table of contents list of figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Xi list of tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 4

Table of contents fusion 878a pci video decoder iv conexant 100600b 2.4 video scaling, cropping, and temporal decimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7 2.4.1 down-scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5

Fusion 878a table of contents pci video decoder 100600b conexant v 2.14 multifunction arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48 2.14.1 normal pci mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

Table of contents fusion 878a pci video decoder vi conexant 100600b 3.5 i2c serial eeprom interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23 3.5.1 eeprom address mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 7

Fusion 878a table of contents pci video decoder 100600b conexant vii msb cropping register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11 0x00c—even field (e_crop) 0x08c—odd field (o_crop) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 8

Table of contents fusion 878a pci video decoder viii conexant 100600b 0x0b4—total line count register (vtotal_hi) . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27 0x0d4—color format register (color_fmt) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28 0x0d8—color control register...

Page 9: List of Figures

Fusion 878a list of figures pci video decoder 100600b conexant xi list of figures figure 1-1. Fusion 878a detailed block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2 figure 1-2. Fusion 878a audio/video decoder and scaler block diagram . . . . . . . ....

Page 10

List of figures fusion 878a pci video decoder xii conexant 100600b figure 3-8. Gpio spi input mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12 figure 3-9. Gpio spi output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 11: List of Tables

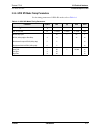

Fusion 878a list of tables pci video decoder 100600b conexant xiii list of tables table 1-1. Audio/video capture product family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1 table 1-2. Pin descriptions grouped by pin function . . . . . . . . . . . . . . . ....

Page 12

List of tables fusion 878a pci video decoder xiv conexant 100600b.

Page 13: 1.0 Product Overview

100600b conexant 1-1 1 1.0 product overview 1.1 functional overview the fusion 878a video and audio capture chip is a multi-function peripheral component interconnect (pci) device intended for +5 v only operation. The video function features a direct memory access (dma)/pci bus master for analog nts...

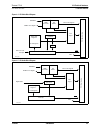

Page 14

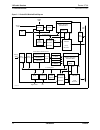

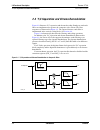

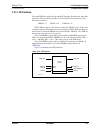

1.0 product overview fusion 878a 1.1 functional overview pci video decoder 1-2 conexant 100600b figure 1-1. Fusion 878a detailed block diagram i2s video decoder video scaler ycrcb 4:2:2, 4:1:1 csc/gamma 8-bit dither mux fifos : y 70x36 cb: 35x36 : cr 35x36 # dwords dma controller pci initiator gpio ...

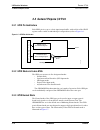

Page 15

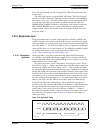

Fusion 878a 1.0 product overview pci video decoder 1.1 functional overview 100600b conexant 1-3 figure 1-2. Fusion 878a audio/video decoder and scaler block diagram composite 1 composite 2 composite 3 composite/s-video (y) s-video (c) cin agccap refp xto xti stv tv-audio sfm radio-audio sml mic or l...

Page 16: 1.2 Detailed Features

1.0 product overview fusion 878a 1.2 detailed features pci video decoder 1-4 conexant 100600b 1.2 detailed features 1.2.1 video capture the fusion 878a integrates an ntsc/pal/secam composite and s-video decoder, scaler, dma controller, and pci bus master on a single device. The fusion 878a can place...

Page 17

Fusion 878a 1.0 product overview pci video decoder 1.2 detailed features 100600b conexant 1-5 1.2.5 video dma channels the fusion 878a enables separate destinations for the odd and even fields, each controlled by a pixel risc instruction list. This instruction list is created by the fusion 878a devi...

Page 18

1.0 product overview fusion 878a 1.2 detailed features pci video decoder 1-6 conexant 100600b 1.2.8 pci bus interface the fusion 878a is designed to efficiently utilize the available 132 mbps pci bus. The 32-bit dwords are output on the pci bus with the appropriate image data under the control of th...

Page 19

Fusion 878a 1.0 product overview pci video decoder 1.2 detailed features 100600b conexant 1-7 the clock signal interface consists of a pair of pins that connect to a 28.63636 mhz (8 × ntsc fsc) crystal. Either fundamental or third harmonic crystals may be used. Alternatively, cmos oscillators may be...

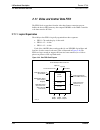

Page 20: 1.3 Pin Descriptions

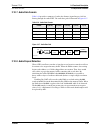

1.0 product overview fusion 878a 1.3 pin descriptions pci video decoder 1-8 conexant 100600b 1.3 pin descriptions figure 1-3 displays the pinout diagram. Table 1-2 provides a description of pin functions grouped by common function. Figure 1-3. Fusion 878a pinout diagram 64 63 62 61 60 59 58 57 56 55...

Page 21

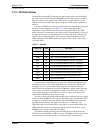

Fusion 878a 1.0 product overview pci video decoder 1.3 pin descriptions 100600b conexant 1-9 table 1-2. Pin descriptions grouped by pin function (1 of 4) pin # pin name i/o signal description pci interface (50 pins) (1) 40 clk i clock this input provides timing for all pci transactions. All pci sign...

Page 22

1.0 product overview fusion 878a 1.3 pin descriptions pci video decoder 1-10 conexant 100600b 25 frame i/o cycle frame this sustained, three-state signal is driven by the current master to indicate the beginning and duration of an access. Frame is asserted to signal the beginning of a bus transactio...

Page 23

Fusion 878a 1.0 product overview pci video decoder 1.3 pin descriptions 100600b conexant 1-11 i 2 c interface (2 pins) 90 scl i/o serial clock bus clock, output open drain. 91 sda i/o serial data bit data or acknowledge, output open drain. General purpose i/o (25 pins) 66 gpclk i/o gp clock video cl...

Page 24

1.0 product overview fusion 878a 1.3 pin descriptions pci video decoder 1-12 conexant 100600b 103 vrxp a audio input circuitry reference voltage. This pin should be connected to an external filtering 0.1 µf capacitor. 102 vrxn a audio input circuitry reference voltage. This pin should be connected t...

Page 25: 2.0 Functional Description

100600b conexant 2-1 2 2.0 functional description 2.1 ultralock tm functionality 2.1.1 the challenge the line length (the interval between the midpoints of the falling edges of succeeding horizontal sync pulses) of analog video sources is not constant. For a stable source such as studio quality sour...

Page 26

2.0 functional description fusion 878a 2.1 ultralock tm functionality pci video decoder 2-2 conexant 100600b pixels per line. Ultralock then interpolates the required number of pixels in a way that maintains the stability of the original image despite variation in the line length of the incoming ana...

Page 27

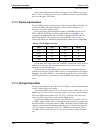

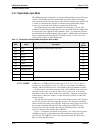

Fusion 878a 2.0 functional description pci video decoder 2.2 composite video input formats 100600b conexant 2-3 2.2 composite video input formats fusion 878a supports several composite video input formats. Table 2-1 shows the video formats and some of the countries in which each format is used. The ...

Page 28

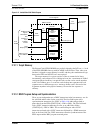

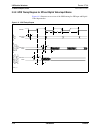

2.0 functional description fusion 878a 2.3 y/c separation and chroma demodulation pci video decoder 2-4 conexant 100600b 2.3 y/c separation and chroma demodulation figure 2-2 illustrates y/c separation and chroma decoding. Band-pass and notch filters are implemented to separate the composite video s...

Page 29

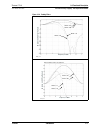

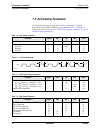

Fusion 878a 2.0 functional description pci video decoder 2.3 y/c separation and chroma demodulation 100600b conexant 2-5 figure 2-3. Y/c separation filter responses ntsc pal/secam ntsc pal/secam luma notch filter frequency responses for ntsc and pal/secam chroma band pass filter frequency responses ...

Page 30

2.0 functional description fusion 878a 2.3 y/c separation and chroma demodulation pci video decoder 2-6 conexant 100600b figure 2-4. Filtering and scaling note(s): z –1 refers to a pixel delay in the horizontal direction, and a line delay in the vertical direction. The coefficients are determined by...

Page 31: Decimation

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-7 2.4 video scaling, cropping, and temporal decimation the fusion 878a provides three mechanisms to reduce the amount of video pixel data in its output stream: down-scalin...

Page 32

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-8 conexant 100600b figure 2-5. Optional horizontal luma low-pass filter responses ntsc pal/secam icon qcif cif icon qcif cif amplitude in db [20*log10(ampl)] amplitude in db [20*log10(ampl...

Page 33

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-9 vertical scaling for vertical scaling, the fusion 878a uses a line store to implement four different filtering options. The filter characteristics are illustrated in fig...

Page 34

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-10 conexant 100600b 2.4.1.4 peaking the fusion 878a enables four different peaking levels by programming the peak bit and hfilt bits in the scloop register. The filters are illustrated in ...

Page 35

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-11 figure 2-10. Peaking filters hfilt = 01 hfilt = 10 hfilt = 11 hfilt = 00 amplitude in db [20*log10(ampl)] 879a_014 frequency in mhz hfilt = 01 hfilt = 11 hfilt = 10 hfi...

Page 36

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-12 conexant 100600b figure 2-11. Luma peaking filters with 2x oversampling filter and luma notch (1 of 2) hfilt = 10 hfilt = 01 hfilt = 11 hfilt = 00 hfilt = 01 hfilt = 11 hfilt = 10 hfilt...

Page 37

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-13 2.4.1.5 chrominance scaling a 2-tap, 32-phase interpolation filter is used for horizontal scaling of chrominance. Vertical scaling of chrominance is implemented through...

Page 38

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-14 conexant 100600b for example, to scale pal/secam input to square pixel qcif, the total number of horizontal pixels desired is 236: an alternative method for determining the hscale value...

Page 39

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-15 the following c-code fragment illustrates changing the vertical scaling value: #define vscale_hi 0x13 #define vscale_lo 0x14 typedef unsigned char byte; typedef unsigne...

Page 40

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-16 conexant 100600b 2.4.2 image cropping cropping enables the user to output any subsection of the video image. The start of the active area in the vertical direction is referenced to vres...

Page 41

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-17 figure 2-12. Effect of the cropping and active registers beginning of a new frame beginning of a new line video frame horizontally active horizontally inactive vertical...

Page 42

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-18 conexant 100600b 2.4.2.1 cropping registers horizontal delay register (hdelay) for video decoding, hdelay is programmed with the number of pixels between horizontal sync and the first p...

Page 43

Fusion 878a 2.0 functional description pci video decoder 2.4 video scaling, cropping, and temporal decimation 100600b conexant 2-19 the vertical delay register (vdelay) for video decoding, vdelay is programmed with the number of half lines between the end of the serration pulses and the first line t...

Page 44

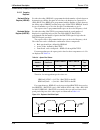

2.0 functional description fusion 878a 2.4 video scaling, cropping, and temporal decimation pci video decoder 2-20 conexant 100600b when changing the programming in the temporal decimation register, 0x00 should be loaded first, and then the decimation value. This ensures that the decimation counter ...

Page 45: 2.5 Video Adjustments

Fusion 878a 2.0 functional description pci video decoder 2.5 video adjustments 100600b conexant 2-21 2.5 video adjustments the fusion 878a provides programmable hue, contrast, saturation, and brightness. 2.5.1 the hue adjust register the hue adjust register (hue) is used to offset the hue of the dec...

Page 46

2.0 functional description fusion 878a 2.6 automatic chrominance gain control pci video decoder 2-22 conexant 100600b 2.6 automatic chrominance gain control the automatic chrominance gain control (acgc) compensates for reduced chrominance and color-burst amplitudes. Here, the color-burst amplitude i...

Page 47: 2.8 Coring

Fusion 878a 2.0 functional description pci video decoder 2.8 coring 100600b conexant 2-23 2.8 coring the fusion 878a video decoder can perform a coring function, in which it forces all values below a programmed level to be 0. This is useful as the human eye is more sensitive to variations in black i...

Page 48

2.0 functional description fusion 878a 2.9 vbi data output interface pci video decoder 2-24 conexant 100600b 2.9 vbi data output interface a frame of video is composed of 525 lines for nstc and 625 for pal/secam. Figure 2-15 illustrates an ntsc video frame, in which there are a number of distinct re...

Page 49

Fusion 878a 2.0 functional description pci video decoder 2.9 vbi data output interface 100600b conexant 2-25 the fusion 878a is able to capture vbi data and store it in the host memory for later processing by the fusion 878a vbi decoder software. Two modes of vbi capture exist: vbi line output mode ...

Page 50

2.0 functional description fusion 878a 2.9 vbi data output interface pci video decoder 2-26 conexant 100600b in the vbi frame output mode, vbi data capture occurs in the active video region and includes all the horizontal blank/sync information in the data stream. This feature can be used to provide...

Page 51

Fusion 878a 2.0 functional description pci video decoder 2.10 video data format conversion 100600b conexant 2-27 2.10 video data format conversion 2.10.1 pixel data path the video decoder/scaler portion of the fusion 878a generates a video data stream in packed 4:2:2 ycrcb format. The video data is ...

Page 52

2.0 functional description fusion 878a 2.10 video data format conversion pci video decoder 2-28 conexant 100600b figure 2-19. Video data format converter 879a_024 from bt879 family video decoder/scaler packed 4:2:2 packed 4:2:2 packed 4:2:2 up-sample chroma 4:4:4 color space conversion strip chroma ...

Page 53

Fusion 878a 2.0 functional description pci video decoder 2.10 video data format conversion 100600b conexant 2-29 table 2-5. Color formats format dword pixel data [31:0] byte lane 3 [31:24] byte lane 2 [23:16] byte lane 1 [15:8] byte lane 0 [7:0] rgb32 (1) dw0 alpha r g b rgb24 dw0 b1 r0 g0 b0 dw1 g2...

Page 54

2.0 functional description fusion 878a 2.10 video data format conversion pci video decoder 2-30 conexant 100600b 2.10.3 ycrcb to rgb conversion the 4:2:2 ycrcb data stream from the video decoder portion of the fusion 878a must be converted to 4:4:4 ycrcb before the rgb conversion occurs, using an in...

Page 55

Fusion 878a 2.0 functional description pci video decoder 2.10 video data format conversion 100600b conexant 2-31 sub-sampling is achieved. In the yuv9 format, lines 2–4 of cr/cb data are discarded, and hence 4:1:1 vertical sub-sampling is achieved. 2.10.6 byte swapping before the data enters the fif...

Page 56

2.0 functional description fusion 878a 2.11 video and control data fifo pci video decoder 2-32 conexant 100600b 2.11 video and control data fifo the fifo block accepts data from the video data format conversion process, buffers the data in fifo memory, then outputs dwords to the dma controller to be...

Page 57

Fusion 878a 2.0 functional description pci video decoder 2.11 video and control data fifo 100600b conexant 2-33 2.11.2 fifo data interface loading data into the fifo can begin only when valid pixels are present during the even or the odd field. The pixel dword pixel data (pd) [31:0] is stored in fi[...

Page 58

2.0 functional description fusion 878a 2.11 video and control data fifo pci video decoder 2-34 conexant 100600b planar mode and packed mode data can be present in the fifos at the same time if a bus access latency persists across a field transition, or if packed vbi data proceeds planar ycrcb data. ...

Page 59

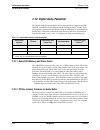

Fusion 878a 2.0 functional description pci video decoder 2.11 video and control data fifo 100600b conexant 2-35 table 2-9. Table of pci bus access latencies video format resolution mode max bus latency before fifo overflow ( µ s) ntsc 30 fps 640 x 480 rgb32 10 rgb24 13 rgb16/ycrcb 4:2:2 20 ycrcb 4:1...

Page 60: 2.12 Dma Controller

2.0 functional description fusion 878a 2.12 dma controller pci video decoder 2-36 conexant 100600b 2.12 dma controller the fusion 878a incorporates a unique dma controller architecture that gives the capture system great flexibility in its ability to deliver data to memory. It is designed as a small...

Page 61

Fusion 878a 2.0 functional description pci video decoder 2.12 dma controller 100600b conexant 2-37 2.12.1 target memory the fusion 878a’s fifo dwords are perfectly aligned to the pci bus: i.E., bit 0 of the fifo dwords lines up with bit ad[0] on the pci bus. Thus, video scan line data is aligned to ...

Page 62

2.0 functional description fusion 878a 2.12 dma controller pci video decoder 2-38 conexant 100600b the software will set up a pixel data flow by creating a risc instruction sequence in the host memory for the odd and even fields. The dma controller normally branches through the risc instruction sequ...

Page 63

Fusion 878a 2.0 functional description pci video decoder 2.12 dma controller 100600b conexant 2-39 write123 1001 5 write pixels to memory in planar mode from the fifos beginning at the specified target addresses. Dword0: [11:0] byte count #1 byte transfer count from fifo1 [15:12] byte enables [23:16...

Page 64

2.0 functional description fusion 878a 2.12 dma controller pci video decoder 2-40 conexant 100600b write1s23 1011 3 write pixels to memory in planar mode from the fifo1 beginning at the specified target addresses. Skip pixels from fifo2 and fifo3. This instruction is used to achieve the yuv9 and yuv...

Page 65

Fusion 878a 2.0 functional description pci video decoder 2.12 dma controller 100600b conexant 2-41 skip 0010 1 skip pixels by discarding byte-count number of bytes from the fifo. This may start and stop in the middle of a dword. Dword0: [11:0] byte count [13:12] byte offset [15:14] reserved [23:16] ...

Page 66

2.0 functional description fusion 878a 2.12 dma controller pci video decoder 2-42 conexant 100600b each risc instruction consists of 1 to 5 dwords. The 32-bits in the dwords relay information such as the opcode, target address, status codes, synchronization codes, byte count/enables, and start/end o...

Page 67

Fusion 878a 2.0 functional description pci video decoder 2.12 dma controller 100600b conexant 2-43 writec cannot be used to begin a new line; i.E., this instruction cannot have the sol bit set. Write123, write1s23, and skip123 control the processing of active pixel data stored in the fifos. These th...

Page 68

2.0 functional description fusion 878a 2.12 dma controller pci video decoder 2-44 conexant 100600b 2.12.5 executing instructions once the dma controller has achieved synchronization between the fifo and the risc program, it starts executing the risc instructions. The data in the fifo will be aligned...

Page 69

Fusion 878a 2.0 functional description pci video decoder 2.12 dma controller 100600b conexant 2-45 queued dwords. The dma controller will ignore the fifo trigger point because it needs to empty the fifo immediately. Otherwise it may not have a chance to empty the rest of the fifos before it has to r...

Page 70

2.0 functional description fusion 878a 2.12 dma controller pci video decoder 2-46 conexant 100600b the planar mode requires that the dma controller give priority to the y fifo to be emptied first. If there is a very long latency in getting access to the pci bus, all three fifos will be almost full w...

Page 71: 2.13 Byte Alignment

Fusion 878a 2.0 functional description pci video decoder 2.13 byte alignment 100600b conexant 2-47 2.13 byte alignment the video function dma controllers and pci initiators are enhanced for byte resolution on target addresses in packed color modes. The fifo dword-aligned data is realigned with the c...

Page 72

2.0 functional description fusion 878a 2.14 multifunction arbiter pci video decoder 2-48 conexant 100600b 2.14 multifunction arbiter an internal arbiter is necessary to determine whether the video or audio dma controller claims the pci bus when a gnt is issued to the fusion 878a. Only one of the two...

Page 73

Fusion 878a 2.0 functional description pci video decoder 2.14 multifunction arbiter 100600b conexant 2-49 2.14.3 interfacing with non-pci 2.1 compliant core logic a small percentage of core logic devices may start a bus transaction during the same cycle that gnt is de-asserted. This is non pci 2.1 c...

Page 74: 2.15 Audio A/d

2.0 functional description fusion 878a 2.15 audio a/d pci video decoder 2-50 conexant 100600b 2.15 audio a/d 2.15.1 muxing and anti-aliasing filtering before entering the audio a/d, the tv, fm, and microphone/line audio inputs are selected by a_sel and multiplexed. The mux selects are break-before-m...

Page 75

Fusion 878a 2.0 functional description pci video decoder 2.15 audio a/d 100600b conexant 2-51 in addition to the switched capacitor gain control, there is a +6 db switch in the pre-amp. This additional amplification is enabled if a_g2x is set high. Thus, when a_gain equals 3 and a_g2x equals 1, the ...

Page 76

2.0 functional description fusion 878a 2.16 high speed serial interface mode pci video decoder 2-52 conexant 100600b 2.16 high speed serial interface mode the same interface used for digital audio may be used for other types of digital serial data. With default settings, the maximum data rate into t...

Page 77: Data Capture

Fusion 878a 2.0 functional description pci video decoder 2.17 asynchronous data parallel mode: raw data capture 100600b conexant 2-53 2.17 asynchronous data parallel mode: raw data capture the asynchronous data parallel port interface allows the user to multiplex raw data from the gpio port into the...

Page 78

2.0 functional description fusion 878a 2.18 digital audio packetizer pci video decoder 2-54 conexant 100600b 2.18 digital audio packetizer the digital audio packetizer (dap) block can packetize data input on asclk, alrck, and adata in two additional modes besides normal i 2 s mode. It can also packe...

Page 79

Fusion 878a 2.0 functional description pci video decoder 2.18 digital audio packetizer 100600b conexant 2-55 2.18.3 fifo interface the audio fifo de couples the high-speed pci interface from the slow audio data packetizer. The size chosen provides for efficient pci bursts and effective pci bus laten...

Page 80

2.0 functional description fusion 878a 2.18 digital audio packetizer pci video decoder 2-56 conexant 100600b 2.18.4 audio packets and data capture audio samples are grouped into a line packet of length alp_len bytes. The audio line packets are grouped to form an audio field packet of length afp_len ...

Page 81

Fusion 878a 2.0 functional description pci video decoder 2.18 digital audio packetizer 100600b conexant 2-57 bytes. The data following one line of length alp_len will begin the next line (no data lost). The alp_len sequence is repeated afp_len times. The last 36-bit word written to the fifo contains...

Page 82

2.0 functional description fusion 878a 2.18 digital audio packetizer pci video decoder 2-58 conexant 100600b there can be any number of asclks ≥ 16 (usually 16–32 between alrck edges. Thus there may be extra asclks versus collected data bits. There is no requirement for asclk (or alrck or adata)) to...

Page 83

Fusion 878a 2.0 functional description pci video decoder 2.18 digital audio packetizer 100600b conexant 2-59 2.18.7 audio data formats table 2-14 provides a summary of audio data formats (signed integer 16/8-bit) flowing through the audio fifo. The audio data path is illustrated in figure 2-27 . 2.1...

Page 84

2.0 functional description fusion 878a 2.19 digital television support pci video decoder 2-60 conexant 100600b 2.19 digital television support digital television support will be available through upcoming application notes. Please contact the local sales office for availability..

Page 85: 3.0 Electrical Interfaces

100600b conexant 3-1 3 3.0 electrical interfaces 3.1 input interface 3.1.1 analog signal selection the fusion 878a contains an on-chip 4:1 multiplexer (mux[3:0]) that can be used to switch between four composite sources or three composite sources and one s-video source. In the first configuration, c...

Page 86

3.0 electrical interfaces fusion 878a 3.1 input interface pci video decoder 3-2 conexant 100600b 3.1.2 multiplexer considerations the video multiplexer is not a break-before-make design. Therefore, during multiplexer switching time, it is possible for the input video signals to be momentarily connec...

Page 87

Fusion 878a 3.0 electrical interfaces pci video decoder 3.1 input interface 100600b conexant 3-3 3.1.3 flash a/d converters the fusion 878a uses two on-chip flash a/d converters to digitize the video signals. Yref+, cref+ and yref–, cref– are the respective top and bottom of the internal resistor la...

Page 88

3.0 electrical interfaces fusion 878a 3.1 input interface pci video decoder 3-4 conexant 100600b this clock is used to generate the clkx2 frequency via the following equation: these values should be programmed as follows to generate pal frequencies: the pll can be put into low power mode by setting ...

Page 89

Fusion 878a 3.0 electrical interfaces pci video decoder 3.1 input interface 100600b conexant 3-5 the clock source tolerance should be 50 ppm or less. Devices that output cmos voltage levels are required. The load capacitance in the crystal configurations may vary depending on the magnitude of board ...

Page 90

3.0 electrical interfaces fusion 878a 3.1 input interface pci video decoder 3-6 conexant 100600b 3.1.8 2x oversampling and input filtering digitized video needs to be band-limited in order to avoid aliasing artifacts. Because the fusion 878a samples the video data at 8 × fsc (over twice the normal r...

Page 91

Fusion 878a 3.0 electrical interfaces pci video decoder 3.1 input interface 100600b conexant 3-7 figure 3-3. Luma and chroma 2x oversampling filter ntsc pal/secam ntsc pal/secam amplitude in db [20*log10(ampl)] amplitude in db [20*log10(ampl)] frequency in mhz frequency in mhz 0 -5 -10 -15 -20 -25 -...

Page 92: 3.2 Pci Bus Interface

3.0 electrical interfaces fusion 878a 3.2 pci bus interface pci video decoder 3-8 conexant 100600b 3.2 pci bus interface the pci local bus is an architectural, timing, electrical, and physical interface that allows the fusion 878a to interface to the local bus of a host cpu. The fusion 878a is fully...

Page 93

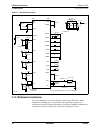

Fusion 878a 3.0 electrical interfaces pci video decoder 3.2 pci bus interface 100600b conexant 3-9 figure 3-4. Pci video block diagram fifo data fifo control signals video decoder interrupts clk dma controller pci initiator pci control signals pci config. Registers local registers interrupts gpio i ...

Page 94

3.0 electrical interfaces fusion 878a 3.3 general purpose i/o port pci video decoder 3-10 conexant 100600b 3.3 general purpose i/o port 3.3.1 gpio pin architecture each gpio pin is set up as a basic input/output buffer, with each bit of the gpoe register used to enable an individual pin’s output dri...

Page 95

Fusion 878a 3.0 electrical interfaces pci video decoder 3.3 general purpose i/o port 100600b conexant 3-11 i data is written to and read from the gpio pins through the gpdata signal. When configured to output signals through the gpio, information is written to a gpdata holding register, which is out...

Page 96

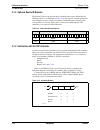

3.0 electrical interfaces fusion 878a 3.3 general purpose i/o port pci video decoder 3-12 conexant 100600b 3.3.4 spi input mode spi input mode is used to input synchronous pixel interface video information into the part. The interface accepts 16-bit ycrcb video data. Because the incoming video is in...

Page 97

Fusion 878a 3.0 electrical interfaces pci video decoder 3.3 general purpose i/o port 100600b conexant 3-13 3.3.5 spi output mode spi output mode is used to output data from the decoder/scaler block of the part. This does not change the regular output of the part. Refer to figure 3-9 . When running t...

Page 98

3.0 electrical interfaces fusion 878a 3.3 general purpose i/o port pci video decoder 3-14 conexant 100600b figure 3-10 illustrates spi output clock-data timing information. The falling edge of the output gpclk triggers the change in video data. This should allow for ample setup and hold times for an...

Page 99

Fusion 878a 3.0 electrical interfaces pci video decoder 3.3 general purpose i/o port 100600b conexant 3-15 related video timing signals for both fields are illustrated in figure 3-11 . Note that in fields 1, 3, 5, and 7 the falling edge of hreset is two clock cycles ahead of the falling edge of vres...

Page 100

3.0 electrical interfaces fusion 878a 3.3 general purpose i/o port pci video decoder 3-16 conexant 100600b figure 3-11. Video timing in spi output mode note(s): (1) hreset precedes vreset by two clock cycles at the beginning of fields 1, 3, 5 and 7 to facilitate external field generation. 2. Field t...

Page 101

Fusion 878a 3.0 electrical interfaces pci video decoder 3.3 general purpose i/o port 100600b conexant 3-17 3.3.6 gpio spi mode timing parameters for the timing parameters of gpio sp1 mode, refer to table 3-4 . Table 3-4. Gpio spi mode timing parameters parameter symbol min typ max units ntsc: 4 × f ...

Page 102

3.0 electrical interfaces fusion 878a 3.3 general purpose i/o port pci video decoder 3-18 conexant 100600b 3.3.7 digital video input mode the gpio port can be configured to accept general digital data streams. The parts contain a tg_ram-based state machine that isolates the digital video input event...

Page 103

Fusion 878a 3.0 electrical interfaces pci video decoder 3.3 general purpose i/o port 100600b conexant 3-19 3.3.7.2 modified smpte-125 the modified smpte-125 interface is the same as ccir656, but the clock runs at 24.54 mhz, with 640 active pixels on a 780 pixel line. This clock rate difference provi...

Page 104

3.0 electrical interfaces fusion 878a 3.3 general purpose i/o port pci video decoder 3-20 conexant 100600b 3.3.8 gpio timing diagram for spi and digital video input modes figure 3-13 illustrates an overview of the gpio timing for spi input and digital video input modes. Figure 3-13. Gpio timing diag...

Page 105: 3.4 I

Fusion 878a 3.0 electrical interfaces pci video decoder 3.4 i 2 c interface 100600b conexant 3-21 3.4 i 2 c interface the i 2 c bus is a two-wire serial interface. Serial clock and data lines, scl, and sda transfer data between the bus master and the slave device. The i 2 c bus within the fusion 878...

Page 106

3.0 electrical interfaces fusion 878a 3.4 i 2 c interface pci video decoder 3-22 conexant 100600b in the case where direct control of the i 2 c bus lines is desired, the fusion 878a device driver can disable the i 2 c hardware control and can take software control of the scl and sda pins. This is us...

Page 107: 3.5 I

Fusion 878a 3.0 electrical interfaces pci video decoder 3.5 i2c serial eeprom interface 100600b conexant 3-23 3.5 i 2 c serial eeprom interface the external eeprom must reside on the i 2 c bus (sda, scl). This interface supports the ic’s equivalent to the 24c02 or 24c02a 2 k bit 5 v cmos serial eepr...

Page 108

3.0 electrical interfaces fusion 878a 3.5 i2c serial eeprom interface pci video decoder 3-24 conexant 100600b 3.5.2 subsystem vendor id pci configuration header location 0x2c specifies the subsystem vendor id and the subsystem id. If an external eeprom is present, the subsystem vendor id and subsyst...

Page 109

Fusion 878a 3.0 electrical interfaces pci video decoder 3.5 i2c serial eeprom interface 100600b conexant 3-25 3.5.2.3 programming and write-protect the eeprom can be programmed before soldering onto the pcb, or it may be programmed through fusion 878a using the i 2 c hardware or software modes. The ...

Page 110

3.0 electrical interfaces fusion 878a 3.5 i2c serial eeprom interface pci video decoder 3-26 conexant 100600b 3.5.3.2 vital product data read sequence when sw resets the vpd flag bit, the device initiates the following i 2 c sequence to read four bytes from the eeprom (assumes vpd address was set to...

Page 111

Fusion 878a 3.0 electrical interfaces pci video decoder 3.5 i2c serial eeprom interface 100600b conexant 3-27 the device resets the vpd flag bit once all four bytes from the vpd data register are programmed into the eeprom. If a slave nack is received during either page write, the sequence is aborte...

Page 112

3.0 electrical interfaces fusion 878a 3.6 power management interface pci video decoder 3-28 conexant 100600b 3.6 power management interface fusion 878a supports the new capabilities feature for power management as outlined in pci bus power management interface specification, revision 1.1. Power mana...

Page 113: 3.7 Jtag Interface

Fusion 878a 3.0 electrical interfaces pci video decoder 3.7 jtag interface 100600b conexant 3-29 3.7 jtag interface 3.7.1 need for functional verification as the complexity of imaging chips increases, the need to easily access individual chips for functional verification is becoming vital. The fusio...

Page 114

3.0 electrical interfaces fusion 878a 3.7 jtag interface pci video decoder 3-30 conexant 100600b 3.7.3 optional device id register the fusion 878a has the optional device identification register defined by the jtag specification as displayed in table 3-10 . This register contains information concern...

Page 115: 4.1 Layout Considerations

100600b conexant 4-1 4 4.0 pc board layout considerations 4.1 layout considerations the pc board layout should be optimized for lowest noise on the fusion 878a power and ground lines. Route digital traces away from analog traces. All shields must be connected to the ground plane with low impedance c...

Page 116

4.0 pc board layout considerations fusion 878a 4.1 layout considerations pci video decoder 4-2 conexant 100600b and around the fusion 878a, if possible. Avoid creating a cut in the plane with feed-throughs: instead, disperse them. To fill: • copper fill ground on the component side • power fill on t...

Page 117

Fusion 878a 4.0 pc board layout considerations pci video decoder 4.2 split planes and voltage regulators 100600b conexant 4-3 4.2 split planes and voltage regulators the reference designs included in the bt878/fusion 878a hardware users guide have no split planes. Careful attention has been given to...

Page 118: 4.3 Latchup Avoidance

4.0 pc board layout considerations fusion 878a 4.3 latchup avoidance pci video decoder 4-4 conexant 100600b 4.3 latchup avoidance latchup is possible with all cmos devices. It is triggered when any signal pin exceeds the voltage on the power pins associated with that pin by more than 0.5 v, or falls...

Page 119

100600b conexant 5-1 5 5.0 control register definitions-function 0 the fusion 878a supports two types of address spaces: function 0 and function 1. This chapter defines function 0. The configuration address space includes the predefined pci configuration registers. The memory address space includes ...

Page 120

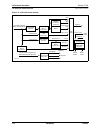

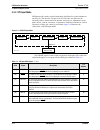

5.0 control register definitions-function 0 fusion 878a 5.1 pci configuration space pci video decoder 5-2 conexant 100600b figure 5-1. Function 0 pci configuration space header status command class code 0x00 0x04 0x08 0x0c 0x10 0x14 0x18 0x1c 0x20 0x24 0x28 0x2c 0x30 0x34 0x38 0x3c 0x40 0x44 0x4b 0x...

Page 121

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.2 pci configuration registers (header) 100600b conexant 5-3 5.2 pci configuration registers (header) the following types are used to specify how the fusion 878a registers are implemented: 0x00 — vendor and device id register...

Page 122

5.0 control register definitions-function 0 fusion 878a 5.2 pci configuration registers (header) pci video decoder 5-4 conexant 100600b 0x08 — revision id and class code register 0x0c — header type, latency timer register 0x10 — base address 0 register 0x2c — subsystem id and subsystem vendor id reg...

Page 123

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.2 pci configuration registers (header) 100600b conexant 5-5 0x3c — interrupt line, interrupt pin, min_gnt, max_lat register min_gnt and max_lat values are dependent on target performance (trdy) and video mode (scale factors ...

Page 124

5.0 control register definitions-function 0 fusion 878a 5.2 pci configuration registers (header) pci video decoder 5-6 conexant 100600b 0x44 — vpd capability register 0x48 — vpd data register 0x4c — power management capability register bits type default name description [31] rw vpd_flag this flag is...

Page 125

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.2 pci configuration registers (header) 100600b conexant 5-7 0x50 — power management support registers bits type default name description [31:24] ro 0x00 pwr-data this field is used to report the state dependent data requeste...

Page 126

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-8 conexant 100600b 5.3 local registers (memory mapped) fusion 878a’s local registers reside in the 4 kb memory addressed space reserved for each function. All of the registers correspond t...

Page 127

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-9 0x000 — device status register (dstatus) upon reset dstatus is initialized to 0x00. Cof is the lsb. The cof and lof status bits hold their values until reset to their de...

Page 128

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-10 conexant 100600b 0x004—input format register (iform) upon reset iform is initialized to 0x58. Format(0) is the lsb. 0x008—temporal decimation register (tdec) upon reset tdec is initiali...

Page 129

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-11 msb cropping register) 0x00c—even field (e_crop) 0x08c—odd field (o_crop) upon reset this register is initialized to 0x12. Hactive_msb(0) is the lsb. See the vactive, v...

Page 130

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-12 conexant 100600b horizontal delay register, lower byte 0x018—even field (e_delay_lo) 0x098—odd field (o_delay_lo) upon reset this register is initialized to 0x78. Hdelay_lo(0) is the ls...

Page 131

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-13 0x028—brightness control register (bright) upon reset this register is initialized to 0x00. Bits type default name description [7:0] rw 0x00 bright the brightness contr...

Page 132

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-14 conexant 100600b miscellaneous control register 0x02c—even field (e_control) 0x0ac—odd field (o_control) upon reset this register is initialized to 0x20. Sat_v_msb is the lsb. Bits type...

Page 133

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-15 0x030—luma gain register, lower byte (contrast_lo) upon reset contrast_lo is initialized to 0xd8. Contrast_lo(0) is the lsb. Contrast equals the con_msb plus the lsbyte...

Page 134

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-16 conexant 100600b 0x034—chroma (u) gain register, lower byte (sat_u_lo) upon reset sat_u_lo is initialized to 0xfe. Sat_u_lo(0) is the lsb. Sat_u_msb in the miscellaneous control registe...

Page 135

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-17 0x038—chroma (v) gain register, lower byte (sat_v_lo) upon reset sat_v_lo is initialized to 0xb4. Sat_v_lo(0) is the lsb. Sat_v_msb in the miscellaneous control registe...

Page 136

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-18 conexant 100600b 0x03c—hue control register (hue) upon reset hue is initialized to 0x00. Hue(0) is the lsb. Bits type default name description [7:0] rw 0x00 hue hue adjustment involves ...

Page 137

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-19 sc loop control register 0x040—even field (e_scloop) 0x0c0—odd field (o_scloop) bits type default name description [7] rw 0 peak this bit determines whether the normal ...

Page 138

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-20 conexant 100600b 0x044 — white crush up register (wc_up) this control register may be written to or read by the mpu at any time, and upon reset it is initialized to 0xcf. Upcnt(0) is th...

Page 139

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-21 vertical scaling register, upper byte 0x04c—even field (e_vscale_hi) 0x0cc—odd field (o_vscale_hi) upon reset this register is initialized to 0x60. Vertical scaling reg...

Page 140

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-22 conexant 100600b 0x5b—audio reset register (areset) upon reset, areset is initialized to 0x00. 0x060—agc delay register (adelay) upon reset, adelay is initialized to 0x68. 0x064—burst d...

Page 141

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-23 0x068—adc interface register (adc) upon reset, adc is initialized to 0x82. Crush is the lsb. Bits type default name description [7:6] 10 [5] reserved this bit is reserv...

Page 142

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-24 conexant 100600b video timing control register 0x6c—even field (e_vtc) 0xec—odd field (o_vtc) upon reset, this register is initialized to 0x00. Vfilt(0) is the lsb. 0x07c—software reset...

Page 143

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-25 0x078—white crush down register this control register may be written to or read by the mpu at any time, and upon reset is initialized to 0x7f. Dncnt(0) is the least sig...

Page 144

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-26 conexant 100600b 0x084—timing generator control (tgctrl) register upon reset, tgctrl is initialized to 00. 7 reserved must be written with a logical zero. [6:5] rw tgcko gpclk output cl...

Page 145

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-27 0x0b0—total line count register (vtotal_lo) if this register is set to non-zero, the 10-bit value will change the decoder’s vertical synchronization line count from the...

Page 146

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-28 conexant 100600b 0x0d4—color format register (color_fmt) bits type default name description [7:4] rw 0000 color_odd odd field color format 0000 = rgb32 0001 = rgb24 0010 = rgb16 0011 = ...

Page 147

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-29 0x0d8—color control register (color_ctl) a value of 1 enables byte swapping of data entering the fifo. B3[31:24] is swapped with b2[23:16] and b1[15:8] is swapped with ...

Page 148

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-30 conexant 100600b 0x0e0—vbi packet size register (vbi_pack_size) 0x0e4—vbi packet size / delay register (vbi_pack_del) 0x0e8—field capture counter register (fcap) upon reset fcap is init...

Page 149

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-31 0x0f8—integer register (pll-xci) upon reset this register is initialized to 00. 0x0fc—digital video signal interface format (dvsif) register upon reset, dvsif is initia...

Page 150

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-32 conexant 100600b 0x100—interrupt status register (int_stat) this register provides status of pending interrupt conditions. To clear the interrupts, read this register and write the same...

Page 151

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-33 0x104—interrupt mask register (int_mask) [5] rr 0 vpres set when the analog video signal input changes from present to absent or vice versa. [4] rr 0 hlock set if the h...

Page 152

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-34 conexant 100600b 0x10c—gpio and dma control register (gpio_dma_ctl) bits type default name description [15] rw 0 gpintc a value of 0 selects the direct non-inverted/inverted input from ...

Page 153

Fusion 878a 5.0 control register definitions-function 0 pci video decoder 5.3 local registers (memory mapped) 100600b conexant 5-35 0x110—i2c data/control register bits type default name description [31:24] rw — i2cdb0 first byte sent in an i 2 c transaction. Typically this will be the base or chip ...

Page 154

5.0 control register definitions-function 0 fusion 878a 5.3 local registers (memory mapped) pci video decoder 5-36 conexant 100600b 0x114—risc program start address register (risc_strt_add) 0x118—gpio output enable control register (gpio_out_en) 0x120—risc program counter register (risc_count) 0x200...

Page 155

100600b conexant 6-1 6 6.0 control register definitions–function 1 this chapter defines function 1 address spaces. As in the previous chapter, the configuration address space includes the pre-defined pci configuration registers. The memory address space includes all the local registers used by fusio...

Page 156

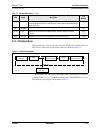

6.0 control register definitions–function 1 fusion 878a 6.1 pci configuration space pci video decoder 6-2 conexant 100600b figure 6-1. Function 1 pci configuration space header status command class code 0x00 0x04 0x08 0x0c 0x10 0x14 0x18 0x1c 0x20 0x24 0x28 0x2c 0x30 0x34 0x38 0x3c 0x40 0x44 0x4b 0x...

Page 157

Fusion 878a 6.0 control register definitions–function 1 pci video decoder 6.2 pci configuration registers (header) 100600b conexant 6-3 6.2 pci configuration registers (header) the following types specify how the fusion 878a registers are implemented: 0x00—vendor and device id register 0x04—command ...

Page 158

6.0 control register definitions–function 1 fusion 878a 6.2 pci configuration registers (header) pci video decoder 6-4 conexant 100600b 0x08—revision id and class code register 0x0c—header type register 0x0c—latency timer register 0x10—base address 0 register [8] rw 0 serr enable a value of 1 enable...

Page 159

Fusion 878a 6.0 control register definitions–function 1 pci video decoder 6.2 pci configuration registers (header) 100600b conexant 6-5 0x2c—subsystem id and subsystem vendor id register 0x34—capabilities pointer register 0x3c—interrupt line, interrupt pin, min_gnt, max_lat register bits type defaul...

Page 160

6.0 control register definitions–function 1 fusion 878a 6.2 pci configuration registers (header) pci video decoder 6-6 conexant 100600b 0x40 — device control register 0x44—vpd capability register bits type default name description [7:3] ro 00000 reserved [2] rw 0 en_vsfx enables via/sis pci controll...

Page 161

Fusion 878a 6.0 control register definitions–function 1 pci video decoder 6.2 pci configuration registers (header) 100600b conexant 6-7 0x48—vpd data register 0x4c—power management capability register bits type default name description [31:0] rw* — vpd data always transfers 4 bytes between the vpd d...

Page 162

6.0 control register definitions–function 1 fusion 878a 6.2 pci configuration registers (header) pci video decoder 6-8 conexant 100600b 0x50—power management support register bits type default name description [31:24] ro 0x00 pwr-data this field is used to report the state-dependent data requested b...

Page 163

Fusion 878a 6.0 control register definitions–function 1 pci video decoder 6.3 local registers (memory mapped) 100600b conexant 6-9 6.3 local registers (memory mapped) fusion 878a’s local registers reside in the 4 kb memory-addressed space reserved for each function. All of the registers correspond t...

Page 164

6.0 control register definitions–function 1 fusion 878a 6.3 local registers (memory mapped) pci video decoder 6-10 conexant 100600b 0x100—interrupt status register (int_stat) this register provides the status of pending interrupt conditions. To clear the interrupts, read this register, then write th...

Page 165

Fusion 878a 6.0 control register definitions–function 1 pci video decoder 6.3 local registers (memory mapped) 100600b conexant 6-11 0x104—interrupt mask register (int_mask) 0x10c—audio control register (gpio_dma_ctl) [3] rr 0 oflow set when an overflow is detected in audio a/d nominal range. [2] ro ...

Page 166

6.0 control register definitions–function 1 fusion 878a 6.3 local registers (memory mapped) pci video decoder 6-12 conexant 100600b [21] rw 0 da_mlb selects most significant or lsb format for adata 0 = msb first for i 2 s format 1 = lsb first for sony format [20:16] rw 00000 da_lrd specifies how man...

Page 167

Fusion 878a 6.0 control register definitions–function 1 pci video decoder 6.3 local registers (memory mapped) 100600b conexant 6-13 0x110—audio packet lengths register 0x114—risc program start address register (risc_strt_add) 0x120—risc program counter register (risc_count) bits type default name de...

Page 168

6.0 control register definitions–function 1 fusion 878a 6.3 local registers (memory mapped) pci video decoder 6-14 conexant 100600b.

Page 169: 7.0 Parametric Information

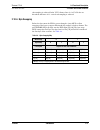

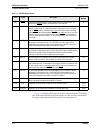

100600b conexant 7-1 7 7.0 parametric information 7.1 dc electrical parameters dc electrical parameters are specified in tables 7-1 through 7-3 . Table 7-1. Recommended operating conditions parameter symbol min typ max units power supply — analog v aa , v bb 4.75 5.00 5.25 v power supply — digital v...

Page 170

7.0 parametric information fusion 878a 7.1 dc electrical parameters pci video decoder 7-2 conexant 100600b table 7-2. Absolute maximum ratings parameter symbol min max units v aa (measured to agnd) v aa , v bb — 7.00 v v dd (measured to gnd) v dd — 7.00 v voltage on any signal pin (1) — dgnd – 0.5 v...

Page 171

Fusion 878a 7.0 parametric information pci video decoder 7.1 dc electrical parameters 100600b conexant 7-3 input high current (v in = 2.7 v i ih — — 70 µa input low current (v in = 0.5 v) i il — — –70 µa input capacitance (f = 1 mhz, v in = 2.4 v) c in — 5 — pf digital outputs pci outputs output hig...

Page 172

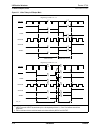

7.0 parametric information fusion 878a 7.2 ac electrical parameters pci video decoder 7-4 conexant 100600b 7.2 ac electrical parameters ac electrical parameters are specified in tables 7-4 through 7-7 . Timing diagrams for clock, gpio, and jtag are provided in figures 7-1 through 7-2 , respectively....

Page 173

Fusion 878a 7.0 parametric information pci video decoder 7.2 ac electrical parameters 100600b conexant 7-5 figure 7-2. Jtag timing diagram 10 11 15 16 12 13 tdi, tms tck tdo 14 879a_052 table 7-7. Decoder performance parameters parameter symbol min typ max units horizontal lock range ±7 % of line le...

Page 174

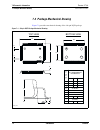

7.0 parametric information fusion 878a 7.3 package mechanical drawing pci video decoder 7-6 conexant 100600b 7.3 package mechanical drawing figure 7-3 provides a mechanical drawing of the 128-pin pqfp package. Figure 7-3. 128-pin pqfp package mechanical drawing all dimensions in millimeters s y m b ...

Page 175: Appendix A. Acronym List

100600b conexant a-1 a appendix a. Acronym list the acronym list does not include names of pins, registers, or bits. A/d analog-to-digital acgc automatic chrominance gain control acpi advanced configuration and power interface adc analog to digital conversion af audio frequency afe audio front end a...

Page 176

Appendix a . Acronym list fusion 878a pci video decoder a-2 conexant 100600b gfx graphics controller gpio general purpose input/output i 2 c inter-integrated circuit ic integrated circuit id identification ieee institute of electrical and electronic engineers int integer itu international telecommun...

Page 177

Fusion 878a appendix a . Acronym list pci video decoder 100600b conexant a-3 vcr video cassette recorder vdfc video data format conversion vfe video front end vpd vital product data vtc video timing controller y/c luminance and chrominance.

Page 178

Appendix a . Acronym list fusion 878a pci video decoder a-4 conexant 100600b.

Page 180

Further information literature@conexant.Com 1-800-854-8099 (north america) 33-14-906-3980 (international) web site www.Conexant.Com world headquarters conexant systems, inc. 4311 jamboree road p. O. Box c newport beach, ca 92658-8902 phone: (949) 483-4600 fax: (949) 483-6375 u.S. Florida/south ameri...