Fairchild FEB107-001 User Manual - page 12

© 2005 Fairchild Semiconductor

Page 12

of 14

Rev 2.0 March 2005

www.fairchildsemi.com

6.2 Layout considerations

The FEB107-001 Evaluation board contains high impedance, low level signals and low impedance, high level

circuits. Consequently, it requires extra care in component placement, grounding and PC trace routing. In

order to shield low level circuits from the high level signals, the control circuits are placed in surface mount form

on the bottom side of the board. Since the current sense for the FAN4803 is not differential, care must be taken

to prevent large di/dt across the PCB trace joining the output capacitor and the current sense resistor. As the best

place to reference the IC is at the output capacitor return potential (the most stable potential), the difference

between this potential and the current sense resistor return potential must be kept to a minimum. This is

accomplished by “starring” all 400V return connections to the output capacitor, and/or “starring” very low

inductive/resistive paths from all power devices to the output capacitor return. Output common mode capaci-

tors C23 and C26, along with a ground plane, have been added as a low impedance path for shunting output

common mode currents back to the source through C20 and C19. Although it is not absolutely necessary for a

functioning FEB107-001 Evaluation Board, it does help to reduce high frequency output noise and improve

output voltage regulation.

The following list some general layout guidelines.

A. Bypass the VCC pin directly to the IC ground pin with a 1µF ceramic capacitor, located as close as possible

to the IC.

B. Return all compensation components directly to the IC ground pin, keeping the lead lengths as short as

possible.

C. Make sure that low level noise-free returns do not share return paths with high level, or noisy signals,

e.g.

,

gate drive.

D. Isolate and or shield rapidly changing high voltage waveforms from sensitive, high impedance circuits, such

as the timing capacitor, PFC current sense input, error amplifier input/output,

etc.

E. “Star” connect all power return paths to the boost output capacitor C1.

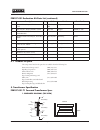

7. Featured Products

7.1 FAN4803 Description

The FAN4803 is a space-saving controller for power factor corrected, switched mode power supplies that offers

very low start-up and operating currents.

Power Factor Correction (PFC) offers the use of smaller, lower cost bulk capacitors, reduces power line loading

and stress on the switching FETs, and results in a power supply fully compliant to IEC1000-3-2 specifications.

The FAN4803 includes circuits for the implementation of a leading edge, average current "boost" type PFC and

a trailing edge, PWM.

The FAN4803-1’s PFC and PWM operate at the same frequency, 67kHz. The PFC frequency of the FAN4803-

2 is automatically set at half that of the 134kHz PWM. This higher frequency allows the user to design with

smaller PWM components while maintaining the optimum operating frequency for the PFC. An overvoltage

comparator shuts down the PFC section in the event of a sudden decrease in load. The PFC section also includes

peak current limiting for enhanced system reliability.

7.1.1 FAN4803 Features

• Internally synchronized PFC and PWM in one 8-pin IC

• Patented one-pin voltage error amplifier with advanced input current shaping technique

• Peak or average current, continuous boost, leading edge PFC (Input Current Shaping Technology)

• High efficiency trailing-edge current mode PWM

• Low supply currents; start-up: 150µA typ., operating: 2mA typ.

• Synchronized leading and trailing edge modulation