- DL manuals

- HOLT

- Motherboard

- ADK-5200

- Quick Start Manual

HOLT ADK-5200 Quick Start Manual

Summary of ADK-5200

Page 1

Qsg-5200 rev. A holt integrated circuits adk-5200 quick start guide: hi-5200 10base-t/100base-tx physical layer transceiver april 2018.

Page 2

Qsg-5200 2 holt integrated circuits revision history revision date description of change qsg-5200, rev. New 02-09-18 initial release rev. A 04-23-18 remove hi-5201 option.

Page 3

Qsg-5200 3 holt integrated circuits introduction the holt hi-5200 is a 10base-t/100base-tx physical layer transceiver with both mii and rmii mac interfaces. It utilizes a unique mixed-signal design to extend signaling distance while reducing power consumption, and offers hp auto mdi/mdi-x for reliab...

Page 4

Qsg-5200 4 holt integrated circuits features ● holt 10base-t/100base-tx physical layer transceiver ● rj-45 jack for fast ethernet cable interface ● hp auto-mdix for automatic detection and correction for straight-through and crossover cables ● mii (media independent interface) connector to interface...

Page 5

Qsg-5200 5 holt integrated circuits mii (media independent interface) default configuration the mii interface is defined by clause 22 of the ieee 802.3 specification. The hi-5200 phy evaluation board receives power and accesses mii data and management information from the mii connector j1. In mii mo...

Page 6

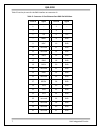

Qsg-5200 6 holt integrated circuits j1 pin # signal j1 pin # signal 29 txen 30 gnd 31 txd0 32 gnd 33 txd1 34 gnd 35 txd2 36 gnd 37 txd3 38 gnd 39 col 40 gnd 41 crs 42 gnd 43 +5v 44 +5v 45 -- 46 -- 47 -- 48 -- 49 -- 50 -- rmii (reduced media independent interface) configuration option the hi-5200 adk...

Page 7

Qsg-5200 7 holt integrated circuits table 2 lists the pin outs for the rmii interface on connector j1. Table 2. Connector j1 fast ethernet port rmii pin definition. J1 pin # signal j1 pin # signal 1 -- 2 -- 3 -- 4 -- 5 +5v 6 +5v 7 mdio 8 gnd 9 mdc 10 gnd 11 not used 12 gnd 13 not used 14 gnd 15 rxd1...

Page 8

Qsg-5200 8 holt integrated circuits j1 pin # signal j1 pin # signal 43 +5v 44 +5v 45 -- 46 -- 47 -- 48 -- 49 -- 50 --.

Page 9

Qsg-5200 9 holt integrated circuits jumper setting & definition the hi-5200 adk phy evaluation board does not require any jumper for normal operation. At power-up, the hi-5200 adk phy is configured using the chip’s internal pull-up and pull-down resistors with its default strapping pin values. Jumpe...

Page 10

Qsg-5200 10 holt integrated circuits table 4 lists the pin strapping definitions for the hi-5200 adk phy evaluation board jumpers. Table 4. Hi-5200pc pin strapping options on phy evaluation board. Jumper u1 pin # pin name pin function jp3 jp2 jp1 15 14 13 phyad2 phyad1 phyad0 the phy address is latc...

Page 11

Qsg-5200 11 holt integrated circuits test point definition the hi-5200 adk phy evaluation board has six test points. They are defined in the following table. Table 5. Hi-5200pc phy evaluation board test points. Test point description tp1 interrupt signal (u1 pin 21) with external pull-up tp2 signal ...

Page 12

Qsg-5200 12 holt integrated circuits led indicators the board has two led indicators (led0 and led1). Led1 is connected to pin 31 and led0 is connected to pin 30 of the hi-5200pc (u1), the two leds are programmable to led mode ‘00’ or ‘01’ via register 1e (hex), bits [15:14], and are defined in the ...

Page 13

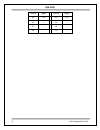

Pcb rev. A p/n: hv032 bill of materials hi-520x pc pq evaluation board item qty description reference digikey p/n mfg p/n 1 1 pcb, bare, evaluation board n/a jettech # 42169 2 7 capacitor cer 0.1uf 25v 10% x7r 0805 c4,c5,c7,c11, c12,c13,c15 399-1168-1-nd kemet c0805c104k3ractu 3 2 capacitor cer 22pf...

Page 14

1 1 2 2 3 3 4 4 5 5 d d c c b b a a txen_a rxd3_a rxd1_a txd2_a ledk0 txd1_a rxd2_a rxer_a rxd0_a rxd1_a rxd3_a rxdv_a ledk0 rxd2_a col_a crs_a ledk1 crs_a rxdv_a rstn intrp_a rxc_a rxer_a rxd0_a col_a ledk1 txc_a txd3_a txd0_a txp txn xo xi txn signal_gnd mdc_a rxn txp ledk1 ledk0 mdio_a rxp tx+ rx...