- DL manuals

- IBM

- Computer Hardware

- A2

- User Manual

IBM A2 User Manual

Summary of A2

Page 1

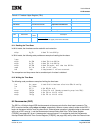

A2 processor user’s manual for blue gene/q note: this document and the information it contains are provided on an as-is basis. There is no plan for providing for future updates and corrections to this document. October 23, 2012 version 1.3 title page.

Page 2

® copyright and disclaimer © copyright international business machines corporation 2010, 2012 printed in the united states of america october 2012 ibm, the ibm logo, and ibm.Com are trademarks or registered trademarks of international business machines corp., registered in many jurisdictions worldwi...

Page 3

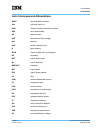

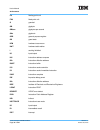

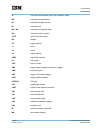

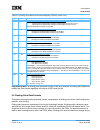

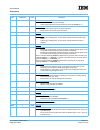

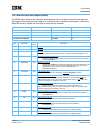

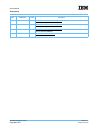

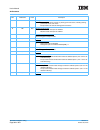

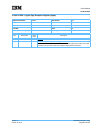

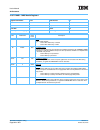

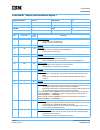

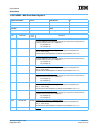

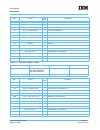

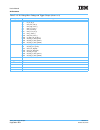

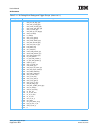

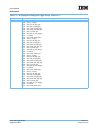

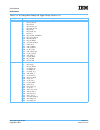

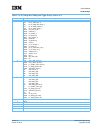

User’s manual a2 processor version 1.3 october 23, 2012 contents page 3 of 864 contents list of figures ............................................................................................................... 21 list of tables .....................................................................

Page 4

User’s manual a2 processor contents page 4 of 864 version 1.3 october 23, 2012 2. Cpu programming model ......................................................................................... 61 2.1 logical partitioning .................................................................................

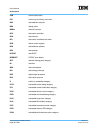

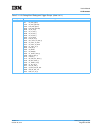

Page 5

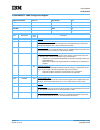

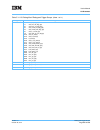

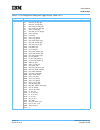

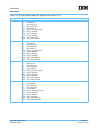

User’s manual a2 processor version 1.3 october 23, 2012 contents page 5 of 864 2.6 instruction categories ..................................................................................................................... 86 2.7 instruction classes ....................................................

Page 6

User’s manual a2 processor contents page 6 of 864 version 1.3 october 23, 2012 2.10.2.3 carry (ca) field .......................................................................................................... 112 2.10.2.4 transfer byte count (tbc) field ..............................................

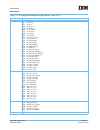

Page 7

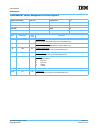

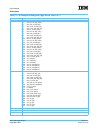

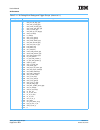

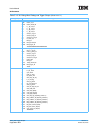

User’s manual a2 processor version 1.3 october 23, 2012 contents page 7 of 864 3.6.2 load and store instructions ................................................................................................. 145 3.6.3 floating-point store instructions ................................................

Page 8

User’s manual a2 processor contents page 8 of 864 version 1.3 october 23, 2012 5.5.3.6 data cache disable ...................................................................................................... 183 6. Memory management .....................................................................

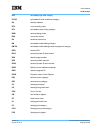

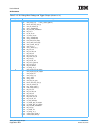

Page 9

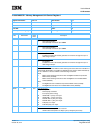

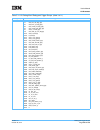

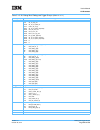

User’s manual a2 processor version 1.3 october 23, 2012 contents page 9 of 864 6.11.2 32-bit mode tlb search instruction (tlbsx[.]) ................................................................. 225 6.11.3 32-bit mode tlb search and reserve instruction (tlbsrx.) .....................................

Page 10

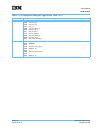

User’s manual a2 processor contents page 10 of 864 version 1.3 october 23, 2012 6.17.27 logical page exception register upper (lperu) ........................................................... 274 6.17.28 mas register update summary .....................................................................

Page 11

User’s manual a2 processor version 1.3 october 23, 2012 contents page 11 of 864 7.6.8 floating-point unavailable interrupt .................................................................................... 342 7.6.9 system call interrupt ...............................................................

Page 12

User’s manual a2 processor contents page 12 of 864 version 1.3 october 23, 2012 8.4.1 invalid operation exception ................................................................................................. 375 8.4.1.1 action ........................................................................

Page 13

User’s manual a2 processor version 1.3 october 23, 2012 contents page 13 of 864 10.4.2.3 dac debug events applied to instructions that result in multiple storage accesses 407 10.4.2.4 dac debug events applied to various instruction types ......................................... 408 10.4.3 data valu...

Page 14

User’s manual a2 processor contents page 14 of 864 version 1.3 october 23, 2012 10.11 pc configuration register 0 (pccr0) ...................................................................................... 444 10.12 trace and trigger bus ..............................................................

Page 15

User’s manual a2 processor version 1.3 october 23, 2012 contents page 15 of 864 12.3.1 erat read entry (eratre) ................................................................................................. 496 12.3.2 erat write entry (eratwe) ........................................................

Page 16

User’s manual a2 processor contents page 16 of 864 version 1.3 october 23, 2012 14.5.15 dac4 - data address compare 4 .................................................................................... 557 14.5.16 dbcr0 - debug control register 0 .......................................................

Page 17

User’s manual a2 processor version 1.3 october 23, 2012 contents page 17 of 864 14.5.65 lpidr - logical partition id register .............................................................................. 616 14.5.66 lr - link register ...................................................................

Page 18

User’s manual a2 processor contents page 18 of 864 version 1.3 october 23, 2012 14.5.115 tenc - thread enable clear register .......................................................................... 675 14.5.116 tens - thread enable set register ........................................................

Page 19

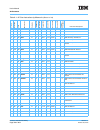

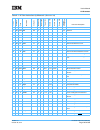

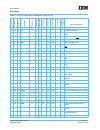

User’s manual a2 processor version 1.3 october 23, 2012 contents page 19 of 864 appendix a. Processor instruction summary ......................................................... 737 a.1 instruction formats ...............................................................................................

Page 20

User’s manual a2 processor contents page 20 of 864 version 1.3 october 23, 2012 d.4.11 tlb management instruction dependencies .................................................................... 845 d.4.12 processor control instruction operation ........................................................

Page 21

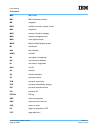

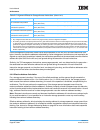

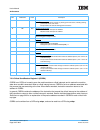

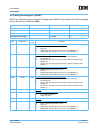

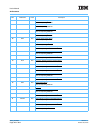

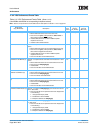

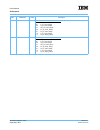

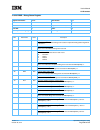

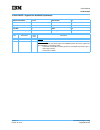

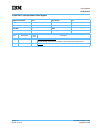

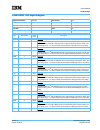

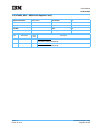

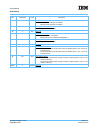

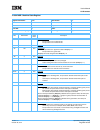

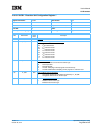

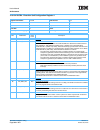

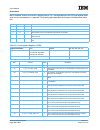

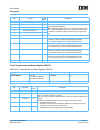

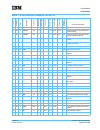

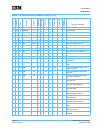

User’s manual a2 processor version 1.3 october 23, 2012 list of figures page 21 of 864 list of figures figure 1-1. A2 core organization ............................................................................................................. 50 figure 1-2. A2 processor block diagram ...............

Page 22

User’s manual a2 processor list of figures page 22 of 864 version 1.3 october 23, 2012.

Page 23

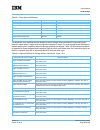

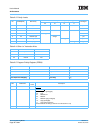

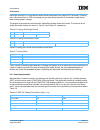

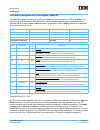

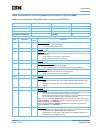

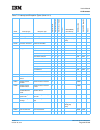

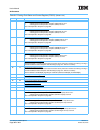

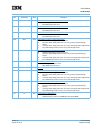

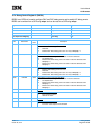

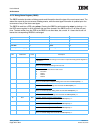

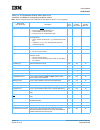

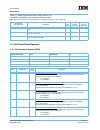

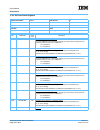

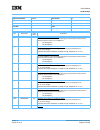

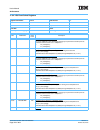

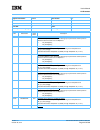

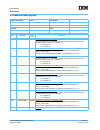

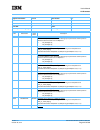

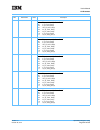

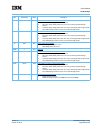

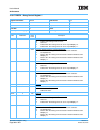

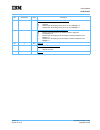

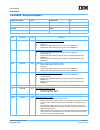

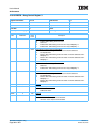

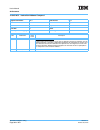

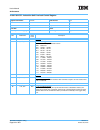

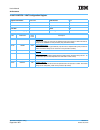

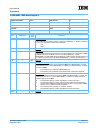

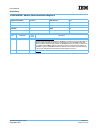

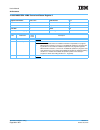

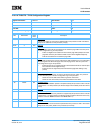

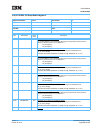

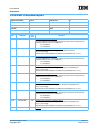

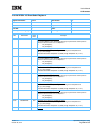

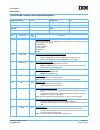

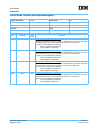

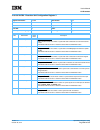

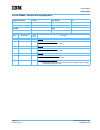

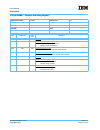

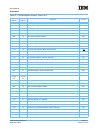

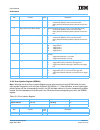

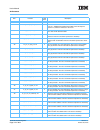

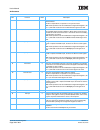

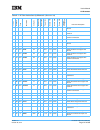

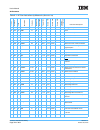

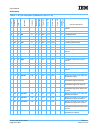

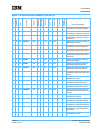

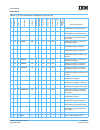

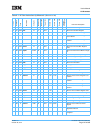

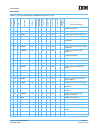

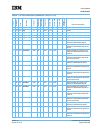

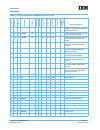

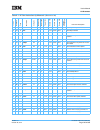

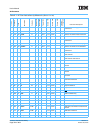

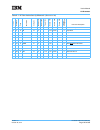

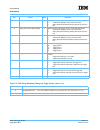

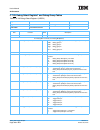

User’s manual a2 processor version 1.3 october 23, 2012 list of tables page 23 of 864 list of tables table 2-1. Data operand definitions ....................................................................................................... 63 table 2-2. Alignment effects for storage access instruct...

Page 24

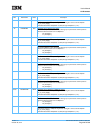

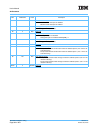

User’s manual a2 processor list of tables page 24 of 864 version 1.3 october 23, 2012 table 2-39. Xer[ca] updating instructions ............................................................................................111 table 2-40. Sprg0 register ....................................................

Page 25

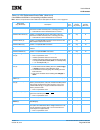

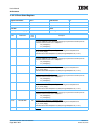

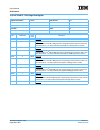

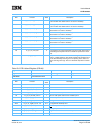

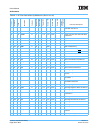

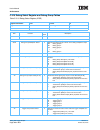

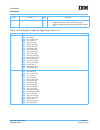

User’s manual a2 processor version 1.3 october 23, 2012 list of tables page 25 of 864 table 4-2. Shadow tlb array entry initialization .................................................................................. 158 table 5-1. Data cache array organization ........................................

Page 26

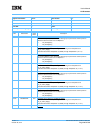

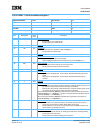

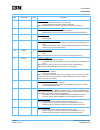

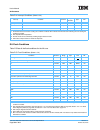

User’s manual a2 processor list of tables page 26 of 864 version 1.3 october 23, 2012 table 10-1. Pccr0[dba] (debug action) definition per thread ............................................................400 table 10-2. Debug events ....................................................................

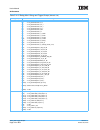

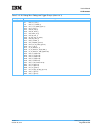

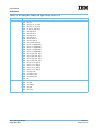

Page 27

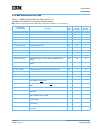

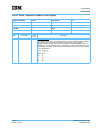

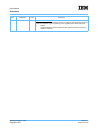

User’s manual a2 processor version 1.3 october 23, 2012 list of tables page 27 of 864 table 15-17. Ram data register high (ramdh) ...................................................................................... 726 table 15-18. Ram data register low (ramdl) .......................................

Page 28

User’s manual a2 processor list of tables page 28 of 864 version 1.3 october 23, 2012.

Page 29

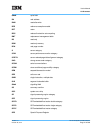

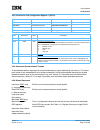

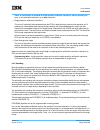

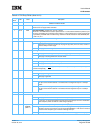

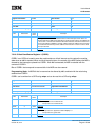

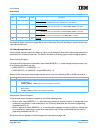

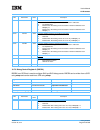

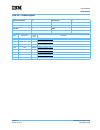

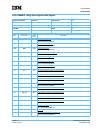

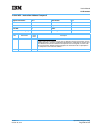

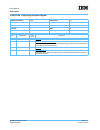

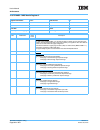

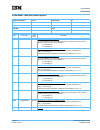

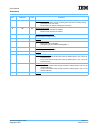

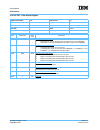

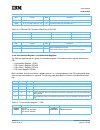

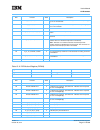

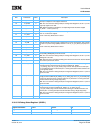

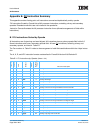

User’s manual a2 processor version 1.3 october 23, 2012 revision log page 29 of 864 revision log each release of this document supersedes all previously released versions. The revision log lists all signifi- cant changes made to the document since its initial release. In the rest of the document, ch...

Page 30

User’s manual a2 processor revision log page 30 of 864 version 1.3 october 23, 2012.

Page 31

User’s manual a2 processor version 1.3 october 23, 2012 about this book page 31 of 864 about this book this user’s manual provides the architectural overview, programming model, and detailed information about the instruction set, registers, and other facilities of the ibm® power isa a2 64-bit embedd...

Page 32

User’s manual a2 processor about this book page 32 of 864 version 1.3 october 23, 2012 • debug facilities on page 399 • performance events and event selection on page 449 • implementation dependent instructions on page 481 • power management methods on page 525 • register summary on page 529 • scom ...

Page 33

User’s manual a2 processor version 1.3 october 23, 2012 about this book page 33 of 864 • the symbol is used to describe the concatenation of two values. For example, 0b010 0b111 is the same as 0b010111. • x n means x raised to the n power. • n x means the replication of x, n times (that is, x ...

Page 34

User’s manual a2 processor about this book page 34 of 864 version 1.3 october 23, 2012.

Page 35

User’s manual a2 processor version 1.3 october 23, 2012 list of acronyms and abbreviations page 35 of 864 list of acronyms and abbreviations abist automatic built-in self test alu arithmetic logic unit ansi american national standards institute are auto-reload enable as address space atb alternate t...

Page 36

User’s manual a2 processor list of acronyms and abbreviations page 36 of 864 version 1.3 october 23, 2012 csb control status block csi context synchronizing instruction dac data address compare dba debug action dbell doorbell interrupt dcc data cache controller dch data channel dci data cache invali...

Page 37

User’s manual a2 processor version 1.3 october 23, 2012 list of acronyms and abbreviations page 37 of 864 e.Pt embedded.Page table category e.Twc embedded.Tlb write conditional category ea effective address ecc error-correcting code ecl embedded cache locking category edm external debug mode een err...

Page 38

User’s manual a2 processor list of acronyms and abbreviations page 38 of 864 version 1.3 october 23, 2012 fu floating-point unit fxu fixed-point unit g guarded gb gigabyte gb/sec gigabytes per second ghz gigahertz gpr general purpose register gs guest state htm hardware trace macro hwt hardware tabl...

Page 39

User’s manual a2 processor version 1.3 october 23, 2012 list of acronyms and abbreviations page 39 of 864 is instruction fetch address space or invalidation select isa instruction set architecture isi instruction storage interrupt iu instruction unit iu0 - iu6 instruction unit pipeline stage ivc ins...

Page 40

User’s manual a2 processor list of acronyms and abbreviations page 40 of 864 version 1.3 october 23, 2012 mas mmu assist mav mmu architecture version mb megabyte mesi modified, exclusive, shared, invalid mhz megahertz mmc memory coherence category mmu memory management unit msb most significant byte...

Page 41

User’s manual a2 processor version 1.3 october 23, 2012 list of acronyms and abbreviations page 41 of 864 qnan quiet nan ra real address raw read-after-write ree reference exception enable ret return risc reduced instruction set computing rmt replacement management table ro read only rom read-only m...

Page 42

User’s manual a2 processor list of acronyms and abbreviations page 42 of 864 version 1.3 october 23, 2012 sprn special purpose register number sprg special purpose registers general sr supervisor mode read access sram static random access memory stm stream category sw supervisor mode write access sx...

Page 43

User’s manual a2 processor version 1.3 october 23, 2012 list of acronyms and abbreviations page 43 of 864 ux underflow exception or user mode execution access v vector category v.Le little-endian category va virtual addresses vf virtualization fault vhdl very-high-speed integrated circuit (vhsic) ha...

Page 44

User’s manual a2 processor list of acronyms and abbreviations page 44 of 864 version 1.3 october 23, 2012.

Page 45

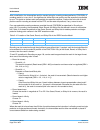

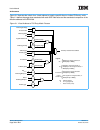

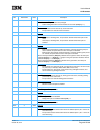

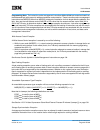

User’s manual a2 processor version 1.3 october 23, 2012 overview page 45 of 864 1. Overview the ibm power isa a2 64-bit embedded processor core is an implementation of the scalable and flexible power isa architecture. The a2 core implements four simultaneous threads of execution within the core. Eac...

Page 46

User’s manual a2 processor overview page 46 of 864 version 1.3 october 23, 2012 1.2 a2 core features the a2 core is a high-performance, low-power engine that implements the flexible and powerful power isa architecture. The a2 core contains a single-issue, in-order, pipelined processing unit, along w...

Page 47

User’s manual a2 processor version 1.3 october 23, 2012 overview page 47 of 864 • cache line locking supported • caches can be partitioned to provide separate regions for transient instructions and data • critical-word-first data access and forwarding • pseudo lru replacement policy • cache tags and...

Page 48

User’s manual a2 processor overview page 48 of 864 version 1.3 october 23, 2012 • timer facilities • 64-bit time base • decrementer with auto-reload capability • fixed interval timer (fit) • watchdog timer with critical interrupt and/or auto-reset • multiple core interfaces operating at core frequen...

Page 49

User’s manual a2 processor version 1.3 october 23, 2012 overview page 49 of 864 1.3 the a2 core as a power isa implementation the a2 core implements the full, 64-bit fixed-point power isa architecture. The a2 core fully complies with these architectural specifications. The core does not implement th...

Page 50

User’s manual a2 processor overview page 50 of 864 version 1.3 october 23, 2012 1.4.1 instruction unit the instruction unit of the a2 core fetches, decodes, and issues two instructions from different threads per cycle to any combination of the one execution pipeline and the axu interface (see sectio...

Page 51

User’s manual a2 processor version 1.3 october 23, 2012 overview page 51 of 864 1.4.2 execution unit the a2 core contains a single execution pipeline. The pipeline consists of seven stages and can access the 5-ported (three read, two write) gpr file. The pipeline handles all arithmetic, logical, bra...

Page 52

User’s manual a2 processor overview page 52 of 864 version 1.3 october 23, 2012 the dcc interfaces to the axu port to provide direct load/store access to the data cache for axu load and store operations. Such axu load and store instructions can access up to 32 bytes (a double quadword) in a single c...

Page 53

User’s manual a2 processor version 1.3 october 23, 2012 overview page 53 of 864 the establishment and replacement of tlb entries by simply not using indirect entries (that is, by using only direct ind = 0 entries). This gives system software significant flexibility in implementing a custom page repl...

Page 54

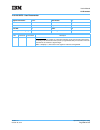

User’s manual a2 processor overview page 54 of 864 version 1.3 october 23, 2012 1.4.5 timers the a2 core contains a time base and three timers: a decrementer (dec), a fixed interval timer (fit), and a watchdog timer. The time base is a 64-bit counter that gets incremented at a frequency either equal...

Page 55

User’s manual a2 processor version 1.3 october 23, 2012 overview page 55 of 864 internal debug mode supports accessing architected processor resources, setting hardware and software breakpoints, and monitoring processor status. In internal debug mode, debug events can generate debug exceptions, whic...

Page 56

User’s manual a2 processor overview page 56 of 864 version 1.3 october 23, 2012 1.4.7.1 arithmetic and load/store pipelines the a2 core has a single execution pipeline. The pipeline handles all computational instructions and reads from and writes to the fprs, floating-point status and control regist...

Page 57

User’s manual a2 processor version 1.3 october 23, 2012 overview page 57 of 864 1.4.8.1 ieee 754 compliance ieee 754 requires a certain set of operations to be included in any implementation that claims to be compliant. Such operations can be implemented in hardware, software, or a combination of th...

Page 58

User’s manual a2 processor overview page 58 of 864 version 1.3 october 23, 2012 1.4.10.2 clock and power management interface the cpm interface supports clock distribution and power management to reduce power consumption below the normal operational level. External logic is necessary for the sleep m...

Page 59

User’s manual a2 processor version 1.3 october 23, 2012 overview page 59 of 864 an entity outside the a2 core is expected to be able to queue the s store-type operations and give a pop indi- cation to the a2 core for each as it is processed and the queue entry is available. For an entity outside the...

Page 60

User’s manual a2 processor overview page 60 of 864 version 1.3 october 23, 2012.

Page 61

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 61 of 864 2. Cpu programming model the programming model of the a2 core describes how the following features and operations of the core appear to programmers: • logical partitioning on page 61 • storage addressing on ...

Page 62

User’s manual a2 processor cpu programming model page 62 of 864 version 1.3 october 23, 2012 a processor is assigned to one partition at any given time. A processor can be assigned to any given partition without consideration of the physical configuration of the system (for example, shared registers...

Page 63

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 63 of 864 the alignment of the operand effective address of some storage access instructions might affect perfor- mance; in some cases, it might cause an alignment exception to occur. For such storage access instructi...

Page 64

User’s manual a2 processor cpu programming model page 64 of 864 version 1.3 october 23, 2012 cache management instructions access cache block operands; for the a2 core, the cache block size is 64 bytes. However, the effective addresses calculated by cache management instructions are not required to ...

Page 65

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 65 of 864 2.2.2.1 data storage addressing modes there are two data storage addressing modes supported by the a2 core: • base + displacement (d-mode) addressing mode: the 16-bit d field is sign-extended and added to th...

Page 66

User’s manual a2 processor cpu programming model page 66 of 864 version 1.3 october 23, 2012 2.2.3 byte ordering if scalars (individual data items and instructions) were indivisible, there would be no such concept as “byte ordering.” it is meaningless to consider the order of bits or groups of bits ...

Page 67

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 67 of 864 short e; /* 0x5152 halfword */ int f; /* 0x6162_6364 word */ } s; c structure mapping rules permit the use of padding (skipped bytes) to align scalars on desirable boundaries. The following structure mapping...

Page 68

User’s manual a2 processor cpu programming model page 68 of 864 version 1.3 october 23, 2012 consider the big-endian mapping of instruction p at address 0x00, where, for example, p = add r7, r7, r4: on the other hand, in a little-endian mapping the same instruction is arranged with the least-signifi...

Page 69

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 69 of 864 • for byte loads and stores, including strings, no reordering of bytes occurs regardless of byte ordering. • for halfword loads and stores, bytes are reversed within the halfword for one byte order with resp...

Page 70

User’s manual a2 processor cpu programming model page 70 of 864 version 1.3 october 23, 2012 2.3 multithreading the a2 core has four threads that allow simultaneous execution within the processor and can be viewed as a 4-way multiprocessor with shared dataflow. This gives the effective appearance of...

Page 71

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 71 of 864 2.3.1.3 guest processor identification register (gpir) the gpir is a register that identifies a specific instance of a processor thread for the guest operating system. The gpir is used to filter incoming pro...

Page 72

User’s manual a2 processor cpu programming model page 72 of 864 version 1.3 october 23, 2012 2.3.2.3 core configuration register 0 (ccr0) the ccr0 is used to disable or enable threads. When a thread is disabled by setting the ccr0 bit corre- sponding to the thread to 0, all instructions that have be...

Page 73

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 73 of 864 the ten is accessed by using two registers: tens and tenc. When tens is written, threads for which the corresponding bit in tens is 1 are enabled; threads for which the corresponding bit in tens is 0 are una...

Page 74

User’s manual a2 processor cpu programming model page 74 of 864 version 1.3 october 23, 2012 2.3.3 wake on interrupt the a2 core can be configured to wake on interrupts or other conditions, if the thread was disabled by a write to ccr0 or by executing a wait instruction. 2.3.3.1 core configuration r...

Page 75

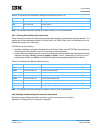

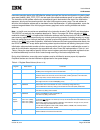

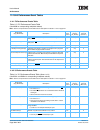

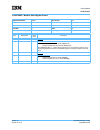

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 75 of 864 2.3.4 thread priority thread priority can be changed by writing the ppr32 register, executing an or rx,rx,rx instruction, or by causing an interrupt. 2.3.4.1 program priority register (ppr32) the program pri...

Page 76

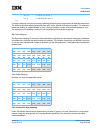

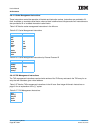

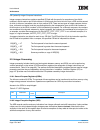

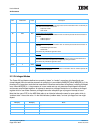

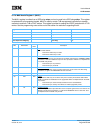

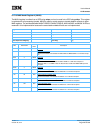

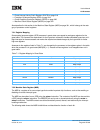

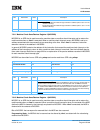

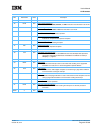

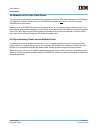

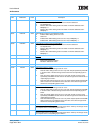

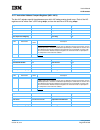

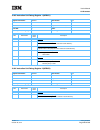

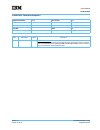

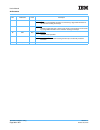

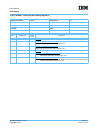

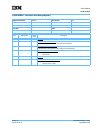

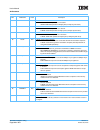

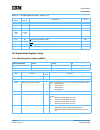

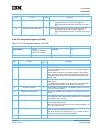

User’s manual a2 processor cpu programming model page 76 of 864 version 1.3 october 23, 2012 table 2-5. Program priority register (ppr32) table 2-3. Priority levels rx ppr32[pri] isa priority a2 hardware priority with iucr1[hipri] setting privileged 00 01 10 11 31 001 very low a2low a2low a2low a2lo...

Page 77

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 77 of 864 2.3.4.2 instruction unit configuration register 1 (iucr1) 2.3.5 resources shared between threads all architected states are duplicated for each thread except for logical partitioning and memory. This allows ...

Page 78

User’s manual a2 processor cpu programming model page 78 of 864 version 1.3 october 23, 2012 2.3.6.1 accessing shared resources when software executing in thread t n writes a new value in an spr (mtspr) that is shared with other threads, either of the following sequences of operations can be perform...

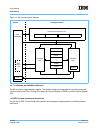

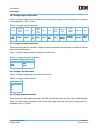

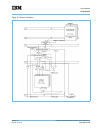

Page 79

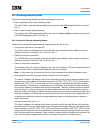

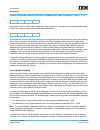

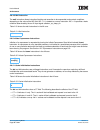

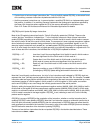

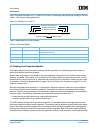

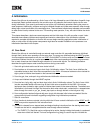

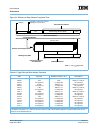

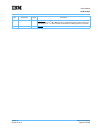

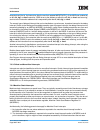

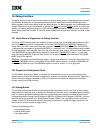

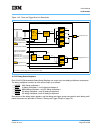

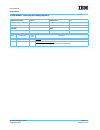

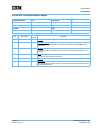

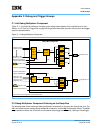

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 79 of 864 2.3.8 pipeline sharing figure 2-1 shows the instruction flow for the a2 core. Figure 2-1. A2 core instruction unit.

Page 80

User’s manual a2 processor cpu programming model page 80 of 864 version 1.3 october 23, 2012 2.3.8.1 instruction cache the instruction cache is a shared resource between all threads where a single thread can be selected each cycle dependent upon the number of instructions currently contained within ...

Page 81

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 81 of 864 . 2.3.8.4 ram unit the ram unit allows an external command to be issued within a given thread’s instruction stream. This unit is a shared resource within a core in that only one thread can issue a ram comman...

Page 82

User’s manual a2 processor cpu programming model page 82 of 864 version 1.3 october 23, 2012 2.3.8.5 microcode unit the microcode unit (ucode) is partially shared and partially duplicated logic. The rom that contains the actual stream of instructions to be issued is a shared unit; however, each thre...

Page 83

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 83 of 864 perform the initial write to a register with reserved fields set to 0, and to perform all subsequent writes to the register using a read-modify-write strategy: read the register; use logical instructions to ...

Page 84

User’s manual a2 processor cpu programming model page 84 of 864 version 1.3 october 23, 2012 2.4.1 register mapping some special purpose register (spr) accesses in guest state are mapped to analogous registers for the guest state. This removes the requirement for the hypervisor software to handle em...

Page 85

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 85 of 864 sprs control the use of the debug facilities, timers, interrupts, memory management, caches, and other architected processor resources. Table 14-1 on page 530 shows the mnemonic, name, and number for each sp...

Page 86

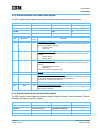

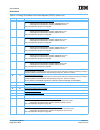

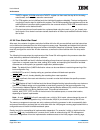

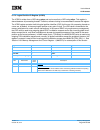

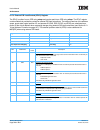

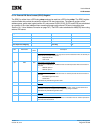

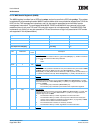

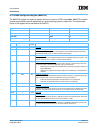

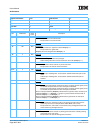

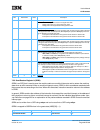

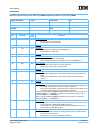

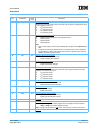

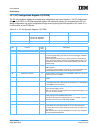

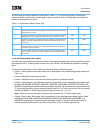

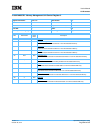

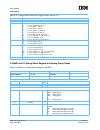

User’s manual a2 processor cpu programming model page 86 of 864 version 1.3 october 23, 2012 2.6 instruction categories the power isa defines that each facility (including registers and fields therein) and instruction is in exactly one category. Table 2-7 indicate the categories that are implemented...

Page 87

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 87 of 864 2.7 instruction classes power isa architecture defines all instructions as falling into exactly one of the following three classes, as determined by the primary opcode (and the extended opcode, if any): 1. D...

Page 88

User’s manual a2 processor cpu programming model page 88 of 864 version 1.3 october 23, 2012 • perform the actions described in the rest of this document, if the instruction is recognized and supported by the implementation. The architected behavior might cause other exceptions. The a2 core recogniz...

Page 89

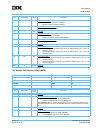

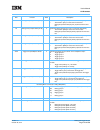

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 89 of 864 table 2-8 summarizes the a2 core instruction set by category. Instructions within each category are described in subsequent sections. 2.8.1 integer instructions integer instructions transfer data between mem...

Page 90

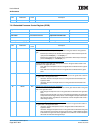

User’s manual a2 processor cpu programming model page 90 of 864 version 1.3 october 23, 2012 table 2-11 shows how operands are handled depending on alignment. Optimal performance and configura- tion is achieved when operands are aligned. Table 2-9. Integer storage access instructions loads stores by...

Page 91

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 91 of 864 2.8.1.2 integer arithmetic instructions arithmetic operations are performed on integer or ordinal operands stored in registers. Instructions that perform operations on two operands are defined in a 3-operand...

Page 92

User’s manual a2 processor cpu programming model page 92 of 864 version 1.3 october 23, 2012 2.8.1.3 integer logical instructions table 2-13 lists the integer logical instructions in the a2 core. See integer arithmetic instructions on page 91 for an explanation of the “[.]” syntax. 2.8.1.4 integer c...

Page 93

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 93 of 864 2.8.1.7 integer shift instructions table 2-17 lists the integer shift instructions in the a2 core. Note that the shift right algebraic instructions implicitly update the xer[ca] field. See integer arithmetic...

Page 94

User’s manual a2 processor cpu programming model page 94 of 864 version 1.3 october 23, 2012 2.8.2 branch instructions these instructions unconditionally or conditionally branch to an address. Conditional branch instructions can test condition codes set in the cr by a previous instruction and branch...

Page 95

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 95 of 864 2.8.3.2 register management instructions these instructions move data between the gprs and control registers in the a2 core. Table 2-22 lists the register management instructions in the a2 core. 2.8.3.3 syst...

Page 96

User’s manual a2 processor cpu programming model page 96 of 864 version 1.3 october 23, 2012 2.8.4.1 cache management instructions these instructions control the operation of the data and instruction caches. Instructions are provided to fill, flush, invalidate, or zero data cache blocks, where a blo...

Page 97

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 97 of 864 2.8.4.3 processor synchronization instruction the processor synchronization instruction, isync, forces the processor to complete all instructions preceding the isync before allowing any context changes as a ...

Page 98

User’s manual a2 processor cpu programming model page 98 of 864 version 1.3 october 23, 2012 2.8.4.6 wait instruction the wait instruction allows instruction fetching and execution to be suspended under certain conditions, depending on the value of the wc field. Wc = 11 is treated as a no-op instruc...

Page 99

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 99 of 864 2.9 branch processing the four branch instructions provided by a2 core are summarized in table 2.8.2 on page 94. The following sections provide additional information about branch addressing, instruction fie...

Page 100

User’s manual a2 processor cpu programming model page 100 of 864 version 1.3 october 23, 2012 the “a” and “t” bits of the bo field can be used by software to provide a hint about whether the branch is likely to be taken or is likely not to be taken, as shown in table 2-35. This implementation has dy...

Page 101

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 101 of 864 ultimately, the branch decoder generates four flags that will be used by the branch predictor at a later stage. These bits are appended to the original 32-bit instruction and are carried along as part of th...

Page 102

User’s manual a2 processor cpu programming model page 102 of 864 version 1.3 october 23, 2012 dynamic prediction begins when a valid instruction initiates a read access to the bht in iu0. The bht is indexed based on the current instruction ifar, and returns a 2-bit history value for that instruction...

Page 103

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 103 of 864 the effect could be minimized by increasing the depth of the bht (and the number of ifar bits used), but with an ifar that is potentially 62 bits long, aliasing can never be eliminated entirely. A depth of ...

Page 104

User’s manual a2 processor cpu programming model page 104 of 864 version 1.3 october 23, 2012 2.9.4.3 branch prioritization after all valid branch instructions within a cache line have been evaluated, they are prioritized in the order they occur. The first branch within a cache line to be evaluated ...

Page 105

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 105 of 864 shadow pointer. The shadow pointer becomes valid for predictions at this point because all branch instruc- tions that have not yet been resolved by the execution unit will be flushed with the rest of the pi...

Page 106

User’s manual a2 processor cpu programming model page 106 of 864 version 1.3 october 23, 2012 instruction). Thus, the lr contents can be used as a return address for a subroutine that was entered using a link update form of branch. The bclr instruction uses the lr in this fashion, enabling indirect ...

Page 107

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 107 of 864 2.9.5.3 condition register (cr) the cr is used to record certain information (“conditions”) related to the results of the various instructions that are enabled to update the cr. A bit in the cr can also be ...

Page 108

User’s manual a2 processor cpu programming model page 108 of 864 version 1.3 october 23, 2012 to summarize, the cr can be accessed in any of the following ways: • mfcr reads the cr into a gpr. Note that this instruction does not update the cr and is therefore not listed in table 2-36. • conditional ...

Page 109

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 109 of 864 • certain forms of various integer instructions (the “.” forms) implicitly update cr[cr0], as do certain forms of the auxiliary processor instructions implemented within the a2 core. • auxiliary processor i...

Page 110

User’s manual a2 processor cpu programming model page 110 of 864 version 1.3 october 23, 2012 cr update by integer compare instructions integer compare instructions update a specified cr field with the result of a comparison of two 64-bit numbers in 64-bit mode or two 32-bit numbers in 32-bit mode, ...

Page 111

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 111 of 864 the following table illustrates the fields of the xer, while table 2-38 and table 2-39 list the instructions that update xer[so,ov] and the xer[ca] fields, respectively. The sections that follow the figure ...

Page 112

User’s manual a2 processor cpu programming model page 112 of 864 version 1.3 october 23, 2012 2.10.2.1 summary overflow (so) field this field is set to 1 when an instruction is executed that causes xer[ov] to be set to 1, except for the case of mtspr(xer), which writes xer[so,ov] with the values in ...

Page 113

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 113 of 864 2.10.2.4 transfer byte count (tbc) field the tbc field is used by the string indexed integer storage access instructions (lswx and stswx) as a byte count. The tbc field is also written by mtspr(xer) with th...

Page 114

User’s manual a2 processor cpu programming model page 114 of 864 version 1.3 october 23, 2012 2.11.1 special purpose registers general (sprg0–sprg8) sprg0 through sprg8 are provided for general purpose, system-dependent software use. One common system usage of these registers is as temporary storage...

Page 115

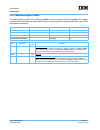

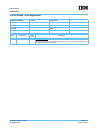

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 115 of 864 table 2-42. Sprg2 register table 2-43. Sprg3 register table 2-44. Sprg4 register register short name: sprg2 read access: priv decimal spr number: 274 write access: priv initial value: 0x0000000000000000 dup...

Page 116

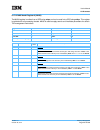

User’s manual a2 processor cpu programming model page 116 of 864 version 1.3 october 23, 2012 table 2-45. Sprg5 register table 2-46. Sprg6 register table 2-47. Sprg7 register register short name: sprg5 read access: priv/any decimal spr number: 277/261 write access: priv/none initial value: 0x0000000...

Page 117

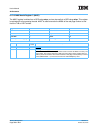

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 117 of 864 table 2-48. Sprg8 register table 2-49. Gsprg0 register table 2-50. Gsprg1 register register short name: sprg8 read access: hypv decimal spr number: 604 write access: hypv initial value: 0x0000000000000000 d...

Page 118

User’s manual a2 processor cpu programming model page 118 of 864 version 1.3 october 23, 2012 table 2-51. Gsprg2 register table 2-52. Gsprg3 register register short name: gsprg2 read access: priv decimal spr number: 370 write access: priv initial value: 0x0000000000000000 duplicated for multithread:...

Page 119

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 119 of 864 2.11.2 external process id load context (eplc) register the eplc register contains fields to provide the context for external process id load instructions. 2.11.3 external process id store context (epsc) re...

Page 120

User’s manual a2 processor cpu programming model page 120 of 864 version 1.3 october 23, 2012 2.12 privileged modes the power isa architecture defines two operating “states” or “modes”: supervisor (privileged) and user (nonprivileged). Which mode the processor is operating in is controlled by msr[pr...

Page 121

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 121 of 864 2.12.1 privileged instructions an instruction that is hypervisor privileged must be in the hypervisor state (msr[gs,pr] = 0b00) to success- fully execute. If executed from guest privileged state (msr[gs,pr]...

Page 122

User’s manual a2 processor cpu programming model page 122 of 864 version 1.3 october 23, 2012 endif else // msrp[uclep]=0 or msr[gs] = 0 if msr[pr]=1 and msr[ucle]=0 cache locking type data storage interrupt endif end 2.12.2 privileged sprs most sprs are privileged. The only defined nonprivileged sp...

Page 123

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 123 of 864 under certain circumstances, it is necessary for the hardware or software to force the synchronization of a program’s context. Context synchronizing operations include all interrupts except machine check, a...

Page 124

User’s manual a2 processor cpu programming model page 124 of 864 version 1.3 october 23, 2012 iac event is recognized on the execution of this instruction; without the isync, the xyz instruction might be prefetched and dispatched to execution before recog- nizing that the iac event has been enabled....

Page 125

User’s manual a2 processor version 1.3 october 23, 2012 cpu programming model page 125 of 864 in this example, the mtdcr is reconfiguring the i/o device in a manner that would cause the preceding store instruction to fail, were the mtdcr to change the device before the completion of the store. Becau...

Page 126

User’s manual a2 processor cpu programming model page 126 of 864 version 1.3 october 23, 2012 2.15.2.1 l1 d-cache four bits are added per cache block, representing the set of watches that exist for that block corresponding to each thread. If not already available, the a2 core needs to provide a thre...

Page 127

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 127 of 864 3. Fu programming model the programming model of the a2 core describes how the following features and operations appear to programmers: • storage addressing, including storage operands, effective address cal...

Page 128

User’s manual a2 processor fu programming model page 128 of 864 version 1.3 october 23, 2012 the alignment of the operand effective address of some storage access instructions can affect performance and in some cases can cause an alignment exception to occur. For such storage access instructions, th...

Page 129

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 129 of 864 3.2 floating-point exceptions each floating-point exception, and each category of invalid operation exception, is associated with an excep- tion bit in the fpscr. The following floating-point exceptions are ...

Page 130

User’s manual a2 processor fu programming model page 130 of 864 version 1.3 october 23, 2012 3.3.1 register types the a2 core core provides two types of registers, floating-point registers (fprs) and the fpscr. Each type is characterized by the instructions used to read and write the registers. The ...

Page 131

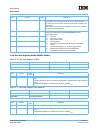

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 131 of 864 3.3.1.2 floating-point status and control register (fpscr) the fpscr controls the handling of floating-point exceptions and records status resulting from the floating- point operations. Table 3-4. Floating-p...

Page 132

User’s manual a2 processor fu programming model page 132 of 864 version 1.3 october 23, 2012 39 vxsnan floating-point invalid operation exception (snan) 0 a floating-point invalid operation exception (vxsnan) did not occur. 1 a floating-point invalid operation exception (vxsnan) occurred. See invali...

Page 133

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 133 of 864 programming note: all floating-point operations conform to the ieee standard. All floating-point operations produce the same results regardless of the value of ieee mode (ni) bit. 3.4 floating-point data for...

Page 134

User’s manual a2 processor fu programming model page 134 of 864 version 1.3 october 23, 2012 load single instruction, it is converted to double format and placed in the target fpr. Conversely, a floating- point value stored from an fpr into storage using a store single instruction is converted to si...

Page 135

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 135 of 864 the fprs support the floating-point double format only. The numeric and nonnumeric values representable within each of the two supported formats are approxima- tions to the real numbers and include the norma...

Page 136

User’s manual a2 processor fu programming model page 136 of 864 version 1.3 october 23, 2012 3.4.2.2 denormalized numbers denormalized numbers (±den) are values that have a biased exponent value of zero and a nonzero fraction value. They are nonzero numbers smaller in magnitude than the representabl...

Page 137

29 0 else fpr(frt) fpr(frb) else if fpr(frc) is a nan then fpr(frt) fp...

Page 138

User’s manual a2 processor fu programming model page 138 of 864 version 1.3 october 23, 2012 3.4.5 normalization and denormalization • the intermediate result of an arithmetic or frsp instruction might require normalization and/or denormal- ization. Normalization and denormalization do not affect th...

Page 139

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 139 of 864 ments, or used directly as operands for single-precision arithmetic instructions, without preceding the store, or the arithmetic instruction, by an frsp instruction. • single-precision arithmetic instruction...

Page 140

User’s manual a2 processor fu programming model page 140 of 864 version 1.3 october 23, 2012 figure 3-2 shows the relation of z, z1, and z2 in this case. The following rules specify the rounding in the four modes. “lsb” means “least-significant bit.” table 3-9 describes the rounding modes. 3.5 float...

Page 141

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 141 of 864 arithmetic instructions require all operands to be single-precision. Double-precision arithmetic instructions produce double-precision values, while single-precision arithmetic instructions produce single-pr...

Page 142

User’s manual a2 processor fu programming model page 142 of 864 version 1.3 october 23, 2012 after normalization, the intermediate result is rounded using the rounding mode specified by fpscr[rn]. If rounding results in a carry into c, the significand is shifted right one position and the exponent i...

Page 143

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 143 of 864 3.5.2 execution model for multiply-add type instructions the a2 core provides a special form of instruction that performs up to three operations in one instruction (a multiplication, an addition, and a negat...

Page 144

User’s manual a2 processor fu programming model page 144 of 864 version 1.3 october 23, 2012 the single-precision instructions for which there is a corresponding double-precision instruction have the same format and extended opcode as the corresponding double-precision instruction. Instructions are ...

Page 145

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 145 of 864 for consistency, to reduce the likelihood of causing a serious malfunction due to user error, and to enable random testing, single-precision operations are performed on double-precision operands. For all cas...

Page 146

29 0 for double-precision load f...

Page 147

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 147 of 864 no denormalization required (includes zero / infinity / nan) if fpr(frs) 1:11 > 896 or fpr(frs) 1:63 = 0 then word 0:1 fpr(frs) 0:1 word 2:31 fpr(frs) 5:34 denormalization required if 874 frs 1:11 89...

Page 148

User’s manual a2 processor fu programming model page 148 of 864 version 1.3 october 23, 2012 note: for complete instruction descriptions, see the power isa v2.06 specification. 3.6.4 floating-point move instructions these instructions copy data from one floating-point register to another, altering t...

Page 149

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 149 of 864 note: for complete instruction descriptions, see the power isa v2.06 specification. 3.6.5.1 floating-point multiply-add instructions these instructions combine a multiply and an add operation without an inte...

Page 150

User’s manual a2 processor fu programming model page 150 of 864 version 1.3 october 23, 2012 note: for complete instruction descriptions, see the power isa v2.06 specification. 3.6.7 floating-point compare instructions the floating-point compare instructions compare the contents of two floating-poin...

Page 151

User’s manual a2 processor version 1.3 october 23, 2012 fu programming model page 151 of 864 note: for complete instruction descriptions, see the power isa v2.06 specification. 3.6.8 floating-point status and control register instructions every floating-point status and control register instruction ...

Page 152

User’s manual a2 processor fu programming model page 152 of 864 version 1.3 october 23, 2012.

Page 153

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 153 of 864 4. Initialization reset of the a2 core is performed by a flush 0 scan of all rings followed by scan initialization of specific rings as required. Reset controls external to the core drive scan ring selection and c...

Page 154

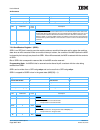

User’s manual a2 processor initialization page 154 of 864 version 1.3 october 23, 2012 thrctl register. A scom write to the thrctl register can then reset the stop bit for the desig- nated thread, and instruction execution commences. B. The ten register can be initialized such that individual thread...

Page 155

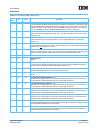

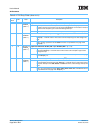

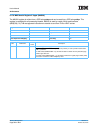

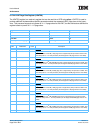

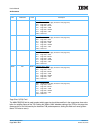

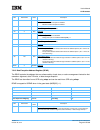

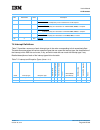

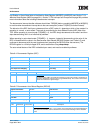

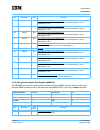

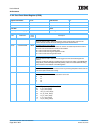

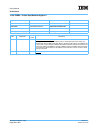

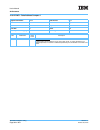

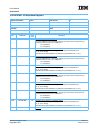

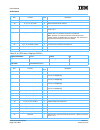

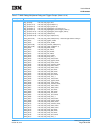

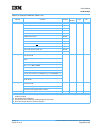

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 155 of 864 instruction execution starts at the iar effective address scanned into the boot configuration ring during hard- ware reset (0x0000_0000_ffff_fffc, the last word of the effective address space, or some other locati...

Page 156

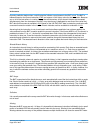

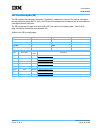

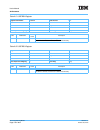

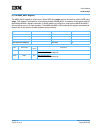

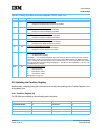

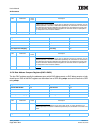

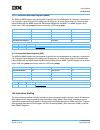

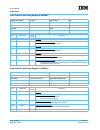

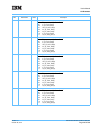

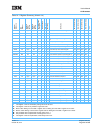

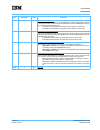

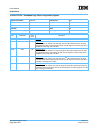

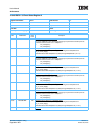

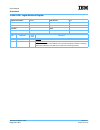

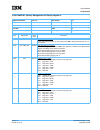

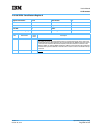

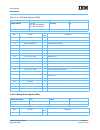

User’s manual a2 processor initialization page 156 of 864 version 1.3 october 23, 2012 iucr0 0x000010fa default reset value can be altered via a scan of the boot configuration ring. Initializes the various branch prediction options. Iucr1 0x00001000 default reset value can be altered via a scan of t...

Page 157

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 157 of 864 xucr0 0x000708c0 default reset value can be altered via a scan of the boot configuration ring. Initializes various xu control parameter fields. Xucr1 0x00000000 default reset value can be altered via a scan of the...

Page 158

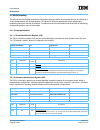

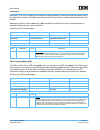

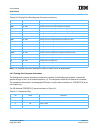

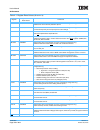

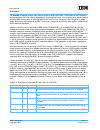

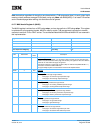

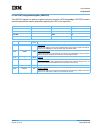

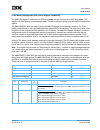

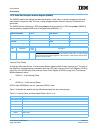

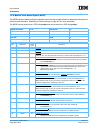

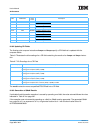

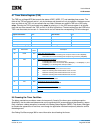

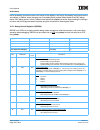

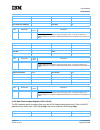

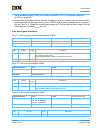

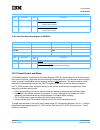

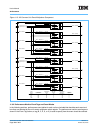

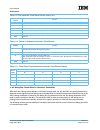

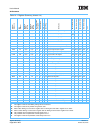

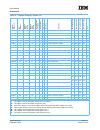

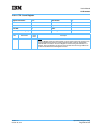

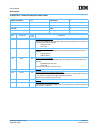

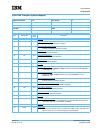

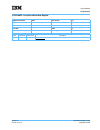

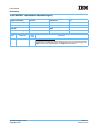

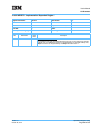

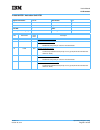

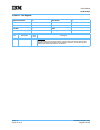

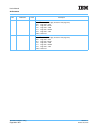

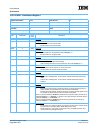

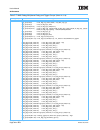

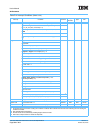

User’s manual a2 processor initialization page 158 of 864 version 1.3 october 23, 2012 table 4-2. Shadow tlb array entry initialization (sheet 1 of 3) resource field reset value comment tlbentry[1] 1 epn 0:51 system-dependent c. Reset value is specified by the boot configuration ring. X 0 exclusion ...

Page 159

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 159 of 864 tlbentry[2] 2 epn 0:51 0x0000000000000 effective page number (matches ivpr(0:51) reset value). X 0 exclusion range enable bit (disabled). Size 0b0001 page size selection (set to 4 kb). This field is recoded to a 3...

Page 160

User’s manual a2 processor initialization page 160 of 864 version 1.3 october 23, 2012 4.3 software initiated reset requests the power isa book iii-e defines two sets of facilities that can be used by software to request a reset: debug and the watchdog timer. Whether or not these facilities are used...

Page 161

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 161 of 864 because the reset request logic is implemented in multiple thread-specific sources, it is possible that more than one reset request output signal can be active at the same time. Software should coordinate the use ...

Page 162

User’s manual a2 processor initialization page 162 of 864 version 1.3 october 23, 2012 the an_ac_reset_x_complete inputs must be active for a minimum of one clock pulse to set the dbsr[mrr] and tsr[wrs] reset status bits. If more than one reset input is active at the same time, they are set using th...

Page 163

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 163 of 864 4.4 initialization software requirements after a reset operation occurs, the a2 core is initialized to a minimum configuration to enable the fetching and execution of the software initialization code and to guaran...

Page 164

User’s manual a2 processor initialization page 164 of 864 version 1.3 october 23, 2012 2. Invalidate the instruction cache (ici). 3. Invalidate the data cache (dci). 4. Synchronize memory accesses (msync). This step forces any data operations that might have been in progress before the reset operati...

Page 165

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 165 of 864 • specify the invalidation class for the entry (can be used by subsequent erativax instructions). • disable the exclusion range function (x = 0); otherwise, one or more tlb entries must be config- ured to fit with...

Page 166

User’s manual a2 processor initialization page 166 of 864 version 1.3 october 23, 2012 • use rfi if changing the msr to match the new ts field of the tlb entry. (srr1 will be copied into the msr, and program execution will resume at the value in srr0.) • use rfi if changing the next instruction fetc...

Page 167

User’s manual a2 processor version 1.3 october 23, 2012 initialization page 167 of 864 • disable the exclusion range function (x = 0); otherwise, one or more erat entries needs to be configured to fit within the exclusion range. 9. Initialize interrupt resources. A. Initialize ivpr and givpr to spec...

Page 168

User’s manual a2 processor initialization page 168 of 864 version 1.3 october 23, 2012 13. Initialize the msr to enable interrupts as desired. A. Set msr[ce] to enable or disable critical input, watchdog timer, guest processor doorbell critical, and processor doorbell critical interrupts. B. Set msr...

Page 169

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 169 of 864 5. Instruction and data caches the a2 core provides separate instruction and data cache controllers and arrays, which allow concurrent access and minimize pipeline stalls. The storage capacity of the ...

Page 170

User’s manual a2 processor instruction and data caches page 170 of 864 version 1.3 october 23, 2012 5.2 instruction cache array organization and operation the instruction is 4-way set-associative, with 64 sets and a 64-byte line size. Table 5-3 illustrates generically the ways and sets of the cache ...

Page 171

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 171 of 864 the icc provides a speculative prefetch mechanism that automatically prefetches up to one line per thread upon any fetch request that misses in the instruction cache. The icc also handles the executio...

Page 172

User’s manual a2 processor instruction and data caches page 172 of 864 version 1.3 october 23, 2012 cache or within memory itself, by the a2 core through the execution of store instructions or by some other mechanism in the system writing to memory, software must use cache management instructions to...

Page 173

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 173 of 864 5.4.3.2 instruction cache parity operations the instruction cache contains parity bits to protect against soft data errors. Both the instruction tags and data are protected. Instruction cache lines co...

Page 174

User’s manual a2 processor instruction and data caches page 174 of 864 version 1.3 october 23, 2012 extensive load, store, and flush queues are also provided, such that up to eight outstanding load misses with the dcc continuing to service subsequent load and store hits in an in-order fashion. The r...

Page 175

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 175 of 864 software must make sure that no lines from that page remain valid in the data cache (typically by using the dcbf instruction) before attempting to access the (now caching inhibited) page with load, st...

Page 176

User’s manual a2 processor instruction and data caches page 176 of 864 version 1.3 october 23, 2012 (of only accessing the requested bytes) is only architecturally required when the guarded storage attribute is also set, but the dcc enforces this requirement on any load to a caching inhibited memory...

Page 177

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 177 of 864 • 16-byte write request (any byte address 0–16 within a double quadword) only possible due to an axu quadword store. • 32-byte write request (must be to byte address 0 of a double quadword) only possi...

Page 178

User’s manual a2 processor instruction and data caches page 178 of 864 version 1.3 october 23, 2012 section 2.12.1 privileged instructions on page 121 summarizes which data cache management instructions are privileged. The following instructions are used by software to manage the data cache. 5.5.3.2...

Page 179

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 179 of 864 the dcbt instruction can also be used as a convenient mechanism for setting up a fixed, known environment within the data cache. This is useful for deterministic performance on a particular sequence o...

Page 180

User’s manual a2 processor instruction and data caches page 180 of 864 version 1.3 october 23, 2012 • ct = 0 indicates l1 only. Note that icbtls ct = 0 is treated the same as icbt ct = 0 because instruction cache locking/unlocking is not supported. • ct = 2 indicates l2 only. The cache line is not p...

Page 181

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 181 of 864 4. Execute an rfi. If the locking instruction is a clear lock instruction, to unlock the line, the handler should do the following: 1. Remove the line address from its list of locked lines. 2. Execute...

Page 182

User’s manual a2 processor instruction and data caches page 182 of 864 version 1.3 october 23, 2012 instructions: notes: • in the l1 data cache, the a2 implements a lock bit for every index and way, allowing a line locking granu- larity. Setting ct = 0 specifies the l1 cache. • the a2 supports ct = ...

Page 183

User’s manual a2 processor version 1.3 october 23, 2012 instruction and data caches page 183 of 864 the a2 implements a flash clear for all data cache lock bits (using xucr0[clfc]). This allows system soft- ware to clear all data cache locking bits without knowing the addresses of the lines locked. ...

Page 184

User’s manual a2 processor instruction and data caches page 184 of 864 version 1.3 october 23, 2012 are treated as misses and do not update the contents of the directory, and back-invalidates from the l2 do not invalidate any cache lines. A dci instruction does however invalidate the entire data cac...

Page 185

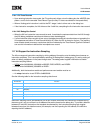

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 185 of 864 6. Memory management the a2 core supports a uniform, 2 64 bytes (64 bits) effective address (ea) space and a 4 tb (42-bit) real address (ra) space. The a2 memory management unit (mmu) performs address translati...

Page 186

User’s manual a2 processor memory management page 186 of 864 version 1.3 october 23, 2012 the tlb is parity protected against soft errors. The details of parity checking are described in the following sections. 6.1.1 support for power isa mmu architecture the a2 memory management unit is based on po...

Page 187

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 187 of 864 6.2.1 virtual address formation the first step in page identification is the expansion of the effective address into a virtual address. Again, the effective address is the 64-bit address calculated by a load, s...

Page 188

User’s manual a2 processor memory management page 188 of 864 version 1.3 october 23, 2012 by convention, application-level code runs with msr[is,ds] set to 1 and uses corresponding tlb entries with the ts = 1. Conversely, system-level code runs with msr[is,ds] set to 0 and uses corresponding tlb ent...

Page 189

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 189 of 864 8. Not all of the address space defined by the hole needs to be mapped by other entries. 9. Pages mapped in the hole must be page-size aligned. 10. Pages mapped in the hole must not overlap. 11. Pages mapped in...

Page 190

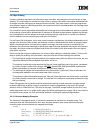

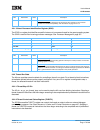

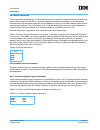

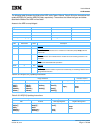

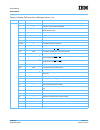

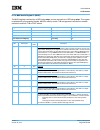

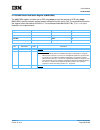

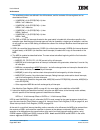

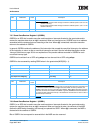

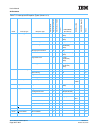

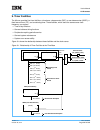

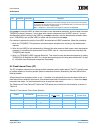

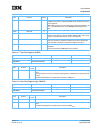

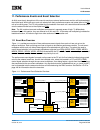

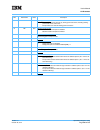

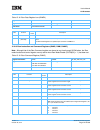

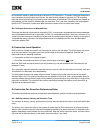

User’s manual a2 processor memory management page 190 of 864 version 1.3 october 23, 2012 figure 6-1 illustrates the criteria for a virtual address to match a specific direct or indirect tlb entry, while table 6-1 defines the page sizes associated with each size field value and the associated compar...

Page 191

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 191 of 864 6.3 address translation after a direct (ind = 0) tlb entry is found that matches the virtual address associated with a given storage access, as described in section 6.2 page identification on page 186, the virt...

Page 192

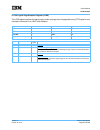

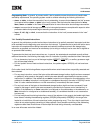

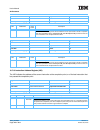

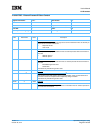

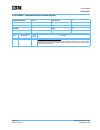

User’s manual a2 processor memory management page 192 of 864 version 1.3 october 23, 2012 figure 6-2. Effective-to-real address translation flow table 6-2. Page size and real address formation size 1 page size rpn bits required to be 0 real address 0b0000 0b0001 0b0010 0b0011 0b0100 0b0101 0b0110 0b...

Page 193

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 193 of 864 6.4 access control after a matching tlb entry has been identified and the address has been translated, the access control mechanism determines whether the program has execute, read, and/or write access to the p...

Page 194

User’s manual a2 processor memory management page 194 of 864 version 1.3 october 23, 2012 6.4.3 read access the user state read enable (ur) or supervisor state read enable (sr) bit of a tlb entry controls read access to a page, depending on the operating mode (user or supervisor) of the processor. •...

Page 195

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 195 of 864 6.5 storage attributes each tlb entry specifies a number of storage attributes for the memory page with which it is associated. Storage attributes affect the manner in which storage accesses to a given page are...

Page 196

User’s manual a2 processor memory management page 196 of 864 version 1.3 october 23, 2012 6.5.1 write-through (w) the a2 core data cache ignores the write-through attribute. The data for all store operations is written to memory, as opposed to only being written into the data cache. If the reference...

Page 197

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 197 of 864 a data access to a guarded storage location is performed only if either the access is caused by an instruction that is known to be required by the sequential execution model, or the access is a load and the sto...

Page 198

User’s manual a2 processor memory management page 198 of 864 version 1.3 october 23, 2012 • the m bits do not need to match on all pages; however, it is then software’s responsibility to maintain data coherency. 2. If the multiple pages exist on multiple processors, then: • the i bits do not need to...

Page 199

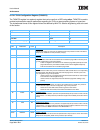

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 199 of 864 each tlb entry identifies a page and defines its translation, access controls, and storage attributes. Accord- ingly, fields in the tlb entry fall into four categories: • page identification fields (information...

Page 200

User’s manual a2 processor memory management page 200 of 864 version 1.3 october 23, 2012 0 67 ts translation address space (1 bit) this bit indicates the address space with which this tlb entry is associated. For instruction storage accesses, msr[is] must match the value of ts in the tlb entry for ...

Page 201

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 201 of 864 address translation fields 1 18:21 - reserved (4 bits) reserved for real page number extension. 1 22:51 rpn 9 real page number (variable size, from 18 - 30 bits) bits 22:n–1 of the rpn field are used to replace...

Page 202

User’s manual a2 processor memory management page 202 of 864 version 1.3 october 23, 2012 1 59 sx (ind = 0) spsize 1 (ind = 1) supervisor state execute enable (ind = 0) or spsize 1 (ind = 1) 9 (1 bit) 0 (ind = 0) instruction fetch is not permitted from this page while msr[pr] = 0, and the attempt to...

Page 203

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 203 of 864 6.7 effective to real address translation arrays the a2 core implements two fully-associative effective to real address translation (erat) arrays also called shadow tlb arrays): one for instruction fetches and ...

Page 204

User’s manual a2 processor memory management page 204 of 864 version 1.3 october 23, 2012 lookup finds no direct entries, but does find an indirect entry (ind = 1), then the address is forwarded to the hardware page table walker for page table lookup. If the address also misses the indirect entry lo...

Page 205

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 205 of 864 eratilx instructions. By invalidating the erat arrays, a context-altering instruction forces the hardware to refresh the erat entries with the updated information in the utlb as each memory page is accessed (wh...

Page 206

User’s manual a2 processor memory management page 206 of 864 version 1.3 october 23, 2012 occur in mmu mode. The erat lru index number is incremented (the mod number of entries below the watermark is described section 6.7.5) in a round-robin fashion each time an entry is written as the result of a t...

Page 207

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 207 of 864 installed with extclass = 0 regardless of the value of the tlb entry iprot bit. Tlb entries created via page table translation (that is, by the hardware page table walker) are always created with iprot = 0 and ...

Page 208

User’s manual a2 processor memory management page 208 of 864 version 1.3 october 23, 2012 the tlbwe with mas0[hes] = 0 back-invalidate scenario above is intended to represent software overwriting a specific, valid tlb entry whose virtual address matches that of a shadow erat copy. This is particular...

Page 209

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 209 of 864 when translations occur in the i-erat due to instruction fetches, the class field is not used as part of the compare function (assuming mmucr1[ictid] = 0). When translations occur in the d-erat, however, the cl...

Page 210

User’s manual a2 processor memory management page 210 of 864 version 1.3 october 23, 2012 this, hypervisor software must always ensure that at least one valid logical to real address translation (lrat) entry exists. The a2 core implements an 8-entry, fully-associative logical to lrat array in suppor...

Page 211

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 211 of 864 include: 1 mb, 16 mb, 256 mb, 1 gb, 4 gb, 16 gb, 256 gb, and 1 tb. These logical pages, or sectors, can be sized by the hypervisor to encompass a single large effective page or many smaller effective pages mapp...

Page 212

User’s manual a2 processor memory management page 212 of 864 version 1.3 october 23, 2012 6.9 tlb management instructions (architected) to enable software to manage the tlb, a set of tlb management instructions is implemented within the a2 core. These instructions are described briefly in the sectio...

Page 213

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 213 of 864 this processor is compliant with category e.Pt, and the size and location of the hardware page tables and format of the associated hardware page table entries are well defined. Aside from this, this processor c...

Page 214

User’s manual a2 processor memory management page 214 of 864 version 1.3 october 23, 2012 ferred. When mas0[hes] = 1, the entry way is defined by the hardware lru mechanism (which always excludes entries with iprot = 1). Finally, the contents of the selected tlb entry are transferred from the approp...

Page 215

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 215 of 864 writing tlb entries with tlbwe is supervisory privileged and is executable by either the hypervisor or a guest operating system (msr[gs] = 1). The guest’s view of real addresses are actually termed “logical add...

Page 216

User’s manual a2 processor memory management page 216 of 864 version 1.3 october 23, 2012 6.9.4 tlb invalidate virtual address (indexed) instruction (tlbivax) the tlbivax instruction is used to invalidate tlb and erat entries that contain the virtual page number asso- ciated with the effective addre...

Page 217

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 217 of 864 incoming invalidation snoop lpid value matches the current value of the lpidr[lpid] field, there is no rejec- tion of the transaction by the mmu; and a tlbi_complete is issued to the memory subsystem as after t...

Page 218

User’s manual a2 processor memory management page 218 of 864 version 1.3 october 23, 2012 6.9.5 tlb invalidate local (indexed) instruction (tlbilx) the tlbilx instruction is used to invalidate tlb and erat entries that contain the virtual page number associ- ated with the effective address of this i...

Page 219

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 219 of 864 the tlbsync instruction can be used (in memory subsystems that support this behavior) to ensure that the effects of global tlbivax and erativax operations have been made globally visible. Generally, this behavi...

Page 220

User’s manual a2 processor memory management page 220 of 864 version 1.3 october 23, 2012 erat entry is to be transferred (that is, ws = 0 specifies erat word 0, and so on). Finally, the contents of the selected erat word are transferred to or from a designated target or source gpr (and the mmucr0 g...

Page 221

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 221 of 864 page 189). Finally, the index of the matching entry is written into the target register (rt). This index value can then serve as the source value for a subsequent eratre or eratwe instruction, to read or update...

Page 222

User’s manual a2 processor memory management page 222 of 864 version 1.3 october 23, 2012 the erativax invalidation snoops from the bus contain a target lpid value. The handling of the invalidation snoops based on this lpid value is dependent on the configured mode of the receiving core. While a het...

Page 223

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 223 of 864 when global erativax operations are sent over certain system bus structures (such as the pbus), some of the information associated with the invalidate transaction needs to be condensed to conform to the bus wid...

Page 224

User’s manual a2 processor memory management page 224 of 864 version 1.3 october 23, 2012 6.10.4 erat invalidate local (indexed) instruction (eratilx) the eratilx instruction is used to invalidate local erat entries that contain the virtual page number associ- ated with the effective address of this...

Page 225

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 225 of 864 tlb hit reloads in mmu mode, need to have the upper 32 bits of the effective page number zeroed at the time of installation to have effective addresses compare successfully on these entries. This is done automa...

Page 226

User’s manual a2 processor memory management page 226 of 864 version 1.3 october 23, 2012 6.11.4 32-bit mode tlb invalidate virtual address (indexed) instruction (tlbivax) the tlbivax instruction is used to invalidate tlb (and erat) entries that contain the virtual page number associated with the ef...

Page 227

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 227 of 864 6.11.8 32-bit mode erat search instruction (eratsx[.]) in 32-bit mode, the eratsx[.] instruction is used to locate an entry in the i-erat or d-erat that is associated with a particular virtual address. This ins...

Page 228

User’s manual a2 processor memory management page 228 of 864 version 1.3 october 23, 2012 forwarding invalidation snoops to target processors. This implies that the effective page number (epn) in the erat entries that pertain to the current 32-bit process need to have been created with zeros in the ...

Page 229

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 229 of 864 if a write access is later attempted, a write access control exception type of data storage interrupt occurs. The interrupt handler can choose to record the change status to the memory page in a software table,...

Page 230

User’s manual a2 processor memory management page 230 of 864 version 1.3 october 23, 2012 a result of an eratsx or eratre instruction). When executing an i-erat or d-erat translation, parity is checked for the tag and data words. When executing an eratsx, only the tag parity is checked. When executi...

Page 231

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 231 of 864 achieved by protecting 511 out of 512 tlb entries is sufficient. Further, the software technique of simply dedi- cating a tlb entry to the page that contains the machine check handler and periodically refreshin...

Page 232

User’s manual a2 processor memory management page 232 of 864 version 1.3 october 23, 2012 mtspr mmucr1,rx ; set some mmucr1[pei] bits, and [csinv]=11. Isync ; wait for the mmmur1 context to update. Eratwe rs,ra,1 ; set up real portion word 1 of erat data. Eratwe rs,ra,0 ; write some data to the erat...

Page 233

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 233 of 864 based on this tlb reservation. Because tlb writes by other threads reset the reservation and the tlbsrx. Instruction can be used to detect tlb entries created by other threads, there is protection against dupli...

Page 234

User’s manual a2 processor memory management page 234 of 864 version 1.3 october 23, 2012 a tlb reservation is established or set (the reservation latch fields are updated and the valid bit is set to ‘1’), only by execution of the tlbsrx. Instruction. The result of the search of the tlb is irrelevan...

Page 235

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 235 of 864 f. The mas1 ts value used by the tlbwe matches the as value associated with the tlb reservation. G. Bits 0:(n-1) of mas2 epn used by the tlbwe match the epn 0:n-1 values associated with the tlb reser- vation, w...

Page 236

User’s manual a2 processor memory management page 236 of 864 version 1.3 october 23, 2012 (2) the mas0 wq used by the tlbwe instruction is 0b11 (this mas0 wq reserved setting is treated the same as the setting of 0b00, or write tlb always). 2. A tlbilx instruction is executed by the thread holding t...

Page 237

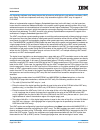

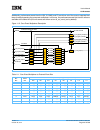

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 237 of 864 6.16 hardware page table walking (category e.Pt) this processor supports the power isa category embedded.Page table (e.Pt) and the embedded mmu architecture version 2.0 (mav 2.0). Because this processor also su...

Page 238

User’s manual a2 processor memory management page 238 of 864 version 1.3 october 23, 2012 6.16.2 indirect tlb entry page and sub-page sizes each indirect tlb entry represents a hardware page table in memory, and there can be many disjoint page tables existing in various areas of real memory. Each in...

Page 239

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 239 of 864 lar page table. To accomplish this, the operating system needs to install 16 mb/64 kb = 256 duplicates of the 16 mb size pte so that the first virtual address falling in this 1/16 “chunk” of the 256 mb indirect...

Page 240

User’s manual a2 processor memory management page 240 of 864 version 1.3 october 23, 2012 6.16.4 calculation of hardware page table entry real address although this processor implements only power of 4 1 k page sizes and sub-page sizes, for the sake of this example, tsize and spsize are interprete...

Page 241

ea 64-p:63 , where p = log 2 (page size specified by pte ps ). Finally, if the indirect entry’s tgs = 1 (a guest pa...

Page 242

User’s manual a2 processor memory management page 242 of 864 version 1.3 october 23, 2012 subsystem when the hardware walker fetches a pte entry. It is the responsibility of software installing the indirect tlb entry to ensure that the wimge settings are valid. Execution of a tlbwe with mas1 ind = 1...

Page 243

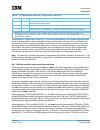

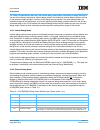

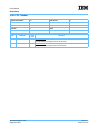

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 243 of 864 c n pte c wlc n 0b00 resvattr n 0 table 6-14. Tlb update after page table translation (sheet 2 of 2) tlb field architected? New value after page table translation 1. The tlb page size field supported by this im...

Page 244

User’s manual a2 processor memory management page 244 of 864 version 1.3 october 23, 2012 6.17 storage control registers (architected) this section describes the specific implementation of the architected storage control related registers. In addi- tion to the registers described below, the msr[is,d...

Page 245

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 245 of 864 6.17.2 logical partition id register (lpidr) the lpidr is written from a gpr using mtspr and can be read into a gpr using mfspr. This register is shared between all processing threads. Therefore, software locki...

Page 246

User’s manual a2 processor memory management page 246 of 864 version 1.3 october 23, 2012 6.17.3 external pid load context (eplc) register the eplc is written from a gpr using mtspr and can be read into a gpr using mfspr. The eplc register contains fields that provide the context for external pid lo...

Page 247

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 247 of 864 6.17.4 external pid store context (epsc) register the epsc is written from a gpr using mtspr and can be read into a gpr using mfspr. The epsc register contains fields that provide the context for external pid s...

Page 248

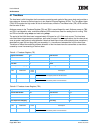

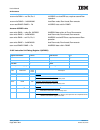

User’s manual a2 processor memory management page 248 of 864 version 1.3 october 23, 2012 6.17.5 mmu assist register 0 (mas0) the mas0 register is written from a gpr using mtspr and can be read into a gpr using mfspr. This register is replicated for all processing threads. Mas0 is used to define whi...

Page 249

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 249 of 864 6.17.6 mmu assist register 1 (mas1) the mas1 register is written from a gpr using mtspr and can be read into a gpr using mfspr. This register is replicated for all processing threads. Mas1 is used by certain tl...

Page 250

User’s manual a2 processor memory management page 250 of 864 version 1.3 october 23, 2012 programming note 1: this register provides for setting the iprot protection bit of tlb entries. For this implementation, it is recommended that no more than two entries in any single congruence class of the tlb...

Page 251

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 251 of 864 tlbilx instructions regardless of where they are placed within a tlb congruence class). As such, when imple- menting a totally software-managed tlb system, using only tlbwe with mas0[hes] = 0 to install tlb ent...

Page 252

User’s manual a2 processor memory management page 252 of 864 version 1.3 october 23, 2012 6.17.8 mmu assist register 2 upper (mas2u) the mas2u register is written from a gpr using mtspr and can be read into a gpr using mfspr. This register is replicated for all processing threads. Mas2u is used by c...

Page 253

User’s manual a2 processor version 1.3 october 23, 2012 memory management page 253 of 864 6.17.9 mmu assist register 3 (mas3) the mas3 register is written from a gpr using mtspr, and can be read into a gpr using mfspr. This register is replicated for all processing threads. Mas3 is used by certain t...

Page 254