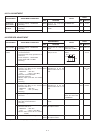

Icom IC-A200 Service Manual - page 9

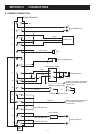

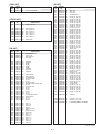

3-3 PLL CIRCUITS

3-3-1 GENERAL (PLL UNIT)

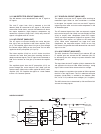

The PLL circuit steadily oscillates the transmit and receive

local frequencies while comparing the phase of the divided

VCO frequency and reference frequency. Therefore, the PLL

output frequency is controlled by the divided ratio (N-data)

of the programmable divider.

The oscillated signal in the VCO circuit is divided by N-data

at a programmable, divider and is phase detected with the

reference frequency at a phase comparator. The detected

signal (pulse-type signal) is rectified by a loop filter and

converted to DC voltage (PLL lock voltage). This voltage is

applied to varactor diodes in .the VCO unit to control the

oscillating frequency. Hence, this loop provides a variable

and stable oscillating frequency.

IC2001 includes the prescaler, programmable divider, phase

comparator, etc. in one chip.

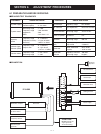

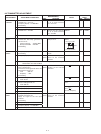

3-3-2 REFERENCE OSCILLATOR CIRCUIT

(MAIN UNIT)

The reference frequency oscillator oscillates at a stable

32.000 MHz which is used for the PLL reference frequency,

receive and transmit LO frequency. AGC minus voltages are

used to detect this frequency.

The reference frequency (32.000 MHz) is generated by the

oscillator circuit of IC19 and X1. The reference frequency

is divided by 4 at IC1 and is then applied to the PLL board.

The frequency is divided again in PLL IC (IC2001) by 1/320

to obtain the PLL reference frequency of 25 kHz.

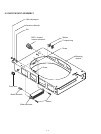

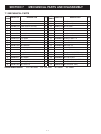

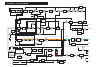

3-3-3 VCO CIRCUIT (VCO UNIT)

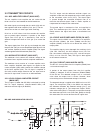

The VCO circuits oscillate the PLL output frequency by

controlling varactor diodes (D2001–D2003).

The VCO circuits (Q2004) employs a clap oscillator circuit.

The signal generated at the VCO is buffer-amplified at

Q2001 or Q2002. The amplified signals are used for a

receive/transmit LO signal as PLL output (OUT2) or used

for a feedback signal (OUT1) to the PLL circuit.

3-3-4 PHASE DETECTOR CIRCUITS (PLL UNIT)

The phase-detector circuit detects the out-of-phase

components of the VCO frequency using a stable reference

frequency.

The PLL IC (IC1001) contains a prescaler, programmable

divider, high-speed phase detector and shift register. The

oscillated signal comes from the VCO board and enters

IC1001 (pin 11). Then, it is divided at the prescaler and

divided again at the programmable divider. The divided

signal is applied to a phase detector to compare it with a

reference frequency (25 kHz). The detected signal exits

IC1001 (pin 7).

3-3-5 LOOP FILTER CIRCUIT

An active loop filter circuit is adopted for this PLL circuit to

convert the phase-detected signal to DC voltage (PLL lock

voltage) and to obtain needed levels to control the VCO

circuit.

The active loop filter (Q1002–Q1004) converts the phase-

detected signal (pulse-type signal) to DC voltage (PLL lock

voltage) to control the VCO oscillating signal. The PLL lock

voltage changes the reactance of varactor diodes in the

VCO circuit.

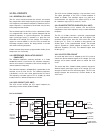

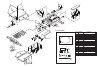

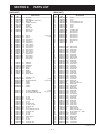

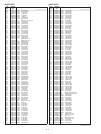

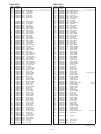

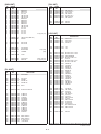

PLL VCO CIRCUIT

3 - 4