Icom IC-R2 Service Manual - page 9

4 - 3

• TONE SQUELCH

The tone squelch circuit detects AF signals and opens the

squelch only when receiving a signal containing a matching

subaudible tone (CTCSS). When tone squelch is in use, and

a signal with a mismatched or no subaudible tone is

received, the tone squelch circuit mutes the AF signals even

when noise squelch is open.

A portion of the AF signals from the FM IF IC (IC2, pin 9)

passes through the low-pass filter (LOGIC unit; IC9) via the

“WFMS” line to remove AF (voice) signals and is applied to

the CTCSS decoder inside the CPU (LOGIC unit; IC11, pin

8) via the “RTONE” line to control the AF mute switch.

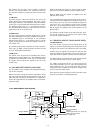

4-2 PLL CIRCUITS

4-2-1 PLL CIRCUIT (RF UNIT)

A PLL circuit provides stable oscillation of the receive

1st/2nd LO frequencies. The PLL circuit compares the

phase of the divided VCO frequency to the reference fre-

quency. The PLL output frequency is controlled by the divid-

ed ratio (N-data) of a programmable divider.

An oscillated signal from the 1st VCO passes thorough the

buffer amplifiers (IC4, Q43) is applied to the PLL IC (IC3, pin

19) and is prescaled in the PLL IC based on the divided ratio

(N-data). The PLL IC detects the out-of-step phase using the

reference frequency and outputs it from pin 13. The output

signal is passed through the loop filter (Q2, Q45) and is then

applied to the 1ST VCO circuit as the lock voltage.

4-2-2 REFERENCE OSCILLATOR CIRCUIT

(RF UNIT)

The reference oscillator circuit (X1, IC3) generates a 19.2

MHz reference frequency which is stabilized within the tem-

perature range –10˚C (+14˚F) to +60˚C (+140˚F). The refer-

ence frequency is applied to the PLL IC (IC3, pin 16) and the

signal is output from the pin 17, and is then applied to the

FM IF IC (IC2, pin 2) via the low-pass fileter.

4-2-3 1ST VCO CIRCUIT (RF UNIT)

The oscillated signal is applied to the buffer amplifiers (IC4,

Q40). The amplified signal is applied to the 1st mixer circuit

(IC1) via the RX LO swtich circuit (D42–D44) and doubler

circuit (Q31).

The 1st VCO circuit (Q28, Q30, D54) oscillates 267.2

MHz–380 MHz and 380 MHz–550 MHz by switching the

SHIFT switch (Q29) “High” and “Low” respectively.

A portion of the signal from IC4 is amplified at the buffer

amplifier (Q43) and is then fed back to the PLL IC (IC3, pin

2) as the comparison signal.

4-2-4 2nd VCO CIRCUIT (RF UNIT)

The 2nd LO circuit generates the 2nd LO frequencies, and

the signals are applied to the 2nd mixer circuit.

The 2nd VCO circuit (Q6, L45, C80, C207, C208) oscillates

260 MHz. The oscillated signal is applied to the 2nd mixer

(IC10, pin 3), and is then mixed with the 1st IF signal.

An oscillated signal from the 2nd VCO passes through the

low-pass filter (C154, C250–C252, L69), and is applied to

the PLL IC (IC3, pin 2), and is then output from pin 8.

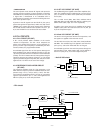

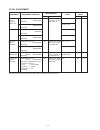

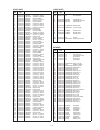

• PLL circuit

Shift register

Prescaler

Phase

detector

Loop

filter

Programmable

counter

Programmable

divider

X1

19.2 MHz

to the FM IF IC

1st VCO

Buffer

Buffer

Buffer

Q40

Q43

IC4

3

4

5

PSTB

IC3 (PLL IC)

CLK

DATA

to 1st mixer circuit

17

16

13

19

Q28, Q30, D54

Q2, Q45

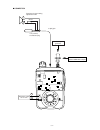

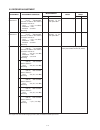

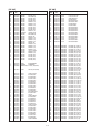

• 2nd LO VCO circuit

Q6, D17

VCO

2nd LO

VCO

Loop

filter

Ripple

filter

LPF

Q37, D53

R3V

to the 2nd mixer (IC10)

PLL IC

IC3

8

2