- DL manuals

- Jameco Electronics

- Computer Hardware

- Rabbit 2000

- User Manual

Jameco Electronics Rabbit 2000 User Manual

Summary of Rabbit 2000

Page 1

The content and copyrights of the attached material are the property of its owner. Distributed by: www.Jameco.Com ✦ 1-800-831-4242.

Page 2: Rabbit 3000

Rabbit 3000 ® microprocessor user’s manual 019–0108 • 040731–o ®.

Page 3

Rabbit 3000 microprocessor rabbit semiconductor 2932 spafford street davis, california 95616-6800 usa telephone: (530) 757-8400 fax: (530) 757-8402 www.Rabbitsemiconductor.Com rabbit 3000 microprocessor user’s manual part number 019-0108 • 040731–o • printed in u.S.A. ©2002–2004 rabbit semiconductor...

Page 4: Able

User’s manual t able of c ontents chapter 1. Introduction 1 1.1 features and specifications rabbit 3000 ..............................................................................................2 1.2 summary of rabbit 3000 advantages .................................................................

Page 5

Rabbit 3000 microprocessor 3.5 interrupt structure .............................................................................................................................. 44 3.5.1 interrupt priority .................................................................................................

Page 6

User’s manual 8.5 memory bank control registers ......................................................................................................120 8.5.1 optional a16, a19 inversions by segment (/cs1 enable) .....................................................121 8.6 allocation of extended co...

Page 7

Rabbit 3000 microprocessor chapter 14. Rabbit 3000 clocks 209 14.1 low-power design......................................................................................................................... 210 chapter 15. Emi control 211 15.1 power supply connections and board layout ...................

Page 8

User’s manual 19.16 block move instructions...............................................................................................................256 19.17 control instructions - jumps and calls.........................................................................................257 19.18...

Page 9

Rabbit 3000 microprocessor.

Page 10: 1. I

User’s manual 1 1. I ntroduction rabbit semiconductor was formed expressly to design a a better microprocessor for use in small and medium-scale controllers. The first microprocessor was the rabbit 2000 . The second microprocessor, now available, is the rabbit 3000 . Rabbit microprocessor design- er...

Page 11

2 rabbit 3000 microprocessor 1.1 features and specifications rabbit 3000 • 128-pin lqfp package. Operating voltage 1.8 v to 3.6 v. Clock speed to 54+ mhz. All specifications are given for both industrial and commercial temperature and voltage ranges. Rabbit microprocessors are low-cost. • industrial...

Page 12

User’s manual 3 a rabbit that is slaved to a master processor can operate entirely with volatile ram, depending on the master for a cold program boot. • there are 56 parallel i/o lines (shared with serial ports). Some i/o lines are timer syn- chronized, which permits precisely timed edges and pulses...

Page 13

4 rabbit 3000 microprocessor • a built-in clock doubler allows ½-frequency crystals to be used. • the built-in main clock oscillator uses an external crystal or a ceramic resonator. Typical crystal or resonator frequencies are in the range of 1.8 mhz to 30 mhz. Since precision timing is available fr...

Page 14

User’s manual 5 figure 1-1. Rabbit 3000 block diagram cpu external interface data buffer memory management/ control address buffer memory chip interface parallel ports port a port b port c port d port e port f port g global power save & clock distribution fast oscillator timer a timer b real-time cl...

Page 15

6 rabbit 3000 microprocessor 1.2 summary of rabbit 3000 advantages • the glueless architecture makes it is easy to design the hardware system. • there are a lot of serial ports and they can communicate very fast. • precision pulse and edge generation is a standard feature. • emi is at extremely low ...

Page 16

User’s manual 7 1.3 differences rabbit 3000 vs. Rabbit 2000 for the benefit of readers who are familiar with the rabbit 2000 microprocessor the rab- bit 3000 is contrasted with the rabbit 2000 in the table below. Feature rabbit 3000 rabbit 2000 maximum clock speed 54 mhz 30 mhz maximum crystal frequ...

Page 17

8 rabbit 3000 microprocessor serial ports with support for sdlc/hdlc irda communications 2 none maximum asynchronous baud rate clock speed/8 clock speed/32 input capture unit 2 none feature rabbit 3000 rabbit 2000

Page 18: 2. R

User’s manual 9 2. R abbit 3000 d esign f eatures the rabbit 3000 is an evolutionary design. The processor and instruction set are nearly identical to the immediate predecessor processor, the rabbit 2000. Both the rabbit 3000 and the rabbit 2000 follow in broad outline the instruction set and the re...

Page 19

10 rabbit 3000 microprocessor 2.1 the rabbit 8-bit processor vs. Other processors the rabbit 3000 processor has been designed with the objective of creating practical sys- tems to solve real world problems in an economical fashion. A cursory comparison of the rabbit 3000 compared to other processors...

Page 20

User’s manual 11 the rabbit is an 8-bit processor with an 8-bit external data bus and an 8-bit internal data bus. Because the rabbit makes the most of its external 8-bit bus and because it has a com- pact instruction set, its performance is as good as many 16-bit processors. We hesitate to compare t...

Page 21

12 rabbit 3000 microprocessor important for rs-485 communication because a half duplex line driver cannot have the direction of transmission reversed until the last data bit has been sent. In many uarts, including those on the z180, it is difficult to generate an interrupt after the last bit is sent...

Page 22

User’s manual 13 2.2.5 parallel i/o there are 56 parallel input/output lines divided among seven 8-bit ports designated a through g. Most of the port lines have alternate functions, such as serial data or chip select strobes. Parallel ports d, e, f, and g have the capability of timer-synchronized ou...

Page 23

14 rabbit 3000 microprocessor 2.2.6 slave port the slave port is designed to allow the rabbit to be a slave to another processor, which could be another rabbit. The port is shared with parallel port a and is a bidirectional data port. The master can read any of three registers selected via two selec...

Page 24

User’s manual 15 2.2.7 auxiliary i/o bus the rabbit 3000 instruction set supports memory access and i/o access. Memory access takes place in a 1 megabyte memory space. I/o access takes place in a 64k i/o space. In a traditional microprocessor design the same address and data lines are used for both ...

Page 25

16 rabbit 3000 microprocessor figure 2-4. Rabbit timers a and b 2.2.9 input capture channels the input capture channels are used to determine the time at which an event takes place. An event is signaled by a rising or falling edge (or optionally by either edge) on one of 16 input pins that can be se...

Page 26

User’s manual 17 and stop condition, for example a rising edge could be the start condition and a falling edge the stop condition. However, optionally, the start and stop condition can be input from separate pins. The input capture channels can be used to measure the width of fast pulses. This is do...

Page 27

18 rabbit 3000 microprocessor length of the pulses. When the duty cycle is greater then 1/1024 the pulses are spread into groups distributed 256 counts apart in the 1024 frame. The pulse width modulation outputs can be passed through a filter and used as a 10-bit d/a converter. The outputs can also ...

Page 28

User’s manual 19 reset pin, and to a programmable output pin that is used to signal the pc that attention is needed. With proper precautions in design and software, it is possible to use serial port a as both a programming port and as a user-defined serial port, although this will not be nec- essary...

Page 29

20 rabbit 3000 microprocessor.

Page 30: 3. D

User’s manual 21 3. D etails on r abbit m icroprocessor f eatures 3.1 processor registers the rabbit’s registers are nearly identical to those of the z180 or the z80. The figure below shows the register layout. The xpc and ip registers are new. The eir register is the same as the z80 i register, and...

Page 31

22 rabbit 3000 microprocessor the rabbit (and the z80/z180) processor has two accumulators—the a register serves as an 8-bit accumulator for 8-bit operations such as add or and . The 16-bit register hl regis- ter serves as an accumulator for 16-bit operations such as add hl,de , which adds the 16- b...

Page 32

User’s manual 23 3.2 memory mapping although the rabbit memory mapping scheme is fairly complex, the user rarely needs to worry about it because the details are handled by the dynamic c development system. Except for a handful of special instructions (see section 19.5, “16-bit load and store 20- bit...

Page 33

24 rabbit 3000 microprocessor figure 3-3. Example of memory mapping operation the names given to the segments in the figure are evocative of the common uses for each segment. The root segment is mapped to the base of flash memory and contains the startup code as well as other code that may happen to...

Page 34

User’s manual 25 the root segment or it may contain data variables. The stack segment is normally 4k long and it holds the system stack. The xpc segment is normally used to execute code that is not stored in the root segment or the data segment. Special instructions support executing code that is vi...

Page 35

26 rabbit 3000 microprocessor 3.2.1 extended code space a crucial element of the rabbit memory mapping scheme is the ability to execute pro- grams containing up to a megabyte of code in an efficient manner. This ability is absent in a pure 16-bit address processor, and it is poorly supported by the ...

Page 36

User’s manual 27 than the xpc segment, can call other code in the root using short jumps and calls. Code in the xpc segment can also call code in the root using short jumps and calls. However, a long call must be used when code in the xpc segment is called. Functions located in the root have an effi...

Page 37

28 rabbit 3000 microprocessor fetching an instruction from memory and fetching or storing data in memory. When enabled separate i and d space make available the combined root and data segment, typi- cally 52k bytes for root code in the i space. In the d space, the root code segment part of the d spa...

Page 38

User’s manual 29 not have split i and d space and memory accesses to these segments do not distinguish between i and d space. The advantage of having more root code space is that root code executes faster because short calls using a 16 bit address are used to call it. This compares to long calls tha...

Page 39

30 rabbit 3000 microprocessor figure 3-7. Schemes for data memory windows a third approach is to place the data and root code in ram in the root segment, freeing the data segment to be a window to extended memory. This requires copying the root code to ram at startup time. Copying root code to ram i...

Page 40

User’s manual 31 ded applications. Some applications may require large data arrays or tables that will require additional data memory. For this purpose dynamic c supports a type of extended data memory that allows the use of additional data memory, even extending far beyond a megabyte. Requirements ...

Page 41

32 rabbit 3000 microprocessor 3.3 instruction set outline “load immediate data to a register” on page 33 “load or store data from or to a constant address” on page 33 “load or store data using an index register” on page 34 “register-to-register move” on page 35 “register exchanges” on page 35 “push ...

Page 42

User’s manual 33 • input/output instructions are now accomplished by normal memory access instructions prefixed by an op code byte to indicate access to an i/o space. There are two i/o spaces, internal peripherals and external i/o devices. Some z80 and z180 instructions have been deleted and are not...

Page 43

34 rabbit 3000 microprocessor 3.3.3 load or store data using an index register an index register is a 16-bit register, usually ix, iy, sp or hl, that is used for the address of a byte or word to be fetched from or stored to memory. Sometimes an 8-bit offset is added to the address either as a signed...

Page 44

User’s manual 35 3.3.4 register-to-register move any of the 8-bit registers, a, b, c, d, e, h, and l, can be moved to any other 8-bit regis- ter, for example: ld a,c ld d,b ld e,l the alternate 8-bit registers can be a destination, for example: ld a’,c ld d’,b these instructions are unique to the ra...

Page 45

36 rabbit 3000 microprocessor 3.3.6 push and pop instructions there are instructions to push and pop the 16-bit registers af, hl, dc, bc, ix, and iy. The registers af', hl', de', and bc' can be popped. Popping the alternate registers is exclusive to the rabbit, and is not allowed on the z80 / z180. ...

Page 46

User’s manual 37 the bool instruction is a special instruction designed to help test the hl register. Bool sets hl to the value 1 if hl is non zero, otherwise, if hl is zero its value is not changed. The flags are set according to the result. Bool can also operate on ix and iy. Bool hl ; set hl to 1...

Page 47

38 rabbit 3000 microprocessor the sbc instruction can also be used to perform a sign extension. ; extend sign of l to hl ld a,l rla ; sign to carry sbc a,a ; a is all 1’s if sign negative ld h,a ; sign extended the multiply instruction performs a signed multiply that generates a 32-bit signed result...

Page 48

User’s manual 39 3.3.8 input/output instructions the rabbit uses an entirely different scheme for accessing input/output devices. Any memory access instruction may be prefixed by one of two prefixes, one for internal i/o space and one for external i/o space. When so prefixed, the memory instruction ...

Page 49

40 rabbit 3000 microprocessor 3.4 how to do it in assembly language—tips and tricks 3.4.1 zero hl in 4 clocks bool hl ; 2 clocks, clears carry, hl is 1 or 0 rr hl ; 2 clocks, 4 total - get rid of possible 1 this sequence requires four clocks compared to six clocks for ld hl,0 . 3.4.2 exchanges not d...

Page 50

User’s manual 41 3.4.4 comparisons of integers unsigned integers may be compared by testing the zero and carry flags after a subtract operation. The zero flag is set if the numbers are equal. With the sbc instruction the carry cleared is set if the number subtracted is less than or equal to the numb...

Page 51

42 rabbit 3000 microprocessor some simplifications are possible if one of the unsigned numbers being compared is a constant. Note that the carry has a reverse sense from sbc . In the following examples, the pseudo-code in the form ld de,(65535-b) does not indicate a load of de with the address point...

Page 52

User’s manual 43 a>b (!S & !V & !Z) v (s & v) a a==b a>=b a another method of doing signed compare is to first map the signed integers onto unsigned integers by inverting bit 15. This is shown in figure 3-8. Once the mapping has been per- formed by inverting bit 15 on both numbers, the comparisions ...

Page 53

44 rabbit 3000 microprocessor 3.5 interrupt structure when an interrupt occurs on the rabbit, the return address is pushed on the stack, and con- trol is transferred to the address of the interrupt service routine. The address of the inter- rupt service routine has two parts: the upper byte of the a...

Page 54

User’s manual 45 the same priority, this introduces interrupt latency while the next routine is waiting for the previous routine to allow more interrupts to take place. If a number of devices have inter- rupt service routines, and all interrupts are of the same priority, then pending interrupts can ...

Page 55

46 rabbit 3000 microprocessor 3.5.2 multiple external interrupting devices the rabbit 3000 has two distinct external interrupt request lines. If there are more than two external causes of interrupts, then these lines must be shared between multiple devices. The interrupt line is edge-sensitive, mean...

Page 56

User’s manual 47 the privileged instructions to manipulate the ip register are listed below. Ipset 0 ; shift ip left and set priority 00 in bits 1,0 ipset 1 ipset 2 ipset 3 ipres ; rotate ip right 2 bits, restoring previous priority reti ; pops ip from stack and then pops return address pop ip ; pop...

Page 57

48 rabbit 3000 microprocessor 3.5.6 computed long calls and jumps the instruction to set the xpc is privileged to so that a computed long call or jump can be made. This would be done by the following sequence. Ld xpc,a jp (hl) in this case, a has the new xpc, and hl has the new pc. This code should ...

Page 58: 4. R

User’s manual 49 4. R abbit c apabilities this chapter describes the various capabilities of the rabbit that may not be obvious from the technical description. 4.1 precisely timed output pulses the rabbit can output precise pulses under software control. The effect of interrupt latency is avoided be...

Page 59

50 rabbit 2000 microprocessor pulse width modulated outputs—the minimum pulse width is 10 µs. If the repetition rate is 10 ms, then a new pulse with 1000 different widths can be generated at the rate of 100 times per second. Asynchronous communications serial output—asynchronous output data can be g...

Page 60

User’s manual 51 4.2 open-drain outputs used for key scan the parallel port d outputs can be individually programmed to be open drain. This is use- ful for scanning a switch matrix, as shown in figure 4-2. A row is driven low, then the col- umns are scanned for a low input line, which indicates a ke...

Page 61

52 rabbit 2000 microprocessor 4.3 cold boot most microprocessors start executing at a fixed address, often address zero, after a reset or power-on condition. The rabbit has two mode pins (smode0, smode1—see figure 5- 1). The logic state of these two pins determines the startup procedure after a rese...

Page 62

User’s manual 53 4.4 the slave port the slave port allows a rabbit to act as a slave to another processor, which can also be a rabbit. The slave has to have only a processor chip, a ram chip, and clock and reset sig- nals that can be supplied by the master. The master can cold boot and download a pr...

Page 63

54 rabbit 2000 microprocessor of the three registers seen by each side for each direction of communication, the first reg- ister, slave register zero, has a special function because an interrupt can only be generated by a write to this register, which then causes an interrupt to take place on the ot...

Page 64: 5. P

User’s manual 55 5. P in a ssignments and f unctions.

Page 65

56 rabbit 3000 microprocessor 5.1 lqfp package 5.1.1 pinout rabbit 3000 (at56c55-il1t, il2t) 128-pin low-profile quad flat pack (lqfp) 14 × 14 body, 0.4 mm pitch figure 5-1. Package outline and pin assignments 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 96 ...

Page 66

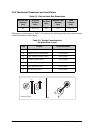

User’s manual 57 5.1.2 mechanical dimensions and land pattern figure 5-2 shows the mechanical dimensions of the rabbit 3000 lqfp package. Figure 5-2. Mechanical dimensions rabbit lqfp package 14.00 ± 0.10 mm 16.00 ± 0.25 mm + 0.10 mm 0.15 mm 0.60 0.18 ± 0.05 mm 0.40 mm 14.00 ± 0.10 mm 16.00 ± 0.25...

Page 67

58 rabbit 3000 microprocessor figure 5-3 shows the pc board land pattern for the rabbit 3000 chip in a 128-pin lqfp package. This land pattern is based on the ipc-sm-782 standard developed by the surface mount land patterns committee and specified in surface mount design and land pat- tern standard ...

Page 68

User’s manual 59 5.2 ball grid array package 5.2.1 pinout rabbit 3000 (at56c55-iz1t, iz2t) 128-pin thin map ball grid array (tfbga) 10 × 10 body, 0.8 mm pitch figure 5-4. Ball grid array pinout looking through the top of package 1 2 3 4 5 6 7 8 9 10 11 12 a b c d e f g h j k l m vddio vssio pf5 pb6 ...

Page 69

60 rabbit 3000 microprocessor 5.2.2 mechanical dimensions and land pattern the design considerations in table 5-3 are based on 5 mil design rules and assume a single conductor between solder lands. Table 5-2. Ball and land size dimensions nominal ball diameter (mm) tolerance variation (mm) ball pitc...

Page 70

User’s manual 61 figure 5-5. Bga package outline a b c d e f g h j k l m 12 11 10 9 8 7 6 5 4 3 2 1 a b c d e f g h j k l m 12 11 10 9 8 7 6 5 4 3 2 1 0.80 10.00 ± 0.05 0.80 10.00 ± 0.05 0.20~0.30 1.20 (max.) ball pitch: ball diameter: 0.80 mm 0.3 mm (0.25~0.35) top view bottom view.

Page 71

62 rabbit 3000 microprocessor 5.3 rabbit pin descriptions table 5-1 lists all the pins on the device, along with their direction, function, and pin num- ber on the package. Table 5-1. Rabbit pin descriptions pin group pin name direction function pin numbers lqfp pin numbers tfbga hardware clk output...

Page 72

User’s manual 63 i/o ports pa[7:0] input / output i/o port a 111–104 d7, a8, b8, c8, d8, a9, b9, c9 i/o ports (continued) pb[7:0] input / output i/o port b 123–116 c4, a5, b5, c5, d5, a6, b6, c6 pc[7:0] 4 in / 4 out i/o port c 66–71, 74, 75 l11, m11, m12, l12, k12, k11, j10, h12 pd[7:0] input / outp...

Page 73

64 rabbit 3000 microprocessor 5.4 bus timing the external bus has essentially the same timing for memory cycles or i/o cycles. A mem- ory cycle begins with the chip select and the address lines. One clock later, the output enable is asserted for a read. The output data and the write enable are asser...

Page 74

User’s manual 65 5.5 description of pins with alternate functions table 5-2. Pins with alternate functions pin name output function input function input capture option pa[7:0] slave d[7:0], id[7:0] slave d[7:0], id[7:0] pb7 slaveattn, ia5 pb6 ia4 /ascs * pb5 ia3 sd1 pb4 ia2 sd0 pb3 ia1 /srd pb2 ia0 ...

Page 75

66 rabbit 3000 microprocessor pf7 pwm3 aqd2a yes pf6 pwm2 aqd2b pf5 pwm1 aqd1a yes pf4 pwm0 aqd1b pf3 qd2a yes pf2 qd2b pf1 clkc qd1a, clkc yes pf0 clkd qd1b, clkd pg7 apwm1 * rxe yes pg6 txe pg5 rclke rclke, arxe * yes pg4 tclke tclke, arclke * pg3 apwm0 * rxf pg2 txf pg1 rclkf rclkf, arxf * pg0 tc...

Page 76

User’s manual 67 the alternate output functions identified in table 5-2 are configured by setting the appro- priate bits in the paralle port x function register. Table 5-3. Parallel port x alternate functions parallel port x function register (pcfr) (address = 0x0055) (pdfr) (address = 0x0065) (pefr...

Page 77

68 rabbit 3000 microprocessor 5.6 dc characteristics stresses beyond those listed in table 5-5 may cause permanent damage. The ratings are stress ratings only, and functional operation of the rabbit 3000 chip at these or any other conditions beyond those indicated in this section is not implied. Exp...

Page 78

User’s manual 69 5.7 i/o buffer sourcing and sinking limit unless otherwise specified, the rabbit i/o buffers are capable of sourcing and sinking 6.8 ma of current per pin at full ac switching speeds. The limits are related to the maxi- mum sustained current permitted by the metallization on the die...

Page 79

70 rabbit 3000 microprocessor.

Page 80: 6. R

User’s manual 71 6. R abbit i nternal i/o r egisters.

Page 81

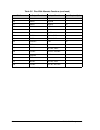

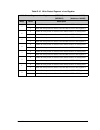

72 rabbit 3000 microprocessor table 6-1. Rabbit 3000 peripherals and interrupt service vectors on-chip peripheral isr starting address system management {iir[7:1], 0, 0x00} memory management no interrupts slave port {iir[7:1], 0, 0x80} parallel port a no interrupts parallel port f no interrupts para...

Page 82

User’s manual 73 6.1 default values for all the peripheral control registers the default values for all of the peripheral control registers are shown in table 6-2. The registers within the cpu affected by reset are the stack pointer (sp), the program counter (pc), the iir register, the eir register,...

Page 83

74 rabbit 3000 microprocessor global revision register grev 0x2f r 0xx00000 port a data register padr 0x30 r/w xxxxxxxx port b data register pbdr 0x40 r/w 00xxxxxx port b data direction register pbddr 0x47 w 11000000 port c data register pcdr 0x50 r/w x0x1x1x1 port c function register pcfr 0x55 w x0...

Page 84

User’s manual 75 port e bit 7 register peb7r 0x7f w xxxxxxxx port f data register pfdr 0x38 r/w xxxxxxxx port f control register pfcr 0x3c w xx00xx00 port f function register pffr 0x3d w xxxxxxxx port f drive control register pfdcr 0x3e w xxxxxxxx port f data direction register pfddr 0x3f w 00000000...

Page 85

76 rabbit 3000 microprocessor pwm msb 0 register pwm0r 0x89 w xxxxxxxx pwm lsb 1 register pwl1r 0x8a w xxxxxxxx pwm msb 1 register pwm1r 0x8b w xxxxxxxx pwm lsb 2 register pwl2r 0x8c w xxxxxxxx pwm msb 2 register pwm2r 0x8d w xxxxxxxx pwm lsb 3 register pwl3r 0x8e w xxxxxxxx pwm msb 3 register pwm3r...

Page 86

User’s manual 77 timer a time constant 5 register tat5r 0xab w xxxxxxxx timer a time constant 6 register tat6r 0xad w xxxxxxxx timer a time constant 7 register tat7r 0xaf w xxxxxxxx timer b control/status register tbcsr 0xb0 r/w xxxxx000 timer b control register tbcr 0xb1 w xxxx0000 timer b msb 1 re...

Page 87

78 rabbit 3000 microprocessor serial port d address register sdar 0xf1 r/w xxxxxxxx serial port d long stop register sdlr 0xf2 r/w xxxxxxxx serial port d status register sdsr 0xf3 r 0xx00000 serial port d control register sdcr 0xf4 w xx000000 serial port d extended register sder 0xf5 w 00000000 seri...

Page 88: 7. M

User’s manual 79 7. M iscellaneous f unctions 7.1 processor identification four read-only registers are provided to allow software to identify the rabbit micropro- cessor and recognize the features and capabilities of the chip. Five bits in each of these registers are unique to each version of the c...

Page 89

80 rabbit 3000 microprocessor 7.2 rabbit oscillators and clocks the rabbit 3000 usually requires two separate clocks. The main clock normally drives the processor core and most of the peripheral devices, and the 32.768 khz clock drives the battery-backable time-date clock and other circuitry. Main c...

Page 90

User’s manual 81 32.768 khz clock the 32.768 khz clock is primarily used to clock the on-chip real-time clock. In addition, it is also used to support remote cold boot via serial port a, driving the 2400 baud commu- nications used to initiate the cold boot. Another function of the 32.768 khz oscilla...

Page 91

82 rabbit 3000 microprocessor table 7-5. Global control/status register global control/status register (gcsr) (address = 0x00) bit(s) value description 7:6 (rd-only) 00 no reset or watchdog timer time-out since the last read. 01 the watchdog timer timed out. These bits are cleared by a read of this ...

Page 92

User’s manual 83 7.3 clock doubler the clock doubler is provided to allow a lower frequency crystal to be used for the main oscillator and to provide an added range of clock frequency adjustability. The clock dou- bler is controlled via the global clock double register as shown in table 7-7. The clo...

Page 93

84 rabbit 3000 microprocessor when the clock doubler is used and there is no subsequent division of the clock, the output clock will be asymmetric, as shown in figure 7-2. Figure 7-2. Effect of clock doubler the doubled-clock low time is subject to wide (50%) variation since it depends on process pa...

Page 94

User’s manual 85 variation in period on alternate clocks. This does not affect the no-wait states memory access time since two adjacent clocks are always used. However, the maximum allowed clock speed must be slightly reduced if the clock is supplied via the clock doubler. The only signals clocked o...

Page 95

86 rabbit 3000 microprocessor 7.4 clock spectrum spreader when enabled the spectrum spreader stretches and compresses the clocks in a complex pattern that results in spreading the energy in the clock harmonics over a wide range of frequencies. The spectrum spreader has a normal and a strong setting....

Page 96

User’s manual 87 7.5 chip select options for low power some types of flash memory and ram consume power whenever the chip select is enabled even if no signals are changing. The chip select behavior of the rabbit 3000 can be modified to reduce unnecessary power consumption when the rabbit 3000 is run...

Page 97

88 rabbit 3000 microprocessor when operating in the 32 khz mode, it is also possible to further divide the clock to a fre- quency as low as 2 khz, further reducing execution speed and current consumption. It is anticipated that these measures would reduce operating current consumption to as low as 2...

Page 98

User’s manual 89 figure 7-4. Short chip select memory read figure 7-5. Self-timed chip select memory read cycle clock addr data t1 t2 valid memoexb memcsxb 32 khz addr data t1 t2 valid valid m em oexb m em csxb ~100 ns.

Page 99

90 rabbit 3000 microprocessor 7.6 output pins clk, status, /wdtout, /bufen certain output pins can have alternate assignments as specified in table 7-9. Table 7-9. Global output control register (gocr = 0x0e) bit(s) value description 7:6 00 clk pin is driven with peripheral clock. 01 clk pin is driv...

Page 100

User’s manual 91 7.7 time/date clock (real-time clock) the time/date clock (rtc) is a 48-bit (ripple) counter that is driven by the 32.768 khz oscillator. The rtc is a modified ripple counter composed of six separate 8-bit counters. The carries are fed into all six 8-bit counters at the same time an...

Page 101

92 rabbit 3000 microprocessor table 7-10. Real-time clock rtcxr data registers real-time clock x holding register (rtc0r) r/w (address = 0x02) (rtc1r) (address = 0x03) (rtc2r) (address = 0x04) (rtc3r) (address = 0x05) (rtc4r) (address = 0x06) (rtc5r) (address = 0x07) bit(s) value description 7:0 rea...

Page 102

User’s manual 93 7.8 watchdog timer the watchdog timer is a 17-bit counter. In normal operation it is driven by the 32.768 khz clock. When the watchdog timer reaches any of several values corresponding to a delay of from 0.25 to 2 seconds, it “times out.” when it times out, it emits a 1-clock pulse ...

Page 103

94 rabbit 3000 microprocessor the code to do this may also hit the watchdog with a 0.25-second period to speed up the reset. Such watchdog code must be written so that it is highly unlikely that a crash will incorporate the code and continue to hit the watchdog in an endless loop. The following sugg...

Page 104

User’s manual 95 7.9 system reset the rabbit 3000 contains a master reset input (pin 46), which initializes everything in the device except for the real-time clock (rtc). This reset is delayed until the completion of any write cycles in progress to prevent potential corruption of memory. If no write...

Page 105

96 rabbit 3000 microprocessor table 7-14. Rabbit 3000 reset sequence and state of i/o pins pin name direction /reset low * recognized by cpu post-reset † /reset input low or high high clk output high operational clk32k input not affected not affected resout output high low xtala1 input not affected ...

Page 106

User’s manual 97 7.10 rabbit interrupt structure an interrupt causes a call to be executed, pushing the pc on the stack and starting to exe- cute code at the interrupt vector address. The interrupt vector addresses have a fixed lower byte value for all interrupts. The upper byte is adjustable by set...

Page 107

98 rabbit 3000 microprocessor in the case of the external interrupts the only action that will clear the interrupt request is for the interrupt to take place, which automatically clears the request. A special action must be taken in the interrupt service routine for the other interrupts. Table 7-15....

Page 108

User’s manual 99 7.10.1 external interrupts there are two external interrupts. Each interrupt has 2 input pins that can be used to trig- ger the interrupt. The inputs have a pulse catcher that can detect rising, falling or either ris- ing or falling edges. Figure 7-6. External interrupt line logic t...

Page 109

100 rabbit 3000 microprocessor 7.10.2 interrupt vectors: int0 - eir,0x00/int1 - eir,0x08 when it is desired to expand the number of interrupts for additional peripheral devices, the user should use the interrupt routine to dispatch interrupts to other virtual interrupt rou- tines. Each additional in...

Page 110

User’s manual 101 7.11 bootstrap operation the device provides the option of bootstrap from any of three sources: from the slave port, from serial port a in clocked serial mode, or from serial port a in asynchronous mode. This is controlled by the state of the smode pins after reset. Bootstrap opera...

Page 111

102 rabbit 3000 microprocessor serial port a is selected for bootstrap operation as a clocked serial port when smode = 10. In this case bit 7 of parallel port c is used for the serial data and bit 1 of parallel port b is used for the serial clock. Note that the serial clock must be externally suppli...

Page 112

User’s manual 103 7.12 pulse width modulator the pulse width modulator consists of a ten-bit free running counter, and four width reg- isters. Each pwm output is high for "n + 1" counts out of the 1024-clock count cycle, where "n" is the value held in the width register. The pwm output high time can...

Page 113

104 rabbit 3000 microprocessor table 7-17. Pwm lsb x register pwm lsb x register (pwl0r) (address = 0x88) (pwl1r) (address = 0x8a) (pwl2r) (address = 0x8c) (pwl3r) (address = 0x8e) bit(s) value description 7:6 write the least significant two bits for the pulse width modulator count are stored. 5:1 t...

Page 114

User’s manual 105 7.13 input capture the two-channel input capture can be used to time input signals from various port pins. Each input capture channel consists of a sixteen-bit counter that is clocked by the output of timer a8, and can be connected to one or two out of sixteen parallel port pins. T...

Page 115

106 rabbit 3000 microprocessor each input capture counter operates in one of three modes, or can be disabled. The counter is never automatically reset, but must be reset by a software command. Although it does not generate an interrupt, there is a status bit which is set when the counter over- flows...

Page 116

User’s manual 107 table 7-19. Input capture control/status register input capture control/status register (iccsr) (address = 0x56) bit(s) value description 7:2 (read) these status bits (but not the interrupt enable bits) are cleared by the read of this register, as is the input capture interrupt. 7 ...

Page 117

108 rabbit 3000 microprocessor table 7-20. Input capture control register input capture control register (iccr) (address = 0x57) bit(s) value description 7:2 these bits are ignored. 1:0 00 input capture interrupts are disabled. 01 input capture interrupt use interrupt priority 1. 10 input capture in...

Page 118

User’s manual 109 table 7-22. Input capture source x register input capture source x register (ics1r) (address = 0x59) (ics2r) (address = 0x5d) bit(s) value description 7:6 00 parallel port c used for start condition input. 01 parallel port d used for start condition input. 10 parallel port f used f...

Page 119

110 rabbit 3000 microprocessor 7.14 quadrature decoder the two-channel quadrature decoder accepts inputs, via port f, from two external optical incremental encoder modules. Each channel of the quadrature decoder accepts an in- phase (i) and a quadrature-phase (q) signal and provides 8-bit counters t...

Page 120

User’s manual 111 the quadrature decoder generates an interrupt when the counter increments from 0xff to 0x00 or when the counter decrements from 0x00 to 0xff. The timing for the interrupt is shown below. Note that the status bits in the qdcsr are set coincident with the interrupt, and the interrupt...

Page 121

112 rabbit 3000 microprocessor table 7-25. Quadrature decoder control/status register quad decode control/status register (qdcsr) (address = 0x90) bit(s) value description 7 0 quadrature decoder 2 did not increment from 0xff. (read-only) 1 quadrature decoder 2 incremented from 0xff to 0x00. This bit...

Page 122

User’s manual 113 table 7-26. Quadrature decoder control register quad decode control register (qdcr) (address = 0x91) bit(s) value description 7:6 00 disable quadrature decoder 2 inputs. Writing a new value to these bits will not cause quadrature decoder 2 to increment or decrement. 01 this bit com...

Page 123

114 rabbit 3000 microprocessor.

Page 124: 8. M

User’s manual 115 8. M emory i nterface and m apping 8.1 interface for static memory chips static memory chips generally have address lines, data line, a chip select line, an output enable line and a write enable. The rabbit 3000 has these same lines that can connect directly to a number of static m...

Page 125

116 rabbit 3000 microprocessor figure 8-2. Typical memory chip connection rabbit 3000 data lines (8) address lines (20) /cs /we /oe /cs0 /cs1 /cs2 /oe0 /oe1 /we0 /we1 static /cs /we /oe memory flash static memory ram.

Page 126

User’s manual 117 8.2 memory mapping overview see section 3.2, “memory mapping,” for a discussion of rabbit memory mapping. Figure 8-3 shows an overview of the rabbit memory mapping. The task of the memory mapping unit is to accept 16-bit addresses and translate them to 20-bit addresses. The memory ...

Page 127

118 rabbit 3000 microprocessor figure 8-4. Memory segments the memory management unit accepts a 16-bit address from the processor and translates it into a 20-bit address. The procedure to do this works as follows. 1. It is determined which segment the 16-bit address belongs to by inspecting the uppe...

Page 128

User’s manual 119 8.4 memory interface unit the 20-bit memory addresses generated by the memory-mapping unit feed into the mem- ory interface unit. The memory interface unit has a separate write-only control register for each 256k quadrant of the 1m physical memory. This control register specifies h...

Page 129

120 rabbit 3000 microprocessor 8.5 memory bank control registers table 8-3 describes the operation of the four memory bank control registers. The registers are write-only. Each register controls one quadrant in the 1m address space. Bits 7,6—the number of wait states used in access to this quadrant....

Page 130

User’s manual 121 bit 3—inhibits the write pulse to memory accessed in this quadrant. Useful for protecting flash mem- ory from an inadvertent write pulse, which will not actually write to the flash because it is protected by lock codes, but will temporarily disable the flash memory and crash the sy...

Page 131

122 rabbit 3000 microprocessor the memory timing control register (mtcr) enables the extended timing for the memory output enables and write enables. See figure 7-2 for details on how the timing of the mem- ory read and write strobes is affected when using the early output enable and write enable op...

Page 132

User’s manual 123 the breakpoint/debug controller allows the rst 28 instruction to be used as a software breakpoint. Normally the rst 28 instruction causes a call to a particular location in mem- ory, but the operation of this instruction is modified when the breakpoint/debug feature is enabled. The...

Page 133

124 rabbit 3000 microprocessor 8.7 instruction and data space support instruction and data space (i and d space) support is accomplished by optionally invert- ing address lines a16 and/or a19 when the processor accesses d space, but not inverting those lines when the processor accesses i space. The ...

Page 134

User’s manual 125 are mapped into contiguous regions of memory to create a continuous root code segment starting at the bottom of physical memory in flash. In the i space the division between the root segment and the data segment is irrelevant because the dataseg register contains zero and the divis...

Page 135

126 rabbit 3000 microprocessor figure 8-6. Use of physical memory separate i & d space model in figure 8-6 arrows indicate the direction in which variables and constants are allocated as the compile or assemble proceeds. Each of these arrows starts at a constant location in physical memory. This is ...

Page 136

User’s manual 127 8.8 how the compiler compiles to memory the compiler actually generates code for root code and constants and extended code and extended constants. It allocates space for data variables, but does not generate data bits to be stored in memory. In any but the smallest programs, most o...

Page 137

128 rabbit 3000 microprocessor.

Page 138: 9. P

User’s manual 129 9. P arallel p orts the rabbit has seven 8-bit parallel ports designated a, b, c, d, e, f, and g. The pins used for the parallel ports are also shared with numerous other functions as shown in table 5-2. The important properties of the ports are summarized below. • port a—shared wi...

Page 139

130 rabbit 3000 microprocessor 9.1 parallel port a parallel port a has a single read/write register: this register should not be used if the slave port or auxiliary i/o bus is enabled. The slave port control register is used to control whether parallel port a is configured as slave databus, auxiliar...

Page 140

User’s manual 131 9.2 parallel port b parallel port b, has eight pins that can programmed individually to be inputs and outputs. After reset, parallel port b comes up as six inputs (pb[5:0]) and two outputs (pb7 and pb6). The output value on pins pb6 and pb7 (package pins 99, 100) will be low. When ...

Page 141

132 rabbit 3000 microprocessor 9.3 parallel port c parallel port c, shown in table 9-6, has four inputs and four outputs. The even-numbered ports, pc0, pc2, pc4, and pc6, are outputs. The odd-numbered ports, pc1, pc3, pc5, and pc7, are inputs. When the data register is read, bits 1,3,5,7 return the ...

Page 142

User’s manual 133 9.4 parallel port d parallel port d, shown in figure 9-1, has eight pins that can be programmed individually to be inputs or outputs. When programmed as outputs, the pins can be individually selected to be open-drain outputs or standard outputs. Port d pins can be addressed by bit ...

Page 143

134 rabbit 3000 microprocessor figure 9-1. Parallel port d block diagram pd7 pd4 i/o data perclk/2 timer a1 timer b1 timer b2 perclk/2 timer a1 timer b1 timer b2 pd3 pd0 atxa atxb arxa arxb pd5 pd6 inputs driver—optional open drain.

Page 144

User’s manual 135 table 9-8. Parallel port d register functions bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 pddr (r/w) adr = 0x060 pd7 pd6 pd5 pd4 pd3 pd2 pd1 pd0 pddcr (w) adr = 0x066 out = open drain out = open drain out = open drain out = open drain out = open drain out = open drain out = ope...

Page 145

136 rabbit 3000 microprocessor the following registers are described in table 9-8 and in table 9-9. • pddr—parallel port d data register. Read/write. • pdddr—parallel port d data direction register. A "1" makes the corresponding pin an output. Write only. • pddcr—parallel port d drive control regist...

Page 146

User’s manual 137 9.5 parallel port e parallel port e, shown in figure 9-2, has eight i/o pins that can be individually pro- grammed as inputs or outputs. Pe7 is used as the slave port chip select when the slave port is enabled. Each of the port e outputs can be configured as an i/o strobe. In addit...

Page 147

138 rabbit 3000 microprocessor the following registers are described in table 9-11 and in table 9-12. • pedr—port e data register. Reads value at pins. Writes to port e preload register. • peddr—port e data direction register. Set to "1" to make corresponding pin an out- put. This register is zeroed...

Page 148

User’s manual 139 table 9-11. Parallel port e register functions bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 pedr (r/w) adr = 0x070 pe7 pe6 pe5 pe4 pe3 pe2 pe1 pe0 pefr (w) adr = 0x075 alt /i7 alt /i6 alt /i5 alt /i4 alt /i3 alt /i2 alt /i1 alt /i0 peddr (w) adr = 0x077 dir = out dir = out dir =...

Page 149

140 rabbit 3000 microprocessor 9.6 parallel port f parallel port f is a byte-wide port with each bit programmable for data direction and drive. These are simple inputs and outputs controlled and reported in the port f data register. As outputs, the bits of the port are buffered, with the data writte...

Page 150

User’s manual 141 the following registers are described in table 9-14 and in table 9-15. • pfdr—port f data register. Reads value at pins. Writes to port f preload register. • pfcr—parallel port f control register. This register is used to control the clocking of the upper and lower nibble of the fi...

Page 151

142 rabbit 3000 microprocessor the functionality of the parallel port f pins is not affected for pulse width modulation out- puts and serial clock outputs, except that the parallel port f function and direction regis- ters should be set up before a conflicting function on parallel port a is in use, ...

Page 152

User’s manual 143 9.7 parallel port g parallel port g is a byte-wide port with each bit programmable for data direction and drive. These are simple inputs and outputs controlled and reported in the port g data reg- ister. As outputs, the bits of the port are buffered, with the data written to the po...

Page 153

144 rabbit 3000 microprocessor the following registers are described in table 9-17 and in table 9-18. • pgdr—port g data register. Reads value at pins. Writes to port g preload register. • pgcr—parallel port g control register. This register is used to control the clocking of the upper and lower nib...

Page 154: 10. I/o B

User’s manual 145 10. I/o b ank c ontrol r egisters the pins of port e can be set individually to be i/o strobes. Each of the eight possible i/o strobes has a control register that controls the nature of the strobe and the number of wait states that will be inserted in the i/o bus cycle. Writes can ...

Page 155

146 rabbit 3000 microprocessor table 10-1 shows how the eight i/o bank control registers are organized. Table 10-1. I/o bank x control register i/o bank x control register (ib0cr) (address = 0x0080) (ib1cr) (address = 0x0081) (ib2cr) (address = 0x0082) (ib3cr) (address = 0x0083) (ib4cr) (address = 0...

Page 156

User’s manual 147 the eight i/o bank control registers determine the number of i/o wait states applied to an external i/o access within the zone controlled by each register even if the associated strobes are not enabled. Note that the /iord and /iowr signals reflect these registers as well. The cont...

Page 157

148 rabbit 3000 microprocessor.

Page 158: 11. T

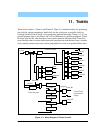

User’s manual 149 11. T imers there are two timers—timer a and timer b. Timer a is intended mainly for generating the clock for various peripherals, baud clock for the serial ports, a periodic clock for clocking parallel ports d and e, or for generating periodic interrupts. Timers a1–a7 are general-...

Page 159

150 rabbit 3000 microprocessor 11.1 timer a timer a consists of ten separate countdown timers a1–a10 as shown in figure 11-1. Timers a1 and a2–a10 are 8-bit countdown registers as shown in figure 11-2. The reload register can contain any number in the range from 0 to 255. The counter divides by (n+1...

Page 160

User’s manual 151 for seven of the counters (a1–a7), the terminal count condition is reported in a status regis- ter and can be programmed to generate an interrupt. There is one interrupt vector for timer a and a common interrupt priority. A common status register (tacsr) has a bit for each timer th...

Page 161

152 rabbit 3000 microprocessor the following table summarizes timer a’s capabilities. The control/status register for timer a (tacsr) is laid out as shown in table 11-3. Table 11-2. Timer a capabilities timer cascade interrupt dedicated connection a1 none yes parallel ports d-g, timer b a2 from a1 y...

Page 162

User’s manual 153 4 (write) 0 a4 interrupt disabled. 1 a4 interrupt enabled. 3 (read) 0 a3 counter has not reached its terminal count. 1 a3 count done. This status bit is cleared by a read of this register. 3 (write) 0 a3 interrupt disabled. 1 a3 interrupt enabled. 2 (read) 0 a2 counter has not reac...

Page 163

154 rabbit 3000 microprocessor the control register (tacr) is laid out as shown in table 11-4. The timer a prescale register (tapr) specifies the main clock for timer a. This will affect all of the timer a countdown timers. By default timer a is clocked by peripheral clock divided by two. The presca...

Page 164

User’s manual 155 the time constant register for each timer (tatxr) is simply an 8-bit data register holding a number between 0 and 255. This time constant will take effect the next time that the timer a counter counts down to zero. The timer counts modulo (divide-by) n+1, where n is the programmed ...

Page 165

156 rabbit 3000 microprocessor 11.2 timer b figure 11-1 shows a block diagram of timer b. The timer b counter can be driven directly by perclk/2, by that clock divided by 8, or by the output of timer a1. Timer b has a continuously running 10-bit counter. The counter is compared against two match reg...

Page 166

User’s manual 157 the control/status register for timer b (tbcsr) is laid out as shown in table 11-7. The control register for timer b (tbcr) is laid out as shown in table 11-8. Table 11-7. Timer b control and status register timer b control and status register (tbcsr) (address = 0x00b0) bit(s) valu...

Page 167

158 rabbit 3000 microprocessor the msb x registers for timer b (tbm1r/tbm2r) are laid out as shown in table 11-9. The lsb x registers for timer b (tbl1r/tbl2r) are laid out as shown in table 11-10. Table 11-9. Timer b count msb x registers timer b count msb x register (tbm1r) (address = 0xb2) (tbm2r...

Page 168

User’s manual 159 11.2.1 using timer b normally the prescaler is set to divide perclk/2 by a number that provides a counting rate appropriate to the problem. For example, if the clock is 22.1184 mhz, then perclk/2 is 11.0592 mhz. A timer b clock rate of 11.0592 mhz will cause a complete cycle of the...

Page 169

160 rabbit 3000 microprocessor timer b can be used for various purposes. The 10-bit counter can be read to record the time at which an event takes place. If the event creates an interrupt, the timer can be read in the interrupt routine. The known time of execution of the interrupt routine can be sub...

Page 170: 12. R

User’s manual 161 12. R abbit s erial p orts the rabbit 3000 has 6 on-chip serial ports designated a, b, c, d, e, and f. All the ports can per- form asynchronous serial communications at high baud rates. Ports a-d can operate as clocked ports. Ports a and b can be switched to alternate pins. Ports e...

Page 171

162 rabbit 3000 microprocessor figure 12-1 shows a block diagram of the serial ports. Figure 12-1. Block diagram of rabbit serial ports serial port f txf serial transmit out rxf serial transmit in tclkf optional external transmit clock rclkf optional external receive clock table 12-1. Serial port si...

Page 172

User’s manual 163 the individual serial ports are capable of operating at baud rates in excess of 500,000 bps in the asynchronous mode, and 8 times faster than that in the synchronous mode. Either 7 or 8 data bits may be transmitted and received in the asynchronous mode. The so-called "9th" bit or a...

Page 173

164 rabbit 3000 microprocessor 12.1 serial port register layout figure 12-2 shows a functional block diagram of a serial port. Each serial port has a data register, a control register and a status register. Writing to the data register starts transmis- sion. The least significant bit (lsb) is always...

Page 174

User’s manual 165 the clock input to the serial port unit must be 8 or 16 (selectable) times the baud rate in the asynchronous mode and 2 times the baud rate for the clocked serial mode when the internal clock is used. Timers a2–a7 supply the input clock for serial ports a–f. These timers can divide...

Page 175

166 rabbit 3000 microprocessor 12.2 serial port registers each serial port has 6 registers shown in the tables below. The status, control and extended registers may have somewhat different formats for different serial ports. Table 12-2. Serial port a registers register name mnemonic i/o address r/w ...

Page 176

User’s manual 167 table 12-5. Serial port d registers register name mnemonic i/o address r/w reset serial port d data register sddr 0xf0 r/w xxxxxxxx serial port d address register sdar 0xf1 w xxxxxxxx serial port d long stop register sdlr 0xf2 w xxxxxxxx serial port d status register sdsr 0xf3 r 0x...

Page 177

168 rabbit 3000 microprocessor table 12-8. Data register all ports serial port x data register (sadr) (address = 0xc0) (sbdr) (address = 0xd0) (scdr) (address = 0xe0) (sddr) (address = 0xf0) (sedr) (address = 0xc8) (sfdr) (address = 0xd8) bit(s) value description 7:0 read returns the contents of the...

Page 178

User’s manual 169 table 12-10. Long stop register all ports serial port x long stop register (salr) (address = 0xc2) (sblr) (address = 0xd2) (sclr) (address = 0xe2) (sdlr) (address = 0xf2) (selr) (address = 0xca) (sflr) (address = 0xda) bit(s) value description 7:0 read returns the contents of the r...

Page 179

170 rabbit 3000 microprocessor table 12-11. Status register asynchronous mode only (all ports) serial port x status register (sasr) (address = 0xc3) (sbsr) (address = 0xd3) (scsr) (address = 0xe3) (sdsr) (address = 0xf3) (sesr) (address = 0xcb) (sfsr) (address = 0xdb) bit(s) value description (async...

Page 180

User’s manual 171 table 12-12. Status register clocked serial (ports a-d only) serial port x status register (sasr) (address = 0xc3) (sbsr) (address = 0xd3) (scsr) (address = 0xe3) (sdsr) (address = 0xf3) bit(s) value description (clocked serial mode only) 7 0 the receive data register is empty 1 th...

Page 181

172 rabbit 3000 microprocessor table 12-13. Status register hdlc mode (ports e and f only) serial port x status register (sesr) (address = 0xcb) (sfsr) (address = 0xd3) bit(s) value description (hdlc mode only) 7 0 the receive data register is empty 1 there is a byte in the receive buffer. The seria...

Page 182

User’s manual 173 table 12-14. Serial port control register ports a and b serial port x control register (sacr) (address = 0xc4) (sbcr) (address = 0xd4) bit(s) value description 7:6 00 no operation. These bits are ignored in the async mode. 01 in clocked serial mode, start a byte receive operation. ...

Page 183

174 rabbit 3000 microprocessor table 12-15. Serial port control register ports c and d serial port x control register (sccr) (address = 0xe4) (sdcr) (address = 0xf4) bit(s) value description 7:6 00 no operation. These bits are ignored in the async mode. 01 in clocked serial mode, start a byte receiv...

Page 184

User’s manual 175 table 12-16. Serial port control register ports e and f serial port x control register (secr) (address = 0xcc) (sfcr) (address = 0xdc) bit(s) value description 7:6 00 no operation. These bits are ignored in the async mode. 01 in hdlc mode, force receiver in flag search mode. 10 no ...

Page 185

176 rabbit 3000 microprocessor table 12-17. Extended register asynchronous mode all ports serial port x extended register (saer) (address = 0xc5) (sber) (address = 0xd5) (scer) (address = 0xe5) (sder) (address = 0xf5) (seer) (address = 0xcd) (sfer) (address = 0xdd) bit(s) value description (async mo...

Page 186

User’s manual 177 table 12-18. Extended register clocked serial mode (ports a-d only) serial port x extended register (saer) (address = 0xc5) (sber) (address = 0xd5) (scer) (address = 0xe5) (sder) (address = 0xf5) bit(s) value description (clocked serial mode only) 7 0 normal clocked serial operatio...

Page 187

178 rabbit 3000 microprocessor table 12-19. Extended register hdlc mode (ports e and f only) serial port x extended register (seer) (address = 0xcd) (sfer) (address = 0xdd) bit(s) value description (hdlc mode only) 7:5 000 nrz data encoding for hdlc receiver and transmitter. 010 nrzi data encoding f...

Page 188

User’s manual 179 12.3 serial port interrupt a common interrupt vector is used for the receive and transmit interrupts. There is a sepa- rate interrupt request flip-flop for the receiver and transmitter. If either of these flip-flops is set, a serial port interrupt is requested. The flip-flops are s...

Page 189

180 rabbit 3000 microprocessor 12.4 transmit serial data timing on transmit, if the interrupts are enabled, an interrupt is requested when the transmit regis- ter becomes empty and, in addition, an interrupt occurs when the shift register and trans- mit register both become empty, that is, when the ...

Page 190

User’s manual 181 12.5 receive serial data timing when the receiver is ready to receive data, a falling edge indicates that a start bit must be detected. The falling edge is detected as a different rx input between two different clocks, the clock being 8x or 16x the baud rate. Once the start bit has...

Page 191

182 rabbit 3000 microprocessor 12.6 clocked serial ports ports a–d can operate in clocked mode. The data line and clock line are driven as shown in figure 12-4. The data and clock are provided as 8-bit bursts with the lsb shifted out and/or received first. By default the transmit shift register adva...

Page 192

User’s manual 183 with new incoming data. Similarly, writing the data to the sxar register causes the trans- mitter to start a byte transmit operation, eliminating the need for the software to issue the start transmit command. The effect of these codes is different, depending on whether the mode is ...

Page 193

184 rabbit 3000 microprocessor answer its interrupts within 20 µs. There will be no slow down if the receiver can answer its interrupt within 1/2 clock or 1.25 µs. If it can answer within 1.5 clocks, or 2.75 µs, the data rate will slow to 44,444 bytes per second. If it can answer in 2.5 clocks or 6....

Page 194

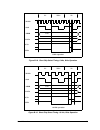

User’s manual 185 12.7 clocked serial timing 12.7.1 clocked serial timing with internal clock for synchronous serial communication, the serial clock can be either generated by the rabbit or by an external device. The timing diagram in figure 12-6 below can be applied to both full-duplex and half-dup...

Page 195

186 rabbit 3000 microprocessor figure 12-8 shows the timing relationship among perclk , the external serial clock, and data receive. Note that rxa is sampled by the rising edge of perclk . Figure 12-8. Synchronous serial data receive timing with external clock (mode 00) when clocking the rabbit exte...

Page 196

User’s manual 187 12.8 synchronous communications on ports e and f serial port e and f are a dual-function serial ports that can be used in either asynchronous or hdlc mode. Four bytes of buffering are available for both receiver and transmitter to reduce interrupt overhead. An interrupt is generate...

Page 197

188 rabbit 3000 microprocessor the current receive frame is not needed (because it is addressed to a different station, for example) a flag search command is available. This command forces the receiver to ignore the incoming data stream until another flag is received. In the transmitter, the crc gen...

Page 198

User’s manual 189 in hdlc mode the internal clock comes from the output of timer a2. This timer output is divided by sixteen to form the transmit clock, and is fed to the digital phase-locked loop (dpll) to form the receive clock. The dpll is basically just a divide-by-16 counter that uses the timin...

Page 199

190 rabbit 3000 microprocessor clock rate must be very small, and depends on the longest possible run of zeros in the received frame. Nrzi encoding guarantees at least one transition every six bits (with the inserted zeros). Since the dpll can adjust by two counts every bit cell, the maximum dif- fe...

Page 200

User’s manual 191 with nrz and nrzi encoding all transitions occur on bit-cell boundaries and the data should be sampled in the middle of the bit cell. If a transition occurs after the expected bit- cell boundary (but before the midpoint) the dpll needs to lengthen the count to line up the bit-cell ...

Page 201

192 rabbit 3000 microprocessor 12.9 serial port software suggestions the receiver and transmitter share the same interrupt vector, but it is possible to make the receive and transmit interrupt service routines (isrs) separate by dispatching the interrupt to either of two different routines. This is ...

Page 202

User’s manual 193 ld (hl),a ; 6 update the in pointer ioi ld a,(scdr) ; 11 get data register port c, clears interrupt request ipres ; 4 restore the interrupt priority ; 68 clocks to here ; to level before interrupt took place ; more interrupts could now take place, ; but receiver data is in register...

Page 203

194 rabbit 3000 microprocessor 2. Clear bit 4 of the parallel port c function register so that the output no longer comes from the serial port. Of course, this should not be done until the transmitter is idle. A similar procedure can be used if the serial port is set up to use alternate output pins ...

Page 204

User’s manual 195 figure 12-9 illustrates the standard asynchronous serial output patterns. Figure 12-9. Asynchronous serial output patterns 12.9.6 parity, extra stop bits with 7-data-bit characters if only 7 data bits are being sent, sending an additional parity or signal bit is easily solved by se...

Page 205

196 rabbit 3000 microprocessor 12.9.8 supporting 9th bit communication protocols this section describes how 9th bit communication protocols work. 9th bit communication protocols are supported by processors such as the 8051 and the z180, and by companies such as cimentrics technology. The data bytes ...

Page 206

User’s manual 197 the receiving interrupt service routine to detect this gap, it is suggested that dummy char- acters be transmitted to help detect the gap. This can be done in the following manner. The transmitter starts transmitting dummy characters when the first character interrupt is received. ...

Page 207

198 rabbit 3000 microprocessor.

Page 208: 13. R

User’s manual 199 13. R abbit s lave p ort when a rabbit microprocessor is configured as a slave, parallel port a and certain other data lines are used as communication lines between the slave and the master . The slave unit is a rabbit configured as a slave. The master can be another rabbit or any ...

Page 209: Slave Port Read Cycle

200 rabbit 3000 microprocessor a status register can be read by either the slave or the master. The status register has full/ empty bits for each of the six registers. A data register is considered full when it is written to by whichever side is capable of writing to it. If the same register is then...

Page 210

User’s manual 201 the following table explains the parameters used in figure 13-2. The two spd0r registers have special functionality not shared by the other data registers. If the master writes to spd0r, an inbound interrupt flip-flop is set. If slave port interrupts are enabled, the slave processo...

Page 211

202 rabbit 3000 microprocessor figure 13-3. Slave port handshaking and interrupts figure 13-4 shows a sample connection of two slave rabbits to a master rabbit. The mas- ter drives the slave reset line for both slaves and provides the main processor clock from its own clock. There is no requirement ...

Page 212

User’s manual 203 figure 13-4. Typical connection slave rabbit to master rabbit the slave port lines are shown in figure 13-1. The function of these lines is described below. • sd0–sd7—these are bidirectional data lines, and are generally connected to the data bus of the master processor. Multiple s...

Page 213

204 rabbit 3000 microprocessor • /slaveattn—this line is set low (asserted) if the slave writes to the spd0r register. This line is set high if the master writes anything to the slave status register. This line is usually connected to cause the master to be interrupted when it goes low. The data lin...

Page 214

User’s manual 205 if the user for some reason wants to depart from the suggested protocols and poll a register while waiting for the other side to write something to the register, the user should be aware that all the bits might not change at the exact same time when the result changes, and a transi...

Page 215

206 rabbit 3000 microprocessor bits 1,0—this 2-bit field sets the priority of the slave port interrupt. The interrupt is disabled by (0,0). Table 13-3 describes the slave port status register. The status register has 6 bits that are set if the particular register is full. That means that the registe...

Page 216

User’s manual 207 require a speciality processor. The slave processor can process data to perform pattern recognition or to extract a specific parameter from a data stream. 13.3.2 master-slave messaging protocol in this protocol the master sends messages to the slave and receives an acknowledgement ...

Page 217

208 rabbit 3000 microprocessor for this.) once the software is loaded into the slave, the slave can begin to perform its function. As a simple example, suppose that the slave is to be used as a four-port uart. It has the capability to send or receive characters on any of its four serial ports. Leavi...

Page 218: 14. R

User’s manual 209 14. R abbit 3000 c locks the rabbit 3000 normally uses two clocks, the main clock and the 32.768 khz clock. The 32.768 khz clock is needed for the battery-backable clock, the watchdog timer, and the cold-boot function. The main oscillator provides the run-time clock for the micropr...

Page 219

210 rabbit 3000 microprocessor 14.1 low-power design the power consumption is proportional to the clock frequency and to the square of the operating voltage. Thus, operating at 3.3 v instead of 5 v will reduce the power consump- tion by a factor of 10.9/25, or 43% of the power required at 5 v. The c...

Page 220: 15. Emi C

User’s manual 211 15. Emi c ontrol emi or electromagnetic interference from unintentional radiation is of concern to the microprocessor system designer. One concern is passing the tests sometimes required by the u.S. Federal communications commission (fcc) or by the european emc directive. For examp...

Page 221

212 rabbit 3000 microprocessor 15.1 power supply connections and board layout refer to technical note tn221, pc board layout suggestions for the rabbit 3000 microprocessor , for recommendations on laying out a pc board to minmize emi emsis- sions. 15.2 using the clock spectrum spreader the spectrum ...

Page 222

User’s manual 213 when the spectrum spreader is engaged, the frequency is modulated, and individual clock cycles may be shortened or lengthened by an amount that depends on whether the clock doubler is engaged and whether the spectrum spreader is set to the normal or strong set- ting. The frequency ...

Page 223

214 rabbit 3000 microprocessor so low as to be undetectable, except perhaps for extremely weak stations. The effect of a pure harmonic on tv reception is to create a herringbone pattern created by a harmonic falling within the station’s band. If the spreader is engaged the pattern will disappear unl...

Page 224: 16. Ac T

User’s manual 215 16. Ac t iming s pecifications the rabbit 3000 processor may be operated at voltages between 1.8 v and 3.6 v, and at temperatures from –40°c to +85°c with use possible use over the extended range -55°c to +105°c. For long life it is desirable not to exceed a die temperature of 125°...

Page 225

216 rabbit 3000 microprocessor figure 16-1 illustrates the parameters used to describe memory access time. Figure 16-1. Parameters used to describe memory access time table 16-2 lists the delays in gross memory access time for several values of v dd . When the spectrum spreader is enabled with the c...

Page 226

User’s manual 217 figure 16-2 and figure 16-3 illustrate the memory read and write cycles. The rabbit 3000 operates at 2 clocks per bus cycle plus any wait states that might be specified. Figure 16-2. Memory read and write cycles tadr tadr memory read (no wait states) clk a[19:0] memory write (no ex...

Page 227

218 rabbit 3000 microprocessor the following memory read time delays were measured. The measurements were taken at the 50% points under the following conditions. • t = -40°c to 85°c, v = 3.3 v • internal clock to nonloaded clk pin delay ≤ 1 ns @ 85°c/3.0 v the following memory write time delays were...

Page 228

User’s manual 219 figure 16-3. Memory read and write cycles—early output enable and write enable timing tadr tadr memory read (no wait states) clk a[19:0] memory write (no extra wait states) clk a[19:0] valid t1 t2 t1 tw t2 valid toex toex d[7:0] valid thold tsetup /csx /oex tcsx tcsx valid d[7:0] t...

Page 229

220 rabbit 3000 microprocessor figure 16-4 illustrates the sources that create memory access time delays. Figure 16-4. Sources of memory access time delays the gross memory access time is 2t, where t is the clock period. To calculate the actual memory access time, subtract the clock to address outpu...

Page 230

User’s manual 221 the required memory output enable access time is more complicated since it is affected by the clock doubler delays. The clock doubler setup register creates a nominal delay time ranging from 6 to 20 ns, resulting in a nominal clock low time ranging from 6 to 20 ns. The clock low ti...

Page 231

222 rabbit 3000 microprocessor the following factors have to be taken into account when calculating the output enable access time required. • the gross output enable access time is t + minimum clock low time (it is assumed that the early output enable option is enabled) this is reduced by the spectr...

Page 232

User’s manual 223 16.2 i/o access time figure 16-6 illustrates the i/o read and write cycles. Figure 16-6. I/o read and write cycles—no extra wait states note: /iocsx can be programmed to be active low (default) or active high. Tadr tadr external i/o read (no extra wait states) clk a[15:0] external ...

Page 233

224 rabbit 3000 microprocessor the following i/o read time delays were measured. The measurements were taken at the 50% points under the following conditions. • t = -40°c to 85°c, v = 3.3 v • internal clock to nonloaded clk pin delay ≤ 1 ns @ 85°c/3.0 v the following i/o write time delays were measu...

Page 234

User’s manual 225 16.3 further discussion of bus and clock timing the clock doubler is normally used, except in situations where low-frequency systems are specifically being used. The clock doubler works by oring the clock with a delayed ver- sion of itself. The nominal delay varies from 6 to 20 ns,...

Page 235

226 rabbit 3000 microprocessor figure 16-7. Clock doubler and memory timing oscillator oscillator delayed and inverted doubled clock delay time 48% 52% p 0.48p 0.52p 0.48p 0.52p data out example write cycle write pulse early write pulse option example read cycle address, /cs address, /cs output enb ...

Page 236

User’s manual 227 16.4 maximum clock speeds the rabbit 3000 is rated for a minimum clock period of 17 ns (commercial specifications) and 18 ns (industrial specifications). The commercial rating calls for a ±5% voltage varia- tion from 3.3 v and a temperature range from -40 to + 70°c. The industrial ...

Page 237

228 rabbit 3000 microprocessor example the spreader and doubler are enabled, with 8 ns nominal delay in the doubler. The high and low clock are equal to within 1 ns. This violates the duty cycle requirement by 3 ns since (clock low - clock high) can be as small as -1 ns, but the requirement is that ...

Page 238

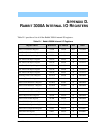

User’s manual 229 16.5 power and current consumption with the rabbit 3000 it is possible to design systems that perform their task with very low power consumption. Unlike competitive processors, the rabbit 3000 has short chip select features designed to minimize power consumption by external memorie...

Page 239

230 rabbit 3000 microprocessor figure 16-9. Rabbit 3000 system current vs. Frequency at 3.3 v figure 16-10. Rabbit 3000 system current vs. Frequency at 3.3 v (enlarged view over 0–16 mhz range) 0 20 40 60 80 100 120 0 10 20 30 40 50 60 clock frequency (mhz) i (ma ) xtal=25.80 xtal=14.74 xtal=11.05 x...

Page 240

User’s manual 231 lowering the operating voltage will greatly reduce current consumption and power. Drop- ping to 2.7 v from 3.3 v will result in 70% current consumption and 60% of the power. Further dropping to 1.8 v will reduce current to 40% and power to 20% compared to 3.3 v. Naturally this comp...

Page 241

232 rabbit 3000 microprocessor 16.6 current consumption mechanisms the following mechanisms contribute to the current consumption of the rabbit 3000 while it is operating. 1. A current proportional to voltage and clock frequency that results from the charging of internal and external capacitances. A...

Page 242

User’s manual 233 16.7 sleepy mode current consumption in sleepy mode the unit operates from the 32.768 khz clock, which may be divided down to as slow as 2.048 khz. The current consumption is given by: i total (µa) = 0.32 × v × f + 0.23 × v c × f + 5 × v c where f is in khz, v is the operating volt...

Page 243

234 rabbit 3000 microprocessor 16.8 memory current consumption since there are many different memories available, let’s look at an example using one of the recommended flash and sram memories. Flash memory —sst part sst39lf512020, 256k × 8, 45 ns access time. Standby current: nil. • static current (...

Page 244

User’s manual 235 16.9 battery-backed clock current consumption when using the suggested tiny logic oscillator, the oscillator and clock consume current as shown in figure 16-12 below. Normally a resistor is placed in the battery circuit to limit the current to about 3 µa, which results in a voltage...

Page 245

236 rabbit 3000 microprocessor 16.10 reduced-power external main oscillator the circuit in figure 16-13 can be used to generate the main clock using less power than with the built-in oscillator buffer. The power consumption is less because of the current- limiting resistors that cannot be used with ...

Page 246: 17. R

User’s manual 237 17. R abbit bios and v irtual d river when a program is compiled by dynamic c for a rabbit target, the virtual driver is auto- matically incorporated into the program. Virtual driver is the name given to some initial- ization routines and a group of services performed by the period...

Page 247

238 rabbit 3000 microprocessor 17.1.2 bios assumptions the bios makes certain assumptions concerning the physical configuration of the proces- sor. Processors are expected to have ram connected to /cs1, /we1, and /oe1. Flash is expected to be connected to /cs0, /we0, and /oe0. (see the rabbit 3000 d...

Page 248

User’s manual 239 gram consistency checking or because a part of the program that should be executing peri- odically is not executing and the watchdog times out. The virtual driver’s periodic interrupt hits the hardware watchdog timer with a 2 second time-out. If the periodic interrupt stops working...

Page 249

240 rabbit 3000 microprocessor.

Page 250: 18. O

User’s manual 241 18. O ther r abbit s oftware 18.1 power management support the power consumption and speed of operation can be throttled up and down with rough synchronism. This is done by changing the clock speed or the clock doubler. The range of control is quite wide: the speed can vary by a fa...

Page 251

242 rabbit 3000 microprocessor 18.2 reading and writing i/o registers the rabbit has two i/o spaces: internal i/o registers and external i/o registers. 18.2.1 using assembly language the fastest way to read and write i/o registers in dynamic c is to use a short segment of assembly language inserted ...

Page 252

User’s manual 243 18.3 shadow registers many of the registers of the rabbit’s internal i/o devices are write-only. This saves gates on the chip, making possible greater capability at lower cost. Write-only registers are eas- ier to use if a memory location, called a shadow register, is associated wi...

Page 253

244 rabbit 3000 microprocessor ld hl,pdddrshadow ; point to shadow register ld de,pdddr ; set de to point to i/o reg set 5,(hl) ; set bit 5 of shadow register ; use ldd instruction for atomic transfer ioi ldd ; (io de) in this case, the ldd instruction when used with an i/o prefix provides a conveni...

Page 254

User’s manual 245 two library functions are provided to read and write the real-time clock: unsigned long int read_rtc(void) ; // read bits 15-46 rtc void write_rtc(unsigned long int time) ; // write bits 15-46 // note: bits 0-14 and bit 47 are zeroed however, it is not intended that the real-time c...

Page 255

246 rabbit 3000 microprocessor.

Page 256: 19. R

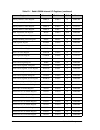

User’s manual 247 19. R abbit i nstructions summary “load immediate data” on page 250 “load & store to immediate address” on page 250 “8-bit indexed load and store” on page 250 “16-bit indexed loads and stores” on page 250 “16-bit load and store 20-bit address” on page 251 “register to register move...

Page 257

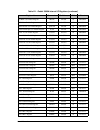

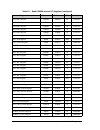

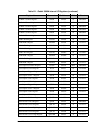

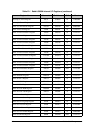

248 rabbit 3000 microprocessor spreadsheet conventions altd (“a” column) symbol key ioi and ioe (“i” column) symbol key flag register key flag description f altd selects alternate flags fr altd selects alternate flags and register r altd selects alternate register s altd operation is a special case ...

Page 258