- DL manuals

- NEC

- Microcontrollers

- 78K/0 Series

- User Manual

NEC 78K/0 Series User Manual

Summary of 78K/0 Series

Page 1

User’s manual printed in japan © 78k/0 series instructions document no. U12326ej4v0um00 (4th edition) date published october 2001 n cp(k) 1995 common to 78k/0 series.

Page 2

2 user's manual u12326ej4v0um [memo].

Page 3

3 user's manual u12326ej4v0um caution: purchase of nec i 2 c components conveys a license under the philips i 2 c patent rights to use these components in an i 2 c system, provided that the system conforms to the i 2 c standard specification as defined by philips. Iebus is a trademark of nec corpora...

Page 4

4 user's manual u12326ej4v0um the export of these products from japan is regulated by the japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than japan may also be ...

Page 5: Regional Information

5 user's manual u12326ej4v0um regional information some information contained in this document may vary from country to country. Before using any nec product in your application, piease contact the nec office in your country to obtain a list of authorized representatives and distributors. They will ...

Page 6

6 user's manual u12326ej4v0um major revisions in this edition page description throughout deletion of all information except for information common to the 78k/0 series (for individual product information, refer to the user’s manual of each product). The mark shows major revised points..

Page 7

7 user's manual u12326ej4v0um introduction target readers this manual is intended for users who wish to understand the functions of 78k/0 series products and to design and develop its application systems and programs. Purpose this manual is intended to give users an understanding of the various kind...

Page 8

8 user's manual u12326ej4v0um related documents the related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such. • documents common to 78k/0 series document name document no. User’s manual instructions this manual application...

Page 9

9 user's manual u12326ej4v0um contents chapter 1 memory space ............................................................................................................... 12 1.1 memory spaces ............................................................................................................

Page 10

10 user's manual u12326ej4v0um chapter 5 explanation of instructions ................................................................................. 46 5.1 8-bit data transfer instructions ...................................................................................... 48 5.2 16-bit data tra...

Page 11

11 user's manual u12326ej4v0um list of figures figure no. Title page 2-1 program counter configuration .............................................................................................................. 14 2-2 program status word configuration ................................................

Page 12

12 user's manual u12326ej4v0um chapter 1 memory space 1.1 memory spaces the 78k/0 series product program memory map varies depending on the internal memory capacity. For details of memory-mapped address area, refer to the user’s manual of each product. 1.2 internal program memory (internal rom) spac...

Page 13

13 chapter 1 memory space user's manual u12326ej4v0um (3) ram for vfd display there are some products in the 78k/0 series to which ram for vfd display is allocated. This ram can also be used as an ordinary ram area. (4) internal expansion ram there are some products in the 78k/0 series to which inte...

Page 14

14 user's manual u12326ej4v0um chapter 2 registers 2.1 control registers the control registers control the program sequence, statuses and stack memory. A program counter, a program status word and a stack pointer are the control registers. 2.1.1 program counter (pc) the program counter is a 16-bit r...

Page 15

15 chapter 2 registers user's manual u12326ej4v0um (1) interrupt enable flag (ie) this flag controls the interrupt request acknowledgement operations of the cpu. When ie = 0, the ie flag is set to interrupt disable (di), and interrupts other than non-maskable interrupts are all disabled. When ie = 1...

Page 16

16 chapter 2 registers user's manual u12326ej4v0um interrupt and brk instructions psw pc15-pc8 pc15-pc8 pc7-pc0 lower half register pairs sp sp _ 2 sp _ 2 call, callf and callt instructions push rp instruction sp _ 1 sp sp sp _ 2 sp _ 2 sp _ 1 sp pc7-pc0 sp _ 3 sp _ 2 sp _ 1 sp sp sp _ 3 upper half ...

Page 17

17 chapter 2 registers user's manual u12326ej4v0um 2.2 general-purpose registers general-purpose registers are mapped at particular addresses (fee0h to feffh) of the data memory. These registers consist of 4 banks, each bank consisting of eight 8-bit registers (x, a, c, b, e, d, l and h). In additio...

Page 18

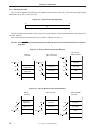

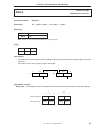

18 chapter 2 registers user's manual u12326ej4v0um figure 2-6. General-purpose register configuration (a) absolute names (b) functional names bank0 bank1 bank2 bank3 feffh fee0h r0 15 0 7 0 16-bit processing 8-bit processing fee7h rp3 rp2 rp1 rp0 r1 r2 r3 r4 r5 r6 r7 fee8h feefh fef0h fef7h fef8h ba...

Page 19

19 chapter 2 registers user's manual u12326ej4v0um 2.3 special function registers (sfrs) unlike a general-purpose register, each special-function register has a special function. Special function registers are allocated in the 256-byte area ff00h to ffffh. Special function registers can be manipulat...

Page 20

20 user's manual u12326ej4v0um chapter 3 addressing 3.1 instruction address addressing an instruction address is determined by program counter (pc) contents. The pc contents are normally incremented (+1 for each byte) automatically according to the number of bytes of an instruction to be fetched eac...

Page 21

21 chapter 3 addressing user's manual u12326ej4v0um 15 0 pc 8 7 7 0 fa 10 to fa 8 11 10 0 0 0 0 1 6 4 3 callf fa 7 to fa 0 3.1.2 immediate addressing [function] immediate data in the instruction word is transferred to the program counter (pc) and branched. This function is carried out when the “call...

Page 22

22 chapter 3 addressing user's manual u12326ej4v0um 15 1 15 0 pc 7 0 low addr. High addr. Memory (table) effective address+1 effective address 0 1 0 0 0 0 0 0 0 0 8 7 8 7 6 5 0 0 1 1 1 7 6 5 1 0 ta 4–0 instruction code 3.1.3 table indirect addressing [function] table contents (branch destination add...

Page 23

23 chapter 3 addressing user's manual u12326ej4v0um 3.1.4 register addressing [function] the register pair (ax) contents to be specified by an instruction word are transferred to the program counter (pc) and branched. This function is carried out when the “br ax” instruction is executed. [illustrati...

Page 24

24 chapter 3 addressing user's manual u12326ej4v0um 3.2 operand address addressing the following methods are available to specify the register and memory (addressing) to undergo manipulation during instruction execution. 3.2.1 implied addressing [function] this addressing automatically specifies the...

Page 25

25 chapter 3 addressing user's manual u12326ej4v0um 3.2.2 register addressing [function] register addressing accesses a general-purpose register as an operand. The general-purpose register to be accessed is specified by the register bank selection flags (rbs0 and rbs1) and the register specification...

Page 26

26 chapter 3 addressing user's manual u12326ej4v0um 3.2.3 direct addressing [function] direct addressing directly addresses the memory indicated by the immediate data in the instruction word. [operand format] identifier description addr16 label or 16-bit immediate data [description example] mov a, !...

Page 27

27 chapter 3 addressing user's manual u12326ej4v0um 15 0 short direct memory effective address 1 1 1 1 1 1 1 8 7 0 7 op code saddr-offset α when 8-bit immediate data is 20h to ffh, α = 0. When 8-bit immediate data is 00h to 1fh, α = 1. 3.2.4 short direct addressing [function] the memory to be manipu...

Page 28

28 chapter 3 addressing user's manual u12326ej4v0um 15 0 sfr effective address 1 1 1 1 1 1 1 8 7 0 7 op code sfr-offset 1 3.2.5 special-function register (sfr) addressing [function] a memory-mapped special function register (sfr) is addressed with 8-bit immediate data in an instruction word. This ad...

Page 29

29 chapter 3 addressing user's manual u12326ej4v0um 15 0 8 d 7 e 0 7 7 0 a de memory memory address specified by register pair de contents of memory to be addressed are transferred 3.2.6 register indirect addressing [function] register indirect addressing addresses memory with register pair contents...

Page 30

30 chapter 3 addressing user's manual u12326ej4v0um 3.2.7 based addressing [function] 8-bit immediate data is added to the contents of the hl register pair as a base register and the sum is used to address the memory. The hl register pair to be accessed is in the register bank specified by the regis...

Page 31

31 chapter 3 addressing user's manual u12326ej4v0um 3.2.9 stack addressing [function] the stack area is indirectly addressed with the stack pointer (sp) contents. This addressing method is automatically employed when the push, pop, subroutine call and return instructions are executed or the register...

Page 32

32 user's manual u12326ej4v0um chapter 4 instruction set this chapter lists the instructions in the 78k/0 series instruction set. The instructions are common to all 78k/0 series products. 4.1 operation for the operation list for each product, refer to the user’s manual of each product. 4.1.1 operand...

Page 33

33 chapter 4 instruction set user's manual u12326ej4v0um 4.1.2 description of “operation” column a: a register; 8-bit accumulator x: x register b: b register c: c register d: d register e: e register h: h register l: l register ax: ax register pair; 16-bit accumulator bc: bc register pair de: de reg...

Page 34

34 chapter 4 instruction set user's manual u12326ej4v0um 4.1.4 description of number of clocks 1 instruction clock cycle is 1 cpu clock cycle (f cpu ) selected by the processor clock control register (pcc). 4.1.5 instructions listed by addressing type (1) 8-bit instructions mov, xch, add, addc, sub,...

Page 35

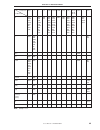

35 chapter 4 instruction set user's manual u12326ej4v0um 2nd operand #byte a r note sfr saddr !Addr16 psw [de] [hl] [hl+byte] $addr16 1 none [hl+b] 1st operand [hl+c] a add mov mov mov mov mov mov mov mov ror addc xch xch xch xch xch xch xch rol sub add add add add add rorc subc addc addc addc addc ...

Page 36

36 chapter 4 instruction set user's manual u12326ej4v0um 2nd operand a.Bit sfr.Bit saddr.Bit psw.Bit [hl].Bit cy $addr16 none 1st operand a.Bit mov1 bt set1 bf clr1 btclr sfr.Bit mov1 bt set1 bf clr1 btclr saddr.Bit mov1 bt set1 bf clr1 btclr psw.Bit mov1 bt set1 bf clr1` btclr [hl].Bit mov1 bt set1...

Page 37

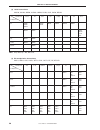

37 chapter 4 instruction set user's manual u12326ej4v0um (4) call instructions/branch instructions call, callf, callt, br, bc, bnc, bz, bnz, bt, bf, btclr, dbnz 2nd operand ax !Addr16 !Addr11 [addr5] $addr16 1st operand basic instructions br call callf callt br br bc bnc bz bnz compound instructions...

Page 38

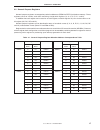

38 chapter 4 instruction set user's manual u12326ej4v0um 4.2 instruction codes 4.2.1 description of instruction code table r rp rb r 2 r 1 r 0 reg p 1 p 0 reg-pair rb 1 rb 0 reg-bank 0 0 0 r0 x 0 0 rp0 ax 0 0 rb0 0 0 1 r1 a 0 1 rp1 bc 0 1 rb1 0 1 0 r2 c 1 0 rp2 de 1 0 rb2 0 1 1 r3 b 1 1 rp3 hl 1 1 r...

Page 39

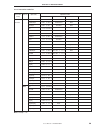

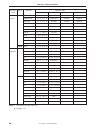

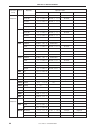

39 chapter 4 instruction set user's manual u12326ej4v0um 4.2.2 instruction code list instruction mnemonic operands operation code group b1 b2 b3 b4 8-bit data mov r,#byte 1 0 1 0 0 r 2 r 1 r 0 data transfer saddr,#byte 0 0 0 1 0 0 0 1 saddr-offset data sfr,#byte 0 0 0 1 0 0 1 1 sfr-offset data a,r n...

Page 40

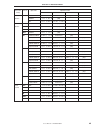

40 chapter 4 instruction set user's manual u12326ej4v0um 16-bit data movw rp,#word 0 0 0 1 0 p 1 p 0 0 low byte high byte transfer saddrp,#word 1 1 1 0 1 1 1 0 saddr-offset low byte high byte sfrp,#word 1 1 1 1 1 1 1 0 sfr-offset low byte high byte ax,saddrp 1 0 0 0 1 0 0 1 saddr-offset saddrp,ax 1 ...

Page 41

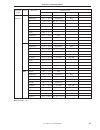

41 chapter 4 instruction set user's manual u12326ej4v0um 8-bit sub a,#byte 0 0 0 1 1 1 0 1 data operation saddr,#byte 1 0 0 1 1 0 0 0 saddr-offset data a,r note 0 1 1 0 0 0 0 1 0 0 0 1 1 r 2 r 1 r 0 r,a 0 1 1 0 0 0 0 1 0 0 0 1 0 r 2 r 1 r 0 a,saddr 0 0 0 1 1 1 1 0 saddr-offset a,!Addr16 0 0 0 1 1 0 ...

Page 42

42 chapter 4 instruction set user's manual u12326ej4v0um 8-bit or a,#byte 0 1 1 0 1 1 0 1 data operation saddr,#byte 1 1 1 0 1 0 0 0 saddr-offset data a,r note 0 1 1 0 0 0 0 1 0 1 1 0 1 r 2 r 1 r 0 r,a 0 1 1 0 0 0 0 1 0 1 1 0 0 r 2 r 1 r 0 a,saddr 0 1 1 0 1 1 1 0 saddr-offset a,!Addr16 0 1 1 0 1 0 0...

Page 43

43 chapter 4 instruction set user's manual u12326ej4v0um 16-bit addw ax,#word 1 1 0 0 1 0 1 0 low byte high byte operation subw ax,#word 1 1 0 1 1 0 1 0 low byte high byte cmpw ax,#word 1 1 1 0 1 0 1 0 low byte high byte multiply/ mulu x 0 0 1 1 0 0 0 1 1 0 0 0 1 0 0 0 divide divuw c 0 0 1 1 0 0 0 1...

Page 44

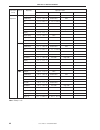

44 chapter 4 instruction set user's manual u12326ej4v0um bit or1 cy,saddr.Bit 0 1 1 1 0 0 0 1 0 b 2 b 1 b 0 0 1 1 0 saddr-offset manipulation cy,sfr.Bit 0 1 1 1 0 0 0 1 0 b 2 b 1 b 0 1 1 1 0 sfr-offset cy,a.Bit 0 1 1 0 0 0 0 1 1 b 2 b 1 b 0 1 1 1 0 cy,psw.Bit 0 1 1 1 0 0 0 1 0 b 2 b 1 b 0 0 1 1 0 0 ...

Page 45

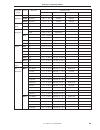

45 chapter 4 instruction set user's manual u12326ej4v0um unconditional br !Addr16 1 0 0 1 1 0 1 1 low addr high addr branch $addr16 1 1 1 1 1 0 1 0 jdisp ax 0 0 1 1 0 0 0 1 1 0 0 1 1 0 0 0 conditional bc $addr16 1 0 0 0 1 1 0 1 jdisp branch bnc $addr16 1 0 0 1 1 1 0 1 jdisp bz $addr16 1 0 1 0 1 1 0 ...

Page 46

46 user's manual u12326ej4v0um chapter 5 explanation of instructions this chapter explains the instructions of 78k/0 series products. Each instruction is described with a mnemonic, including description of multiple operands. The basic configuration of instruction description is shown on the next pag...

Page 47: Mov

47 chapter 5 explanation of instructions user's manual u12326ej4v0um description example mnemonic full name move mov byte data transfer meaning of instruction [instruction format] mov dst, src: indicates the basic description format of the instruction. [operation] dst ← src: indicates instruction op...

Page 48

48 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.1 8-bit data transfer instructions the following instructions are 8-bit data transfer instructions. Mov ... 49 xch ... 50

Page 49: Mov

49 chapter 5 explanation of instructions user's manual u12326ej4v0um move mov byte data transfer [instruction format] mov dst, src [operation] dst ← src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) mov r, #byte mov a, psw saddr, #byte psw, a sfr, #byte a, [de] a, r note [de], a r, a...

Page 50: Xch

50 chapter 5 explanation of instructions user's manual u12326ej4v0um exchange xch byte data exchange [instruction format] xch dst, src [operation] dst ↔ src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) xch a, r note xch a, [hl] a, saddr a, [hl+byte] a, sfr a, [hl+b] a, !Addr16 a, [h...

Page 51

51 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.2 16-bit data transfer instructions the following instructions are 16-bit data transfer instructions. Movw ... 52 xchw ... 53.

Page 52: Movw

52 chapter 5 explanation of instructions user's manual u12326ej4v0um move word movw word data transfer [instruction format] movw dst, src [operation] dst ← src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) movw rp, #word movw sfrp, ax saddrp, #word ax, rp note sfrp, #word rp, ax note...

Page 53: Xchw

53 chapter 5 explanation of instructions user's manual u12326ej4v0um exchange word xchw word data exchange [instruction format] xchw dst, src [operation] dst ↔ src [operand] mnemonic operand(dst,src) xchw ax, rp note note only when rp = bc, de or hl [flag] z ac cy [description] • the 1st and 2nd ope...

Page 54

54 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.3 8-bit operation instructions the following are 8-bit operation instructions. Add ... 55 addc ... 56 sub ... 57 subc ... 58 and ... 59 or ... 60 xor ... 61 cmp ... 62.

Page 55: Add

55 chapter 5 explanation of instructions user's manual u12326ej4v0um add add byte data addition [instruction format] add dst, src [operation] dst, cy ← dst + src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) add a, #byte add a, !Addr16 saddr, #byte a, [hl] a, r note a, [hl+byte] r, a...

Page 56: Addc

56 chapter 5 explanation of instructions user's manual u12326ej4v0um add with carry addc addition of byte data with carry [instruction format] addc dst, src [operation] dst, cy ← dst + src + cy [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) addc a, #byte addc a, !Addr16 saddr, #byte a...

Page 57: Sub

57 chapter 5 explanation of instructions user's manual u12326ej4v0um subtract sub byte data subtraction [instruction format] sub dst, src [operation] dst, cy ← dst – src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) sub a, #byte sub a, !Addr16 saddr, #byte a, [hl] a, r note a, [hl+by...

Page 58: Subc

58 chapter 5 explanation of instructions user's manual u12326ej4v0um subtract with carry subc subtraction of byte data with carry [instruction format] subc dst, src [operation] dst, cy ← dst – src – cy [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) subc a, #byte subc a, !Addr16 saddr,...

Page 59: and

59 chapter 5 explanation of instructions user's manual u12326ej4v0um and and logical product of byte data [instruction format] and dst, src [operation] dst ← dst ∧ src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) and a, #byte and a, !Addr16 saddr, #byte a, [hl] a, r note a, [hl+byte...

Page 60

60 chapter 5 explanation of instructions user's manual u12326ej4v0um or or logical sum of byte data [instruction format] or dst, src [operation] dst ← dst ∨ src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) or a, #byte or a, !Addr16 saddr, #byte a, [hl] a, r note a, [hl+byte] r, a a,...

Page 61: Xor

61 chapter 5 explanation of instructions user's manual u12326ej4v0um exclusive or xor exclusive logical sum of byte data [instruction format] xor dst, src [operation] dst ← dst ∨ src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) xor a, #byte xor a, !Addr16 saddr, #byte a, [hl] a, r n...

Page 62: Cmp

62 chapter 5 explanation of instructions user's manual u12326ej4v0um compare cmp byte data comparison [instruction format] cmp dst, src [operation] dst – src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) cmp a, #byte cmp a, !Addr16 saddr, #byte a, [hl] a, r note a, [hl+byte] r, a a, ...

Page 63

63 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.4 16-bit operation instructions the following are 16-bit operation instructions. Addw ... 64 subw ... 65 cmpw ... 66.

Page 64: Addw

64 chapter 5 explanation of instructions user's manual u12326ej4v0um add word addw word data addition [instruction format] addw dst, src [operation] dst, cy ← dst + src [operand] mnemonic operand(dst,src) addw ax, #word [flag] z ac cy × × × [description] • the destination operand (dst) specified by ...

Page 65: Subw

65 chapter 5 explanation of instructions user's manual u12326ej4v0um subtract word subw word data subtraction [instruction format] subw dst, src [operation] dst, cy ← dst – src [operand] mnemonic operand(dst,src) subw ax, #word [flag] z ac cy × × × [description] • the source operand (src) specified ...

Page 66: Cmpw

66 chapter 5 explanation of instructions user's manual u12326ej4v0um compare word cmpw word data comparison [instruction format] cmpw dst, src [operation] dst – src [operand] mnemonic operand(dst,src) cmpw ax, #word [flag] z ac cy × × × [description] • the source operand (src) specified by the 2nd o...

Page 67

67 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.5 multiply/divide instructions the following are multiply/divide instructions. Mulu ... 68 divuw ... 69.

Page 68: Mulu

68 chapter 5 explanation of instructions user's manual u12326ej4v0um multiply unsigned mulu unsigned multiplication of data [instruction format] mulu src [operation] ax ← a × src [operand] mnemonic operand(src) mulu x [flag] z ac cy [description] • the a register contents and the source operand (src...

Page 69: Divuw

69 chapter 5 explanation of instructions user's manual u12326ej4v0um divide unsigned word divuw unsigned division of word data [instruction format] divuw dst [operation] ax (quotient), dst (remainder) ← ax ÷ dst [operand] mnemonic operand(dst) divuw c [flag] z ac cy [description] • the ax register c...

Page 70

70 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.6 increment/decrement instructions the following are increment/decrement instructions. Inc ... 71 dec ... 72 incw ... 73 decw ... 74.

Page 71: Inc

71 chapter 5 explanation of instructions user's manual u12326ej4v0um increment inc byte data increment [instruction format] inc dst [operation] dst ← dst + 1 [operand] mnemonic operand(dst) inc r saddr [flag] z ac cy × × [description] • the destination operand (dst) contents are incremented by only ...

Page 72: Dec

72 chapter 5 explanation of instructions user's manual u12326ej4v0um decrement dec byte data decrement [instruction format] dec dst [operation] dst ← dst – 1 [operand] mnemonic operand(dst) dec r saddr [flag] z ac cy × × [description] • the destination operand (dst) contents are decremented by only ...

Page 73: Incw

73 chapter 5 explanation of instructions user's manual u12326ej4v0um increment word incw word data increment [instruction format] incw dst [operation] dst ← dst + 1 [operand] mnemonic operand(dst) incw rp [flag] z ac cy [description] • the destination operand (dst) contents are incremented by only o...

Page 74: Decw

74 chapter 5 explanation of instructions user's manual u12326ej4v0um decrement word decw word data decrement [instruction format] decw dst [operation] dst ← dst – 1 [operand] mnemonic operand (dst) decw rp [flag] z ac cy [description] • the destination operand (dst) contents are decremented by only ...

Page 75

75 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.7 rotate instructions the following are rotate instructions. Ror ... 76 rol ... 77 rorc ... 78 rolc ... 79 ror4 ... 80 rol4 ... 81.

Page 76: Ror

76 chapter 5 explanation of instructions user's manual u12326ej4v0um rotate right ror byte data rotation to the right [instruction format] ror dst, cnt [operation] (cy, dst 7 ← dst 0 , dst m–1 ← dst m ) × one time [operand] mnemonic operand(dst,cnt) ror a, 1 [flag] z ac cy × [description] • the dest...

Page 77: Rol

77 chapter 5 explanation of instructions user's manual u12326ej4v0um rotate left rol byte data rotation to the left [instruction format] rol dst, cnt [operation] (cy, dst 0 ← dst 7 , dst m+1 ← dst m ) × one time [operand] mnemonic operand(dst,cnt) rol a, 1 [flag] z ac cy × [description] • the destin...

Page 78: Rorc

78 chapter 5 explanation of instructions user's manual u12326ej4v0um rotate right with carry rorc byte data rotation to the right with carry [instruction format] rorc dst, cnt [operation] (cy ← dst 0 , dst 7 ← cy, dst m–1 ← dst m ) × one time [operand] mnemonic operand(dst,cnt) rorc a, 1 [flag] z ac...

Page 79: Rolc

79 chapter 5 explanation of instructions user's manual u12326ej4v0um rotate left with carry rolc byte data rotation to the left with carry [instruction format] rolc dst, cnt [operation] (cy ← dst 7 , dst 0 ← cy, dst m+1 ← dst m ) × one time [operand] mnemonic operand(dst,cnt) rolc a, 1 [flag] z ac c...

Page 80: Ror4

80 chapter 5 explanation of instructions user's manual u12326ej4v0um rotate right digit ror4 digit rotation to the right [instruction format] ror4 dst [operation] a 3-0 ← (dst) 3-0 , (dst) 7-4 ← a 3-0 , (dst) 3-0 ← (dst) 7-4 [operand] mnemonic operand(dst) ror4 [hl] note note specify an area other t...

Page 81: Rol4

81 chapter 5 explanation of instructions user's manual u12326ej4v0um rotate left digit rol4 digit rotation to the left [instruction format] rol4 dst [operation] a 3-0 ← (dst) 7-4 , (dst) 3-0 ← a 3-0 , (dst) 7-4 ← (dst) 3-0 [operand] mnemonic operand(dst) rol4 [hl] note note specify an area other tha...

Page 82

82 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.8 bcd adjust instructions the following are bcd adjust instructions. Adjba ... 83 adjbs ... 84.

Page 83: Adjba

Chapter 5 explanation of instructions 83 user's manual u12326ej4v0um decimal adjust register for addition adjba decimal adjustment of addition result [instruction format] adjba [operation] decimal adjust accumulator for addition [operand] none [flag] z ac cy × × × [description] • the a register, cy ...

Page 84: Adjbs

84 chapter 5 explanation of instructions user's manual u12326ej4v0um decimal adjust register for subtraction adjbs decimal adjustment of subtraction result [instruction format] adjbs [operation] decimal adjust accumulator for subtraction [operand] none [flag] z ac cy × × × [description] • the a regi...

Page 85

Chapter 5 explanation of instructions 85 user's manual u12326ej4v0um 5.9 bit manipulation instructions the following are bit manipulation instructions. Mov1 ... 86 and1 ... 87 or1 ... 88 xor1 ... 89 set1 ... 90 clr1 ... 91 not1 ... 92.

Page 86: Mov1

86 chapter 5 explanation of instructions user's manual u12326ej4v0um move single bit mov1 1 bit data transfer [instruction format] mov1 dst, src [operation] dst ← src [operand] mnemonic operand(dst,src) mnemonic operand(dst,src) mov1 cy, saddr.Bit mov1 saddr.Bit, cy cy, sfr.Bit sfr.Bit, cy cy, a.Bit...

Page 87: And1

Chapter 5 explanation of instructions 87 user's manual u12326ej4v0um and single bit and1 1 bit data logical product [instruction format] and1 dst, src [operation] dst ← dst ∧ src [operand] mnemonic operand(dst,src) and1 cy, saddr.Bit cy, sfr.Bit cy, a.Bit cy, psw.Bit cy, [hl].Bit [flag] z ac cy × [d...

Page 88: Or1

88 chapter 5 explanation of instructions user's manual u12326ej4v0um or single bit or1 1 bit data logical sum [instruction format] or1 dst, src [operation] dst ← dst ∨ src [operand] mnemonic operand(dst,src) or1 cy, saddr.Bit cy, sfr.Bit cy, a.Bit cy, psw.Bit cy, [hl].Bit [flag] z ac cy × [descripti...

Page 89: Xor1

Chapter 5 explanation of instructions 89 user's manual u12326ej4v0um exclusive or single bit xor1 1 bit data exclusive logical sum [instruction format] xor1 dst, src [operation] dst ← dst ∨ src [operand] mnemonic operand(dst,src) xor1 cy, saddr.Bit cy, sfr.Bit cy, a.Bit cy, psw.Bit cy, [hl].Bit [fla...

Page 90: Set1

90 chapter 5 explanation of instructions user's manual u12326ej4v0um set single bit (carry flag) set1 1 bit data set [instruction format] set1 dst [operation] dst ←1 [operand] mnemonic operand(dst) set1 saddr.Bit sfr.Bit a.Bit psw.Bit [hl].Bit cy [flag] dst = psw.Bit dst = cy in all other cases z ac...

Page 91: Clr1

Chapter 5 explanation of instructions 91 user's manual u12326ej4v0um clear single bit (carry flag) clr1 1 bit data clear [instruction format] clr1 dst [operation] dst ← 0 [operand] mnemonic operand(dst) clr1 saddr.Bit sfr.Bit a.Bit psw.Bit [hl].Bit cy [flag] dst = psw.Bit dst = cy in all other cases...

Page 92: Not1

92 chapter 5 explanation of instructions user's manual u12326ej4v0um not single bit (carry flag) not1 1 bit data logical negation [instruction format] not1 dst [operation] dst ← dst [operand] mnemonic operand(dst) not1 cy [flag] z ac cy × [description] • the cy flag is inverted. [description example...

Page 93

Chapter 5 explanation of instructions 93 user's manual u12326ej4v0um 5.10 call return instructions the following are call return instructions. Call ... 94 callf ... 95 callt ... 96 brk ... 97 ret ... 98 reti ... 99 retb ... 100

Page 94: Call

94 chapter 5 explanation of instructions user's manual u12326ej4v0um call call subroutine call (16 bit direct) [instruction format] call target [operation] (sp–1) ← (pc+3) h , (sp–2) ← (pc+3) l , sp ← sp–2, pc ← target [operand] mnemonic operand(target) call !Addr16 [flag] z ac cy [description] • th...

Page 95: Callf

Chapter 5 explanation of instructions 95 user's manual u12326ej4v0um call flag callf subroutine call (11 bit direct specification) [instruction format] callf target [operation] (sp–1) ← (pc+2) h , (sp–2) ← (pc+2) l , sp ← sp–2, pc ← target [operand] mnemonic operand(target) callf !Addr11 [flag] z ac...

Page 96: Callt

96 chapter 5 explanation of instructions user's manual u12326ej4v0um call table callt subroutine call (refer to the call table) [instruction format] callt [addr5] [operation] (sp–1) ← (pc+1) h , (sp–2) ← (pc+1) l , sp ← sp–2, pc h ← (00000000, addr5+1) pc l ← (00000000, addr5) [operand] mnemonic ope...

Page 97: Brk

Chapter 5 explanation of instructions 97 user's manual u12326ej4v0um break brk software vectored interrupt [instruction format] brk [operation] (sp–1) ← psw, (sp–2) ← (pc+1) h , (sp–3) ← (pc+1) l , ie ← 0, sp ← sp–3, pc h ← (3fh), pc l ← (3eh) [operand] none [flag] z ac cy [description] • this is a ...

Page 98: Ret

98 chapter 5 explanation of instructions user's manual u12326ej4v0um return ret return from subroutine [instruction format] ret [operation] pc l ← (sp), pc h ← (sp+1), sp ← sp+2 [operand] none [flag] z ac cy [description] • this is a return instruction from the subroutine call made with the call, ca...

Page 99: Reti

Chapter 5 explanation of instructions 99 user's manual u12326ej4v0um return from interrupt reti return from hardware vectored interrupt [instruction format] reti [operation] pc l ← (sp), pc h ← (sp+1), psw ← (sp+2), sp ← sp+3, nmis ← 0 [operand] none [flag] z ac cy r r r [description] • this is a re...

Page 100: Retb

100 chapter 5 explanation of instructions user's manual u12326ej4v0um return from break retb return from software vectored interrupt [instruction format] retb [operation] pc l ← (sp), pc h ← (sp+1), psw ← (sp+2), sp ← sp+3 [operand] none [flag] z ac cy r r r [description] • this is a return instruct...

Page 101

Chapter 5 explanation of instructions 101 user's manual u12326ej4v0um 5.11 stack manipulation instructions the following are stack manipulation instructions. Push ... 102 pop ... 103 movw sp, src ... 104 movw ax, sp ... 104.

Page 102: Push

102 chapter 5 explanation of instructions user's manual u12326ej4v0um push push push [instruction format] push src [operation] when src = rp when src = psw (sp–1) ← src h , (sp–1) ← src (sp–2) ← src l , sp ← sp–1 sp ← sp–2 [operand] mnemonic operand(src) push psw rp [flag] z ac cy [description] • th...

Page 103: Pop

Chapter 5 explanation of instructions 103 user's manual u12326ej4v0um pop pop pop [instruction format] pop dst [operation] when dst = rp when dst = psw dst l ← (sp), dst ← (sp) dst h ← (sp+1), sp ← sp+1 sp ← sp+2 [operand] mnemonic operand(dst) pop psw rp [flag] dst =rp psw z ac cy z ac cy r r r [de...

Page 104: Movw Sp, Src

104 chapter 5 explanation of instructions user's manual u12326ej4v0um movw sp, src move word movw ax, sp word data transfer with stack pointer [instruction format] movw dst, src [operation] dst ← src [operand] mnemonic operand(dst,src) movw sp, #word sp, ax ax, sp [flag] z ac cy [description] • this...

Page 105

Chapter 5 explanation of instructions 105 user's manual u12326ej4v0um 5.12 unconditional branch instruction the unconditional branch instruction is shown below. Br ... 106.

Page 106

106 chapter 5 explanation of instructions user's manual u12326ej4v0um branch br unconditional branch [instruction format] br target [operation] pc ← target [operand] mnemonic operand(target) br !Addr16 ax $addr16 [flag] z ac cy [description] • this is an instruction to branch unconditionally. • the ...

Page 107

Chapter 5 explanation of instructions 107 user's manual u12326ej4v0um 5.13 conditional branch instructions conditional branch instructions are shown below. Bc ... 108 bnc ... 109 bz ... 110 bnz ... 111 bt ... 112 bf ... 113 btclr ... 114 dbnz ... 115.

Page 108

108 chapter 5 explanation of instructions user's manual u12326ej4v0um branch if carry bc conditional branch with carry flag (cy = 1) [instruction format] bc $addr16 [operation] pc ← pc+2+jdisp8 if cy = 1 [operand] mnemonic operand($addr16) bc $addr16 [flag] z ac cy [description] • when cy = 1, data ...

Page 109: Bnc

Chapter 5 explanation of instructions 109 user's manual u12326ej4v0um branch if not carry bnc conditional branch with carry flag (cy = 0) [instruction format] bnc $addr16 [operation] pc ← pc+2+jdisp8 if cy = 0 [operand] mnemonic operand($addr16) bnc $addr16 [flag] z ac cy [description] • when cy = 0...

Page 110

110 chapter 5 explanation of instructions user's manual u12326ej4v0um branch if zero bz conditional branch with zero flag (z = 1) [instruction format] bz $addr16 [operation] pc ← pc+2+jdisp8 if z = 1 [operand] mnemonic operand($addr16) bz $addr16 [flag] z ac cy [description] • when z = 1, data is br...

Page 111: Bnz

Chapter 5 explanation of instructions 111 user's manual u12326ej4v0um branch if not zero bnz conditional branch with zero flag (z = 0) [instruction format] bnz $addr16 [operation] pc ← pc+2+jdisp8 if z = 0 [operand] mnemonic operand($addr16) bnz $addr16 [flag] z ac cy [description] • when z = 0, dat...

Page 112

112 chapter 5 explanation of instructions user's manual u12326ej4v0um branch if true bt conditional branch by bit test (byte data bit = 1) [instruction format] bt bit, $addr16 [operation] pc ← pc+b+jdisp8 if bit = 1 [operand] mnemonic operand(bit,$addr16) b(number of bytes) bt saddr.Bit, $addr16 3 s...

Page 113

Chapter 5 explanation of instructions 113 user's manual u12326ej4v0um branch if false bf conditional branch by bit test (byte data bit = 0) [instruction format] bf bit, $addr16 [operation] pc ← pc+b+jdisp8 if bit = 0 [operand] mnemonic operand(bit,$addr16) b(number of bytes) bf saddr.Bit, $addr16 4 ...

Page 114: Btclr

114 chapter 5 explanation of instructions user's manual u12326ej4v0um branch if true and clear btclr conditional branch and clear by bit test (byte data bit = 1) [instruction format] btclr bit, $addr16 [operation] pc ← pc+b+jdisp8 if bit = 1, then bit ← 0 [operand] mnemonic operand(bit,$addr16) b(nu...

Page 115: Dbnz

Chapter 5 explanation of instructions 115 user's manual u12326ej4v0um decrement and branch if not zero dbnz conditional loop (r1 ≠ 0) [instruction format] dbnz dst, $addr16 [operation] dst ← dst–1, then pc ← pc+b+jdisp16 if dst r1 ≠ 0 [operand] mnemonic operand(dst,$addr16) b(number of bytes) dbnz b...

Page 116

116 chapter 5 explanation of instructions user's manual u12326ej4v0um 5.14 cpu control instructions the following are cpu control instructions. Sel rbn ... 117 nop ... 118 ei ... 119 di ... 120 halt ... 121 stop ... 122.

Page 117: Sel Rbn

Chapter 5 explanation of instructions 117 user's manual u12326ej4v0um select register bank sel rbn register bank selection [instruction format] sel rbn [operation] rbs0, rbs1 ← n; (n = 0-3) [operand] mnemonic operand(rbn) sel rbn [flag] z ac cy [description] • the register bank specified by the oper...

Page 118: Nop

118 chapter 5 explanation of instructions user's manual u12326ej4v0um no operation nop no operation [instruction format] nop [operation] no operation [operand] none [flag] z ac cy [description] • only the time is consumed without processing..

Page 119

Chapter 5 explanation of instructions 119 user's manual u12326ej4v0um enable interrupt ei interrupt enabled [instruction format] ei [operation] ie ← 1 [operand] none [flag] z ac cy [description] • the maskable interrupt acknowledgeable status is set (by setting the interrupt enable flag (ie) to (1))...

Page 120

120 chapter 5 explanation of instructions user's manual u12326ej4v0um disable interrupt di interrupt disabled [instruction format] di [operation] ie ← 0 [operand] none [flag] z ac cy [description] • maskable interrupt acknowledgment by vectored interrupt is disabled (with the interrupt enable flag (...

Page 121: Halt

Chapter 5 explanation of instructions 121 user's manual u12326ej4v0um halt halt halt mode set [instruction format] halt [operation] set halt mode [operand] none [flag] z ac cy [description] • this instruction is used to set the halt mode to stop the cpu operation clock. The total power consumption o...

Page 122: Stop

122 chapter 5 explanation of instructions user's manual u12326ej4v0um stop stop stop mode set [instruction format] stop [operation] set stop mode [operand] none [flag] z ac cy [description] • this instruction is used to set the stop mode to stop the main system clock oscillator and to stop the whole...

Page 123

123 user's manual u12326ej4v0um appendix a revision history the following table shows the revision history of the previous editions. The “applied to:” column indicates the chapters of each edition in which the revision was applied. Edition major revision from previous edition applied to: 2nd additio...

Page 124

124 user's manual u12326ej4v0um appendix b instruction index (mnemonic: by function) [8-bit data transfer instructions] mov ... 49 xch ... 50 [16-bit data transfer instructions] movw ... 52 xchw ... 53 [8-bit operation instructions] add ... 55 addc ... 56 sub ... 57 subc ... 58 and ... 59 or ... 60 ...

Page 125

125 user's manual u12326ej4v0um [unconditional branch instruction] br ... 106 [conditional branch instructions] bc ... 108 bnc ... 109 bz ... 110 bnz ... 111 bt ... 112 bf ... 113 btclr ...114 dbnz ... 115 [cpu control instructions] sel rbn ... 117 nop ... 118 ei ... 119 di ... 120 halt ... 121 stop...

Page 126

126 user's manual u12326ej4v0um appendix c instruction index (mnemonic: in alphabetical order) [a] add ... 55 addc ... 56 addw ... 64 adjba ... 83 adjbs ... 84 and ... 59 and1 ... 87 [b] bc ... 108 bf ... 113 bnc ... 109 bnz ... 111 br ... 106 brk ... 97 bt ... 112 btclr ... 114 bz ... 110 [c] call ...

Page 127

127 user's manual u12326ej4v0um [s] sel rbn ... 117 set1 ... 90 stop ... 122 sub ... 57 subc ... 58 subw ... 65 [x] xch ... 50 xchw ... 53 xor ... 61 xor1 ... 89 appendix c instruction index (mnemonic: in alphabetical order).

Page 128

128 user's manual u12326ej4v0um [memo].

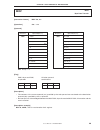

Page 129: Facsimile

Although nec has taken all possible steps to ensure that the documentation supplied to our customers is complete, bug free and up-to-date, we readily accept that errors may occur. Despite all the care and precautions we've taken, you may encounter problems in the documentation. Please complete this ...