- DL manuals

- NEC

- Microcontrollers

- ?PD703302

- User Manual

NEC ?PD703302 User Manual

Summary of ?PD703302

Page 1

V850es/ke1+ 32-bit single-chip microcontrollers hardware printed in japan user’s manual μ pd703302 μ pd703302y μ pd70f3302 μ pd70f3302y 2004 document no. U16896ej2v0ud00 (2nd edition) date published august 2006 n cp(k).

Page 2

User’s manual u16896ej2v0ud 2 [memo].

Page 3

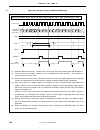

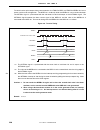

User’s manual u16896ej2v0ud 3 1 2 3 4 voltage application waveform at input pin waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the cmos device stays in the area between v il (max) and v ih (min) due to noise, etc., the device may malfunction. Take c...

Page 4

User’s manual u16896ej2v0ud 4 caution: μ pd70f3302 and 70f3302y use superflash ® technology licensed from silicon storage technology, inc. Iecube is a registered trademark of nec electronics corporation in japan and germany. Minicube is a registered trademark of nec electronics corporation in japan ...

Page 5

User’s manual u16896ej2v0ud 5 these commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited. The information in this document is current as of february, 2006. ...

Page 6

User’s manual u16896ej2v0ud 6 preface readers this manual is intended for users who wish to understand the functions of the v850es/ke1+ and design application systems using these products. Purpose this manual is intended to give users an understanding of the hardware functions of the v850es/ke1+ sho...

Page 7

User’s manual u16896ej2v0ud 7 conventions data significance: higher digits on the left and lower digits on the right active low representation: xxx (overscore over pin or signal name) memory map address: higher addresses on the top and lower addresses on the bottom note: footnote for item marked wit...

Page 8

User’s manual u16896ej2v0ud 8 contents chapter 1 introduction..................................................................................................................17 1.1 k1 series product lineup ................................................................................................

Page 9

User’s manual u16896ej2v0ud 9 4.3.8 port dl ...........................................................................................................................................99 4.4 block diagrams ..................................................................................................

Page 10

User’s manual u16896ej2v0ud 10 7.4.6 ppg output operation .................................................................................................................. 271 7.4.7 one-shot pulse output operation.........................................................................................

Page 11

User’s manual u16896ej2v0ud 11 11.1.1 functions ......................................................................................................................................347 11.1.2 configuration ................................................................................................

Page 12

User’s manual u16896ej2v0ud 12 14.6 dedicated baud rate generator n (brgn) ............................................................................ 424 14.6.1 baud rate generator n (brgn) configuration ............................................................................... 424 14.6.2 ser...

Page 13

User’s manual u16896ej2v0ud 13 16.13.2 when communication reservation function is disabled (iicf0.Iicrsv0 bit = 1) ...........................514 16.14 cautions.................................................................................................................................... 515 16....

Page 14

User’s manual u16896ej2v0ud 14 19.3.1 setting and operation status ........................................................................................................ 578 19.3.2 releasing halt mode.....................................................................................................

Page 15

User’s manual u16896ej2v0ud 15 23.1 function .................................................................................................................................... 618 23.2 configuration.......................................................................................................

Page 16

User’s manual u16896ej2v0ud 16 appendix a development tools............................................................................................... 680 a.1 software package..................................................................................................................... 683...

Page 17

User’s manual u16896ej2v0ud 17 chapter 1 introduction 1.1 k1 series product lineup 1.1.1 v850es/kx1+, v850es/kx1 products lineup v850es/ke1 • 64-pin plastic lqfp (10 × 10 mm, 0.5 mm pitch) • 64-pin plastic tqfp (12 × 12 mm, 0.65 mm pitch) pd70f3207hy pd70f3207h single-power flash: 128 kb, ram: 4 kb ...

Page 18

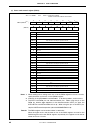

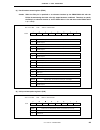

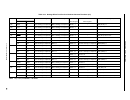

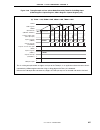

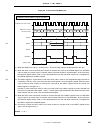

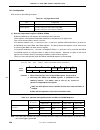

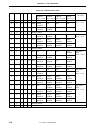

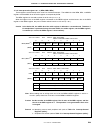

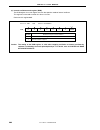

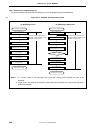

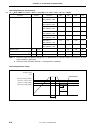

Chapter 1 introduction user’s manual u16896ej2v0ud 18 the function list of the v850es/kx1+ is shown below. Product name v850es/ke1+ v850es/kf1+ v850es/kg1+ v850es/kj1+ number of pins 64 pins 80 pins 100 pins 144 pins mask rom 128 − − 256 − − 256 − − − flash memory − 128 128 − 256 128 − 256 128 256 i...

Page 19

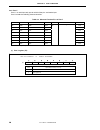

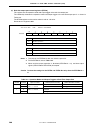

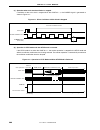

Chapter 1 introduction user’s manual u16896ej2v0ud 19 the function list of the v850es/kx1 is shown below. Product name v850es/ke1 v850es/kf1 v850es/kg1 v850es/kj1 number of pins 64 pins 80 pins 100 pins 144 pins mask rom 128 − 64/ 96 128 − 256 − 64/ 96 128 − 256 − 96/128 − − flash memory − 128 − − 1...

Page 20

Chapter 1 introduction user’s manual u16896ej2v0ud 20 1.1.2 78k0/kx1+, 78k0/kx1 products lineup mask rom: 24 kb, ram: 768 b mask rom: 16 kb, ram: 768 b mask rom: 8 kb, ram: 512 b pd780101 78k0/kb1 30-pin ssop (7.62 mm 0.65 mm pitch) single-power flash: 24 kb, ram: 768 b single-power flash: 16 kb, ra...

Page 21

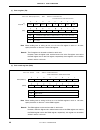

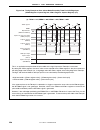

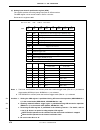

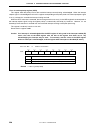

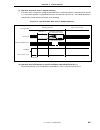

Chapter 1 introduction user’s manual u16896ej2v0ud 21 the list of functions in the 78k0/kx1 is shown below. Part number item 78k0/kb1 78k0/kc1 78k0/kd1 78k0/ke1 78k0/kf1 number of pins 30 pins 44 pins 52 pins 64 pins 80 pins mask rom 8 16/ 24 − 8/ 16 24/ 32 − 8/ 16 24/ 32 − 8/ 16 24/ 32 − 48/ 60 − 2...

Page 22

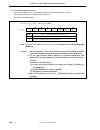

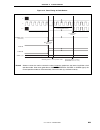

Chapter 1 introduction user’s manual u16896ej2v0ud 22 the list of functions in the 78k0/kx1+ is shown below. Part number item 78k0/kb1+ 78k0/kc1+ 78k0/kd1+ 78k0/ke1+ 78k0/kf1+ number of pins 30 pins 44 pins 52 pins 64 pins 80 pins flash memory 8 16/24 16 24/32 16 24/32 16 24/32 48/60 60 internal mem...

Page 23

Chapter 1 introduction user’s manual u16896ej2v0ud 23 1.2 features { minimum instruction execution time: 50 ns (operation at main clock (f xx ) = 20 mhz) { general-purpose registers: 32 bits × 32 registers { cpu features: signed multiplication (16 × 16 → 32): 1 to 2 clocks (instructions without crea...

Page 24

Chapter 1 introduction user’s manual u16896ej2v0ud 24 { internal oscillator: 240 khz (typ.) remark for frequency characteristics (error) of internal oscillator, refer to chapter 28 electrical specifications. { reset • reset by reset pin • reset by overflow of watchdog timer 1 (wdtres1) • reset by ov...

Page 25

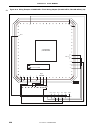

Chapter 1 introduction user’s manual u16896ej2v0ud 25 1.5 pin configuration (top view) 64-pin plastic tqfp (12 × 12) 64-pin plastic lqfp (fine pitch) (10 × 10) μ pd703302gk- ×××-9et-a μ pd703302gb- ×××-8eu-a μ pd703302ygk- ×××-9et-a μ pd703302ygb- ×××-8eu-a μ pd70f3302gk-9et-a μ pd70f3302gb-8eu-a μ ...

Page 26

Chapter 1 introduction user’s manual u16896ej2v0ud 26 pin identification adtrg: a/d trigger input ani0 to ani7: analog input asck0: asynchronous serial clock av ref0 : analog reference voltage av ss : ground for analog clkout: clock output ev dd : power supply for port ev ss : ground for port flmd0,...

Page 27

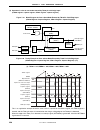

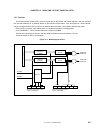

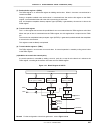

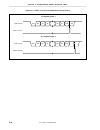

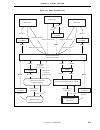

Chapter 1 introduction user’s manual u16896ej2v0ud 27 1.6 function block configuration (1) internal block diagram nmi to01 ti010, ti011 so00, so01 si00, si01 sck00, sck01 intp0 to intp7 intc top00, top01 tip00, tip01 to50, to51 ti50, ti51 toh0, toh1 txd0, txd1 rxd0, rxd1 asck0 rtp00 to rtp05 kr0 to ...

Page 28

Chapter 1 introduction user’s manual u16896ej2v0ud 28 (2) internal units (a) cpu the cpu uses five-stage pipeline control to enable single-clock execution of address calculations, arithmetic logic operations, data transfers, and almost all other types of instruction processing. Other dedicated on-ch...

Page 29

Chapter 1 introduction user’s manual u16896ej2v0ud 29 (i) watchdog timer two watchdog timer channels are provided on chip to detect program loops and system abnormalities. Watchdog timer 1 can be used as an interval timer. When used as a watchdog timer, it generates a non- maskable interrupt request...

Page 30

Chapter 1 introduction user’s manual u16896ej2v0ud 30 (q) power-on-clear (poc) circuit the power-on-clear circuit generates an internal reset signal at power on. The power-on-clear circuit compares the supply voltage (v dd ) and detection voltage (v poc ), and generates an internal reset signal when...

Page 31

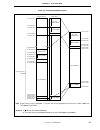

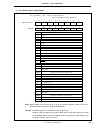

Chapter 1 introduction user’s manual u16896ej2v0ud 31 1.7 overview of functions part number μ pd703302, 703302y μ pd70f3302, 70f3302y rom 128 kb 128 kb (single-power flash memory) internal memory high-speed ram 4 kb memory space 64 mb general-purpose registers 32 bits × 32 registers ceramic/crystal/...

Page 32

User’s manual u16896ej2v0ud 32 chapter 2 pin functions the names and functions of the pins of the v850es/ke1+ are described below, divided into port pins and non-port pins. The pin i/o buffer power supplies are divided into two systems; av ref0 and ev dd . The relationship between these power suppli...

Page 33

Chapter 2 pin functions user’s manual u16896ej2v0ud 33 (2/2) pin name pin no. I/o pull-up resistor function alternate function p50 28 ti011/rtp00/kr0 p51 29 ti50/rtp01/kr1 p52 30 to50/rtp02/kr2 p53 31 rtp03/kr3 p54 34 rtp04/kr4 p55 35 i/o yes port 5 i/o port input/output can be specified in 1-bit un...

Page 34

Chapter 2 pin functions user’s manual u16896ej2v0ud 34 (2) non-port pins (1/2) pin name pin no. I/o pull-up resistor function alternate function adtrg 24 input yes a/d converter external trigger input p32/asck0/to01 ani0 64 p70 ani1 63 p71 ani2 62 p72 ani3 61 p73 ani4 60 p74 ani5 59 p75 ani6 58 p76 ...

Page 35

Chapter 2 pin functions user’s manual u16896ej2v0ud 35 (2/2) pin name pin no. I/o pull-up resistor function alternate function rtp00 28 p50/ti011/kr0 rtp01 29 p51/ti50/kr1 rtp02 30 p52/to50/kr2 rtp03 31 p53/kr3 rtp04 34 p54/kr4 rtp05 35 output yes real-time output port p55/kr5 rxd0 23 serial receive...

Page 36

Chapter 2 pin functions user’s manual u16896ej2v0ud 36 2.2 pin i/o circuits and recommended connection of unused pins (1/2) pin alternate function pin no. I/o circuit type recommended connection p00 toh0 12 p01 toh1 13 5-a p02 nmi 14 p03 to p06 intp0 to intp3 15 to 18 5-w p30 txd0 22 5-a p31 rxd0/in...

Page 37

Chapter 2 pin functions user’s manual u16896ej2v0ud 37 (2/2) pin alternate function pin no. I/o circuit type recommended connection av ref0 – 1 – directly connect to v dd . Av ss – 2 – – ev dd – 33 – – ev ss – 32 – – ic note 1 – 3 – directly connect to ev ss or v ss or pull down with a 10 k Ω resist...

Page 38

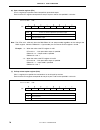

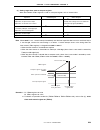

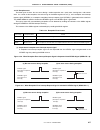

Chapter 2 pin functions user’s manual u16896ej2v0ud 38 2.3 pin i/o circuits (1/2) type 2 type 8-a type 9-c type 5-a type 10-a type 5-w type 10-e schmitt-triggered input with hysteresis characteristics in data output disable p-ch in/out v dd n-ch input enable p-ch v dd pull-up enable in comparator + ...

Page 39

Chapter 2 pin functions user’s manual u16896ej2v0ud 39 (2/2) type 16 p-ch feedback cut-off xt1 xt2 type 13-ae data output disable input enable in/out n-ch v ss mask option v dd type 13-ad data output disable input enable in/out n-ch v ss remark read v dd as ev dd . Also, read v ss as ev ss ..

Page 40

User’s manual u16896ej2v0ud 40 chapter 3 cpu functions the cpu of the v850es/ke1+ is based on the risc architecture and executes most instructions in one clock cycle by using 5-stage pipeline control. 3.1 features { number of instructions: 83 { minimum instruction execution time: 50.0 ns (@ 20 mhz o...

Page 41

Chapter 3 cpu functions user’s manual u16896ej2v0ud 41 3.2 cpu register set the cpu registers of the v850es/ke1+ can be classified into two categories: a general-purpose program register set and a dedicated system register set. All the registers have 32-bit width. For details, refer to the v850es ar...

Page 42

Chapter 3 cpu functions user’s manual u16896ej2v0ud 42 3.2.1 program register set the program register set includes general-purpose registers and a program counter. (1) general-purpose registers (r0 to r31) thirty-two general-purpose registers, r0 to r31, are available. All of these registers can be...

Page 43

Chapter 3 cpu functions user’s manual u16896ej2v0ud 43 3.2.2 system register set system registers control the status of the cpu and hold interrupt information. Read from and write to system registers are performed by setting the system register numbers shown below with the system register load/store...

Page 44

Chapter 3 cpu functions user’s manual u16896ej2v0ud 44 (1) interrupt status saving registers (eipc, eipsw) there are two interrupt status saving registers, eipc and eipsw. Upon occurrence of a software exception or a maskable interrupt, the contents of the program counter (pc) are saved to eipc and ...

Page 45

Chapter 3 cpu functions user’s manual u16896ej2v0ud 45 (2) nmi status saving registers (fepc, fepsw) there are two nmi status saving registers, fepc and fepsw. Upon occurrence of a non-maskable interrupt (nmi), the contents of the program counter (pc) are saved to fepc and the contents of the progra...

Page 46

Chapter 3 cpu functions user’s manual u16896ej2v0ud 46 (4) program status word (psw) the program status word (psw) is a collection of flags that indicate the program status (instruction execution result) and the cpu status. When the contents of this register are changed using the ldsr instruction, t...

Page 47

Chapter 3 cpu functions user’s manual u16896ej2v0ud 47 (2/2) note during saturated operation, the saturated operation results are determined by the contents of the ov flag and s flag. The sat flag is set (to 1) only when the ov flag is set (to 1) during saturated operation. Flag status operation res...

Page 48

Chapter 3 cpu functions user’s manual u16896ej2v0ud 48 (6) exception/debug trap status saving registers (dbpc, dbpsw) there are two exception/debug trap status saving registers, dbpc and dbpsw. Upon occurrence of an exception trap or debug trap, the contents of the program counter (pc) are saved to ...

Page 49

Chapter 3 cpu functions user’s manual u16896ej2v0ud 49 3.3 operating modes the v850es/ke1+ has the following operating modes. (1) normal operating mode after the system has been released from the reset state, the pins related to the bus interface are set to the port mode, execution branches to the r...

Page 50

Chapter 3 cpu functions user’s manual u16896ej2v0ud 50 3.4 address space 3.4.1 cpu address space for instruction addressing, an internal rom area of up to 1 mb, and an internal ram area are supported in a linear address space (program space) of up to 64 mb. For operand addressing (data access), up t...

Page 51

Chapter 3 cpu functions user’s manual u16896ej2v0ud 51 3.4.2 wraparound of cpu address space (1) program space of the 32 bits of the program counter (pc), the higher 6 bits are fixed to 0 and only the lower 26 bits are valid. Even if a carry or borrow occurs from bit 25 to bit 26 as a result of bran...

Page 52

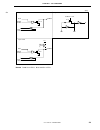

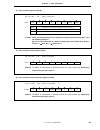

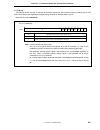

Chapter 3 cpu functions user’s manual u16896ej2v0ud 52 3.4.3 memory map the v850es/ke1+ has reserved areas as shown below. Figure 3-2. Data memory map (physical addresses) 3ffffffh 3fec000h 3febfffh 0100000h 00fffffh 0000000h 3fff000h 3ffefffh 3fff000h 3ffefffh 3ffffffh 3fec000h (80 kb) use-prohibit...

Page 53

Chapter 3 cpu functions user’s manual u16896ej2v0ud 53 figure 3-3. Program memory map 03ff0000h 03feffffh 03fff000h 03ffefffh 03ffffffh 00100000h 000fffffh 00000000h internal ram area (60 kb) use-prohibited area (program fetch disabled area) use-prohibited area (program fetch disabled area) internal...

Page 54

Chapter 3 cpu functions user’s manual u16896ej2v0ud 54 3.4.4 areas (1) internal rom area an area of 1 mb from 0000000h to 00fffffh is reserved for the internal rom area. (a) internal rom (128 kb) a 128 kb area from 0000000h to 001ffffh is provided in the v850es/ke1+. Addresses 0020000h to 00fffffh a...

Page 55

Chapter 3 cpu functions user’s manual u16896ej2v0ud 55 (3) on-chip peripheral i/o area a 4 kb area from 3fff000h to 3ffffffh is reserved as the on-chip peripheral i/o area. Figure 3-6. On-chip peripheral i/o area 3ffffffh 3fff000h on-chip peripheral i/o area (4 kb) fffffffh ffff000h physical address...

Page 56

Chapter 3 cpu functions user’s manual u16896ej2v0ud 56 3.4.5 recommended use of address space the architecture of the v850es/ke1+ requires that a register that serves as a pointer be secured for address generation when operand data in the data space is accessed. The address stored in this pointer ±3...

Page 57

Chapter 3 cpu functions user’s manual u16896ej2v0ud 57 figure 3-7. Recommended memory map data space program space on-chip peripheral i/o on-chip peripheral i/o internal ram internal ram internal rom use prohibited use prohibited internal ram on-chip peripheral i/o note program space 64 mb internal ...

Page 58

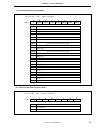

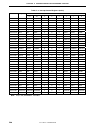

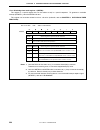

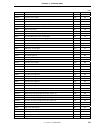

Chapter 3 cpu functions user’s manual u16896ej2v0ud 58 3.4.6 peripheral i/o registers (1/7) operable bit unit address function register name symbol r/w 1 8 16 after reset fffff004h port dl register pdl r/w √ √ 00h note 1 fffff00ch port cm register pcm r/w √ √ 00h note 1 fffff024h port dl mode regist...

Page 59

Chapter 3 cpu functions user’s manual u16896ej2v0ud 59 (2/7) operable bit unit address function register name symbol r/w 1 8 16 after reset fffff148h interrupt control register wtiic r/w √ √ 47h fffff14ah interrupt control register wtic r/w √ √ 47h fffff14ch interrupt control register brgic r/w √ √ ...

Page 60

Chapter 3 cpu functions user’s manual u16896ej2v0ud 60 (3/7) operable bit unit address function register name symbol r/w 1 8 16 after reset fffff446h port 3 mode control register pmc3 r/w √ 0000h fffff446h port 3 mode control register l pmc3l r/w √ √ 00h fffff447h port 3 mode control register h pmc3...

Page 61

Chapter 3 cpu functions user’s manual u16896ej2v0ud 61 (4/7) operable bit unit address function register name symbol r/w 1 8 16 after reset fffff5c6h 16-bit timer mode control register 5 tmc5 r/w √ 0000h fffff5c6h 8-bit timer mode control register 50 tmc50 r/w √ √ 00h fffff5c7h 8-bit timer mode cont...

Page 62

Chapter 3 cpu functions user’s manual u16896ej2v0ud 62 (5/7) operable bit unit address function register name symbol r/w 1 8 16 32 after reset fffff820h power save mode register psmr r/w √ √ 00h fffff828h processor clock control register pcc r/w √ √ 03h fffff82eh cpu operation clock status register ...

Page 63

Chapter 3 cpu functions user’s manual u16896ej2v0ud 63 (6/7) operable bit unit address function register name symbol r/w 1 8 16 after reset fffffb00h tip00 noise elimination control register p0nfc r/w √ √ 00h fffffb04h tip01 noise elimination control register p1nfc r/w √ √ 00h fffffc00h external int...

Page 64

Chapter 3 cpu functions user’s manual u16896ej2v0ud 64 (7/7) operable bit unit address function register name symbol r/w 1 8 16 after reset fffffd1ah serial i/o shift register 1 sio01 r/w √ 00h fffffd1ah serial i/o shift register 1l sio01l r/w √ 0000h fffffd80h iic shift register 0 iic0 note r/w √ 0...

Page 65

Chapter 3 cpu functions user’s manual u16896ej2v0ud 65 3.4.7 special registers special registers are registers that prevent invalid data from being written when an inadvertent program loop occurs. The v850es/ke1+ has the following six special registers. • power save control register (psc) • processo...

Page 66

Chapter 3 cpu functions user’s manual u16896ej2v0ud 66 [description example] when using psc register (standby mode setting) st.B r11, psmr[r0] ; psmr register setting (idle, stop mode setting) mov 0x02, r10 st.B r10, prcmd[r0] ; prcmd register write st.B r10, psc[r0] ; psc register setting nop note ...

Page 67

Chapter 3 cpu functions user’s manual u16896ej2v0ud 67 (3) system status register (sys) this register is allocated with status flags showing the operating state of the entire system. This register can be read or written in 8-bit or 1-bit units. 0 protection error has not occurred protection error ha...

Page 68

Chapter 3 cpu functions user’s manual u16896ej2v0ud 68 3.4.8 cautions (1) wait when accessing register be sure to set the following register before using the v850es/ke1+. • system wait control register (vswc) after setting the vswc register, set the other registers as required. When using an externa...

Page 69

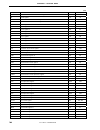

Chapter 3 cpu functions user’s manual u16896ej2v0ud 69 peripheral function register name access k wdtm1 write 1 to 5 watchdog timer 1 (wdt1) note 1 > k = {(1/f x ) × 2/((2 + m)/f cpu )} + 1 f x : main clock oscillation frequency watchdog timer 2 (wdt2) wdtm2 write 3 (fixed) tp0ccr0, tp0ccr1, tp0cnt ...

Page 70

Chapter 3 cpu functions user’s manual u16896ej2v0ud 70 (2) restriction on conflict between sld instruction and interrupt request (a) description if a conflict occurs between the decode operation of an instruction in immediately before the sld instruction following an instruction in and an interrupt ...

Page 71

User’s manual u16896ej2v0ud 71 chapter 4 port functions 4.1 features { input-only ports: 8 pins { i/o ports: 43 pins • fixed to n-ch open-drain output: 2 • switchable to n-ch open-drain output: 4 { input/output can be specified in 1-bit units 4.2 basic port configuration the v850es/ke1+ incorporates...

Page 72

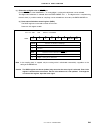

Chapter 4 port functions user’s manual u16896ej2v0ud 72 4.3 port configuration table 4-2. Port configuration item configuration control registers port n register (pn: n = 0, 3 to 5, 7, 9, cm, dl) port n mode register (pmn: n = 0, 3 to 5, 9, cm, dl) port n mode control register (pmcn: n = 0, 3 to 5, ...

Page 73

Chapter 4 port functions user’s manual u16896ej2v0ud 73 (1) port n register (pn) data i/o with external devices is performed by writing to and reading from the pn register. The pn register is configured of a port latch that retains the output data and a circuit that reads the pin status. Each bit of...

Page 74

Chapter 4 port functions user’s manual u16896ej2v0ud 74 (2) port n mode register (pmn) pmn specifies the input mode/output mode of the port. Each bit of the pmn register corresponds to one pin of port n and can be specified in 1-bit units. Pmn7 output mode input mode pmnm 0 1 control of i/o mode pmn...

Page 75

Chapter 4 port functions user’s manual u16896ej2v0ud 75 (4) port n function control register (pfcn) pfcn is a register that specifies the alternate function to be used when one pin has two or more alternate functions. Each bit of the pfcn register corresponds to one pin of port n and can be specifie...

Page 76

Chapter 4 port functions user’s manual u16896ej2v0ud 76 (6) port n function register (pfn) pfn is a register that specifies normal output/n-ch open-drain output. Each bit of the pfn register corresponds to one pin of port n and can be specified in 1-bit units. Pfn7 pfn6 pfn5 pfn4 pfn3 pfn2 pfn1 pfn0...

Page 77

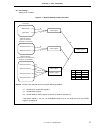

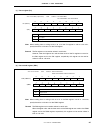

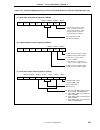

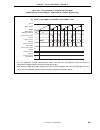

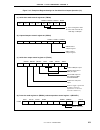

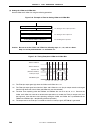

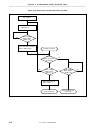

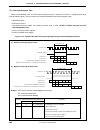

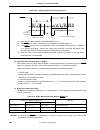

Chapter 4 port functions user’s manual u16896ej2v0ud 77 (8) port settings set the ports as follows. Figure 4-1. Register settings and pin functions pmcn register output mode input mode pmn register “ 0 ” “ 1 ” “ 0 ” “ 1 ” “ 0 ” “ 1 ” (a) (b) (c) (d) alternate function (when two alternate functions a...

Page 78

Chapter 4 port functions user’s manual u16896ej2v0ud 78 4.3.1 port 0 port 0 is a 7-bit i/o port for which i/o settings can be controlled in 1-bit units. Port 0 includes the following alternate functions. Table 4-4. Alternate-function pins of port 0 pin no. Pin name alternate function i/o pull note 1...

Page 79

Chapter 4 port functions user’s manual u16896ej2v0ud 79 (3) port 0 mode control register (pmc0) 0 pmc0 pmc06 pmc05 pmc04 pmc03 pmc02 pmc01 pmc00 i/o port intp3 input pmc06 0 1 specification of p06 pin operation mode i/o port intp2 input pmc05 0 1 specification of p05 pin operation mode i/o port intp...

Page 80

Chapter 4 port functions user’s manual u16896ej2v0ud 80 4.3.2 port 3 port 3 is an 8-bit i/o port for which i/o settings can be controlled in 1-bit units. Port 3 includes the following alternate functions. Table 4-5. Alternate-function pins of port 3 pin no. Pin name alternate function i/o pull note ...

Page 81

Chapter 4 port functions user’s manual u16896ej2v0ud 81 (1) port 3 register (p3) 0 is output 1 is output p3n 0 1 control of output data (in output mode) (n = 0 to 5, 8, 9) p3 (p3h note ) after reset: 00h (output latch) r/w address: p3 fffff406h, p3l fffff406h, p3h fffff407h 0 0 p35 p34 p33 p32 p31 p...

Page 82

Chapter 4 port functions user’s manual u16896ej2v0ud 82 (3) port 3 mode control register (pmc3) pmc3 (pmc3h note 1 ) i/o port scl0 i/o pmc39 0 1 specification of p39 pin operation mode i/o port sda0 i/o pmc38 0 1 specification of p38 pin operation mode i/o port ti010 input/to01 output pmc35 0 1 spec...

Page 83

Chapter 4 port functions user’s manual u16896ej2v0ud 83 (4) port 3 function register h (pf3h) 0 when used as normal port (n-ch open-drain output) when used as alternate-function (n-ch open-drain output) pf3n 0 1 specification of normal port/alternate function (n = 8, 9) pf3h 0 0 0 0 0 pf39 pf38 afte...

Page 84

Chapter 4 port functions user’s manual u16896ej2v0ud 84 (7) specifying alternate-function pins of port 3 pfc35 specification of alternate-function pin of p35 pin 0 ti010 input 1 to01 output pfce34 pfc34 specification of alternate-function pin of p34 pin 0 0 setting prohibited 0 1 setting prohibited ...

Page 85

Chapter 4 port functions user’s manual u16896ej2v0ud 85 4.3.3 port 4 port 4 is a 3-bit i/o port for which i/o settings can be controlled in 1-bit units. Port 4 includes the following alternate functions. Table 4-6. Alternate-function pins of port 4 pin no. Pin name alternate function i/o pull note r...

Page 86

Chapter 4 port functions user’s manual u16896ej2v0ud 86 (3) port 4 mode control register (pmc4) 0 pmc4 0 0 0 0 pmc42 pmc41 pmc40 i/o port sck00 i/o pmc42 0 1 specification of p42 pin operation mode i/o port so00 output pmc41 0 1 specification of p41 pin operation mode i/o port si00 input pmc40 0 1 s...

Page 87

Chapter 4 port functions user’s manual u16896ej2v0ud 87 4.3.4 port 5 port 5 is a 6-bit i/o port for which i/o settings can be controlled in 1-bit units. Port 5 includes the following alternate functions. Table 4-7. Alternate-function pins of port 5 pin no. Pin name alternate function i/o pull note r...

Page 88

Chapter 4 port functions user’s manual u16896ej2v0ud 88 (3) port 5 mode control register (pmc5) i/o port/kr5 input rtp05 output pmc55 0 1 specification of p55 pin operation mode i/o port/kr4 input rtp04 output pmc54 0 1 specification of p54 pin operation mode 0 0 pmc55 pmc54 pmc53 pmc52 pmc51 pmc50 ...

Page 89

Chapter 4 port functions user’s manual u16896ej2v0ud 89 (4) port 5 function control register (pfc5) caution when the p5n pin is specified as an alternate function by the pmc5.Pmc5n bit with the pfc5n bit maintaining the initial value (0), output becomes undefined. Therefore, to specify the p5n pin a...

Page 90

Chapter 4 port functions user’s manual u16896ej2v0ud 90 4.3.5 port 7 port 7 is an 8-bit input-only port for which all the pins are fixed to input. Port 7 includes the following alternate functions. Table 4-8. Alternate-function pins of port 7 pin no. Pin name alternate function i/o pull note remark ...

Page 91

Chapter 4 port functions user’s manual u16896ej2v0ud 91 4.3.6 port 9 port 9 is a 9-bit i/o port for which i/o settings can be controlled in 1-bit units. Port 9 includes the following alternate functions. Table 4-9. Alternate-function pins of port 9 pin no. Pin name alternate function i/o pull note r...

Page 92

Chapter 4 port functions user’s manual u16896ej2v0ud 92 (1) port 9 register (p9) 0 is output 1 is output p9n 0 1 control of output data (in output mode) (n = 0, 1, 6 to 9, 13 to 15) after reset: 00h (output latch) r/w address: p9 fffff412h, p9l fffff412h, p9h fffff413h p915 p9 (p9h note ) p914 p913 ...

Page 93

Chapter 4 port functions user’s manual u16896ej2v0ud 93 (3) port 9 mode control register (pmc9) i/o port intp6 input pmc915 0 1 specification of p915 pin operation mode pmc97 pmc96 0 0 0 0 pmc91 pmc90 after reset: 0000h r/w address: pmc9 fffff452h, pmc9l fffff452h, pmc9h fffff453h pmc915 pmc9 (pmc9h...

Page 94

Chapter 4 port functions user’s manual u16896ej2v0ud 94 (4) port 9 function register h (pf9h) 0 normal output n-ch open-drain output pf9n 0 1 control of normal output/n-ch open-drain output (n = 8, 9) pf9h 0 0 0 0 0 pf99 pf98 after reset: 00h r/w address: fffffc73h caution when using p98 and p99 as ...

Page 95

Chapter 4 port functions user’s manual u16896ej2v0ud 95 (5) port 9 function control register (pfc9) caution when port 9 is specified as an alternate function by the pmc9.Pmc9n bit with the pfc9n bit maintaining the initial value (0), output becomes undefined. Therefore, to specify port 9 as alternat...

Page 96

Chapter 4 port functions user’s manual u16896ej2v0ud 96 (6) pull-up resistor option register 9 (pu9) not connected connected pu9n 0 1 control of on-chip pull-up resistor connection (n = 0, 1, 6 to 9, 13 to 15) pu9 (pu9h note ) after reset: 0000h r/w address: pu9 fffffc52h, pu9l fffffc52h, pu9h fffff...

Page 97

Chapter 4 port functions user’s manual u16896ej2v0ud 97 4.3.7 port cm port cm is a 2-bit i/o port for which i/o settings can be controlled in 1-bit units. Port cm includes the following alternate functions. Table 4-10. Alternate-function pins of port cm pin no. Pin name alternate function i/o pull n...

Page 98

Chapter 4 port functions user’s manual u16896ej2v0ud 98 (4) pull-up resistor option register cm (pucm) not connected connected pucmn 0 1 control of on-chip pull-up resistor connection (n = 0, 1) after reset: 00h r/w address: ffffff4ch 0 pucm 0 0 0 0 0 pucm1 pucm0

Page 99

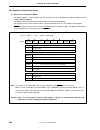

Chapter 4 port functions user’s manual u16896ej2v0ud 99 4.3.8 port dl port dl is an 8-bit i/o port for which i/o settings can be controlled in 1-bit units. Port dl includes the following alternate functions. Table 4-11. Alternate-function pins of port dl pin no. Pin name alternate function i/o pull ...

Page 100

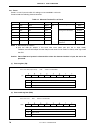

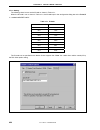

Chapter 4 port functions user’s manual u16896ej2v0ud 100 (1) port dl register (pdl) 0 is output 1 is output pdln 0 1 control of output data (in output mode) (n = 0 to 7) after reset: 00h (output latch) r/w address: fffff004h pdl7 pdl6 pdl5 pdl4 pdl3 pdl2 pdl1 pdl0 pdl (2) port dl mode register (pmdl...

Page 101

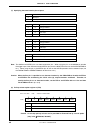

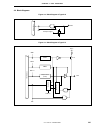

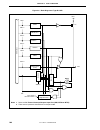

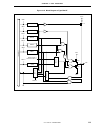

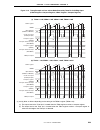

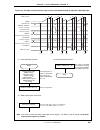

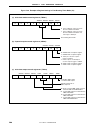

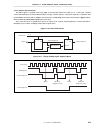

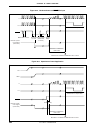

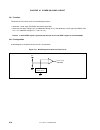

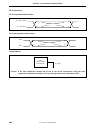

Chapter 4 port functions user’s manual u16896ej2v0ud 101 4.4 block diagrams figure 4-2. Block diagram of type a-a internal bus rd a/d input signal pmn p-ch n-ch figure 4-3. Block diagram of type c-u wr pm rd wr port pmn pmmn wr pu ev dd pumn p-ch address output latch (pmn) internal bus selector sele...

Page 102

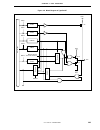

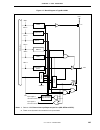

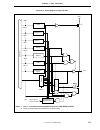

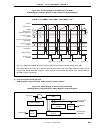

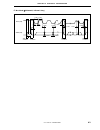

Chapter 4 port functions user’s manual u16896ej2v0ud 102 figure 4-4. Block diagram of type d0-u wr pmc rd address output signal of alternate function 1 wr port pmn pmcmn wr pu pumn wr pm pmmn ev dd p-ch output latch (pmn) internal bus selector selector selector.

Page 103

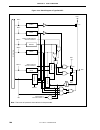

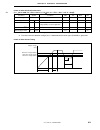

Chapter 4 port functions user’s manual u16896ej2v0ud 103 figure 4-5. Block diagram of type d0-uf wr pmc rd wr port pmn pmcmn wr pu pumn wr pm pmmn wr pf pfmn ev dd p-ch ev dd ev ss p-ch n-ch address output latch (pmn) internal bus selector selector selector output signal of alternate function 1.

Page 104

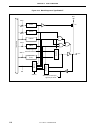

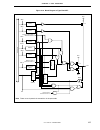

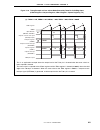

Chapter 4 port functions user’s manual u16896ej2v0ud 104 figure 4-6. Block diagram of type d1-suil wr pmc rd address input signal of alternate function 1 wr port pmn note 2 pmcmn wr intf intfmn note 1 wr pu pumn wr pm pmmn noise elimination edge detection wr intr intrmn note 1 ev dd p-ch output latc...

Page 105

Chapter 4 port functions user’s manual u16896ej2v0ud 105 figure 4-7. Block diagram of type d1-suihl wr pmc rd address wr port pmn pmcmn wr pu pumn wr pm pmmn wr intf intfmn note 1 wr intr intrmn note 1 ev dd p-ch input signal of alternate function 1-2 input signal of alternate function 1-1 noise eli...

Page 106

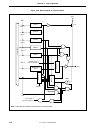

Chapter 4 port functions user’s manual u16896ej2v0ud 106 figure 4-8. Block diagram of type d1-sul wr pmc rd wr port address pmn pmcmn wr pu pumn wr pm pmmn ev dd p-ch note output latch (pmn) internal bus selector selector input signal of alternate function 1 note there are no hysteresis characterist...

Page 107

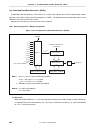

Chapter 4 port functions user’s manual u16896ej2v0ud 107 figure 4-9. Block diagram of type d2-snmufh wr pmc rd address output signal of alternate function 1 input signal of alternate function 1 wr port pmcmn wr pf pfmn wr pm pmmn pmn ev dd ev ss note mask option n-ch output latch (pmn) internal bus ...

Page 108

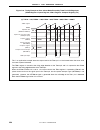

Chapter 4 port functions user’s manual u16896ej2v0ud 108 figure 4-10. Block diagram of type d2-sufl wr pmc rd note wr port pmn pmcmn wr pu pumn wr pm pmmn wr pf pfmn ev dd p-ch ev dd ev ss p-ch n-ch address output latch (pmn) internal bus selector selector selector input signal of alternate function...

Page 109

Chapter 4 port functions user’s manual u16896ej2v0ud 109 figure 4-11. Block diagram of type e00-sut wr pmc rd address alternate-function input signal in port mode output signal of alternate function 2 output signal of alternate function 1 wr port pmn pmcmn wr pu pumn wr pm pmmn wr pfc pfcmn ev dd p-...

Page 110

Chapter 4 port functions user’s manual u16896ej2v0ud 110 figure 4-12. Block diagram of type e10-sul wr pmc rd address input signal of alternate function 1 output signal of alternate function 2 wr port pmn pmcmn wr pu pumn wr pm pmmn wr pfc pfcmn ev dd p-ch output latch (pmn) internal bus selector se...

Page 111

Chapter 4 port functions user’s manual u16896ej2v0ud 111 figure 4-13. Block diagram of type e10-sult wr pmc rd address alternate-function input signal in port mode input signal of alternate function 1 output signal of alternate function 2 wr port pmn pmcmn wr pu pumn wr pm pmmn wr pfc pfcmn ev dd p-...

Page 112

Chapter 4 port functions user’s manual u16896ej2v0ud 112 figure 4-14. Block diagram of type ex0-sut wr pmc rd address alternate-function input signal in port mode output signal of alternate function 2 wr port pmn pmcmn wr pu pumn wr pm pmmn wr pfc pfcmn ev dd p-ch output latch (pmn) internal bus sel...

Page 113

Chapter 4 port functions user’s manual u16896ej2v0ud 113 figure 4-15. Block diagram of type ex0-uf wr pmc rd address output signal of alternate function 2 wr port pmn pmcmn wr pfc pfcmn wr pu pumn wr pm pmmn wr pf pfmn ev dd p-ch ev dd ev ss p-ch n-ch output latch (pmn) internal bus selector selecto...

Page 114

Chapter 4 port functions user’s manual u16896ej2v0ud 114 figure 4-16. Block diagram of type ex1-suht wr pmc rd wr port pmn pmcmn wr pu pumn wr pm pmmn wr pfc pfcmn ev dd p-ch output latch (pmn) address input signal of alternate function 2 alternate-function input signal in port mode internal bus sel...

Page 115

Chapter 4 port functions user’s manual u16896ej2v0ud 115 figure 4-17. Block diagram of type ex1-suil wr pmc rd wr port pmn pmcmn wr pfc pfcmn wr pu pumn wr pm pmmn wr intf intfmn note 1 wr intr intrmn note 1 ev dd p-ch output latch (pmn) note 2 address input signal of alternate function 2 noise elim...

Page 116

Chapter 4 port functions user’s manual u16896ej2v0ud 116 figure 4-18. Block diagram of type ex1-sul wr pmc rd wr port pmn pmcmn wr pu pumn wr pm pmmn wr pfc pfcmn ev dd p-ch output latch (pmn) address input signal of alternate function 2 internal bus selector selector.

Page 117

Chapter 4 port functions user’s manual u16896ej2v0ud 117 figure 4-19. Block diagram of type ex2-sufl wr pmc rd address input signal of alternate function 2 output signal of alternate function 2 wr port pmn note pmcmn wr pfc pfcmn wr pu pumn wr pm pmmn wr pf pfmn ev dd p-ch ev dd ev ss p-ch n-ch outp...

Page 118

Chapter 4 port functions user’s manual u16896ej2v0ud 118 figure 4-20. Block diagram of type gxx10-sul p-ch wr pmc rd wr port pmn note pmcmn wr pfce pfcemn wr pm pmmn wr pfc pfcmn wr pu pumn ev dd address input signal of alternate function 3 output signal of alternate function 4 output latch (pmn) in...

Page 119

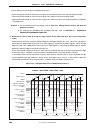

Chapter 4 port functions user’s manual u16896ej2v0ud 119 4.5 port register setting when alternate function is used table 4-12 shows the port register settings when each port is used for an alternate function. When using a port pin as an alternate-function pin, refer to description of each pin..

Page 120

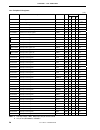

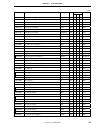

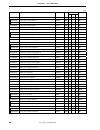

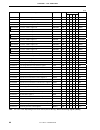

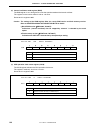

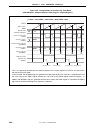

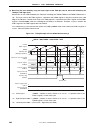

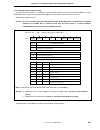

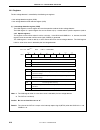

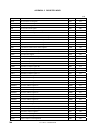

Chapter 4 p o rt fu ncti o ns user’s manual u1 6896ej2v0ud 120 other bits (registers) – – – – – – – – – – – – – – – – – – – pfcnx bit of pfcn register – – – pfc03 = 0 – – – pfc30 = 0 note 1, pfc31 = 0 note 1, pfc31 = 0 note 2, pfc32 = 0 note 2, pfc32 = 0 pfc32 = 1 pfc33 = 0 pfc33 = 1 pfc34 = 0 pfc34...

Page 121

Chapter 4 p o rt fu ncti o ns user’s manual u1 6896ej2v0ud 121 table 4-12. Settings when port pins are used for alternate functions (2/3) other bits (registers) – – pf38 (pf3h) = 1 pf39 (pf3h) = 1 – – krm0 (krm) = 1 – – krm1 (krm) = 1 – – krm2 (krm) = 1 – krm3 (krm) = 1 pf54 (pf5) = 0 pf55 (pf5) = 0...

Page 122

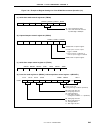

Chapter 4 p o rt fu ncti o ns user’s manual u1 6896ej2v0ud 122 table 4-12. Settings when port pins are used for alternate functions (3/3) other bits (registers) krm6 (krm) = 1 krm7 (krm) = 1 pf98 (pf9) = don’t care pf98 (pf9) = don’t care pfcnx bit of pfcn register pfc90 = 1 pfc90 = setting not requ...

Page 123

Chapter 4 port functions user’s manual u16896ej2v0ud 123 4.6 cautions 4.6.1 cautions on bit manipulation instruction for port n register (pn) when a 1-bit manipulation instruction is executed on a port that provides both input and output functions, the value of the output latch of an input port that...

Page 124

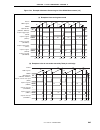

Chapter 4 port functions user’s manual u16896ej2v0ud 124 4.6.2 hysteresis characteristics in port mode, the following ports do not have hysteresis characteristics. P02 to p06 p31 to p35, p38, p39 p40, p42 p97, p99, p913 to p915.

Page 125

User’s manual u16896ej2v0ud 125 chapter 5 clock generation function 5.1 overview the following clock generation functions are available. { main clock oscillator ×4) mode> • f x = 2 to 5 mhz (f xx = 8 to 20 mhz: 4.5 v ≤ v dd ≤ 5.5 v) • f x = 2 to 4 mhz (f xx = 8 to 16 mhz: 4.0 v ≤ v dd ≤ 5.5 v) • f x...

Page 126

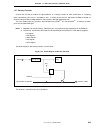

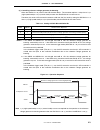

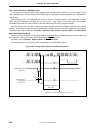

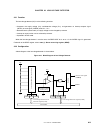

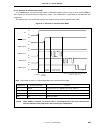

Chapter 5 clock generation function user’s manual u16896ej2v0ud 126 5.2 configuration figure 5-1. Clock generator internal oscillator intbrg clkout x1 x2 1/256 1/8 pll f xx /32 f xx /16 f xx /8 f xx /4 f xx /2 f xx f clk f xt f xx f x f r /8 f r frc bit subclock oscillator xt1 xt2 f xt interval time...

Page 127

Chapter 5 clock generation function user’s manual u16896ej2v0ud 127 (1) main clock oscillator the main clock oscillator oscillates the following frequencies (f x ). • f x = 2 to 5 mhz (v dd = 4.5 to 5.5 v, in pll mode) • f x = 2 to 4 mhz (v dd = 4.0 to 5.5 v, in pll mode) • f x = 2 to 2.5 mhz (v dd ...

Page 128

Chapter 5 clock generation function user’s manual u16896ej2v0ud 128 5.3 registers (1) processor clock control register (pcc) the pcc register is a special register. Data can be written to this register only in combination of specific sequences (refer to 3.4.7 special registers). This register can be...

Page 129

Chapter 5 clock generation function user’s manual u16896ej2v0ud 129 (2/2) f xx f xx /2 f xx /4 f xx /8 (default value) f xx /16 f xx /32 setting prohibited f xt ck2 0 0 0 0 1 1 1 × clock selection (f clk /f cpu ) ck1 0 0 1 1 0 0 1 × ck0 0 1 0 1 0 1 × × ck3 0 0 0 0 0 0 0 1 cautions 1. Do not change t...

Page 130

Chapter 5 clock generation function user’s manual u16896ej2v0ud 130 (a) example of setting main clock operation → subclock operation ck3 bit ← 1: use of a bit manipulation instruction is recommended. Do not change the ck2 to ck0 bits. Subclock operation: read the cls bit to check if subclock operati...

Page 131

Chapter 5 clock generation function user’s manual u16896ej2v0ud 131 (b) example of setting subclock operation → main clock operation mck bit ← 0: main clock starts oscillating insert waits by the program and wait until the oscillation stabilization time of the main clock elapses. Ck3 bit ← 0: use of...

Page 132

Chapter 5 clock generation function user’s manual u16896ej2v0ud 132 (2) internal oscillation mode register (rcm) the rcm register is an 8-bit register that sets the operation mode of the internal oscillator. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00...

Page 133

Chapter 5 clock generation function user’s manual u16896ej2v0ud 133 5.4 operation 5.4.1 operation of each clock the following table shows the operation status of each clock. Table 5-1. Operation status of each clock pcc register cls bit = 0, mck bit = 0 cls bit = 1, mck bit = 0 cls bit = 1, mck bit ...

Page 134

Chapter 5 clock generation function user’s manual u16896ej2v0ud 134 5.5 pll function 5.5.1 overview the pll function is used to output the operating clock of the cpu and on-chip peripheral function at a frequency 4 times higher than the oscillation frequency, and select the clock-through mode. When ...

Page 135

Chapter 5 clock generation function user’s manual u16896ej2v0ud 135 5.5.3 usage (1) when pll is used • after reset has been released, the pll operates (pllctl.Pllon bit = 1), but because the default mode is the clock-through mode (pllctl.Selpll bit = 0), select the pll mode (selpll bit = 1). • to se...

Page 136

User’s manual u16896ej2v0ud 136 chapter 6 16-bit timer/event counter p (tmp) timer p (tmp) is a 16-bit timer/event counter. The v850es/ke1+ incorporates tmp0. 6.1 overview an outline of tmp0 is shown below. • clock selection: 8 ways • capture trigger input pins: 2 • external event count input pins: ...

Page 137

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 137 6.3 configuration tmp0 includes the following hardware. Table 6-1. Configuration of tmp0 item configuration timer register 16-bit counter registers tmp0 capture/compare registers 0, 1 (tp0ccr0, tp0ccr1) tmp0 counter read bu...

Page 138

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 138 (1) 16-bit counter this 16-bit counter can count internal clocks or external events. The count value of this counter can be read by using the tp0cnt register. When the tp0ctl0.Tp0ce bit = 0, the value of the 16-bit counter ...

Page 139

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 139 6.4 registers (1) tmp0 control register 0 (tp0ctl0) the tp0ctl0 register is an 8-bit register that controls the operation of tmp0. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00...

Page 140

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 140 (2) tmp0 control register 1 (tp0ctl1) the tp0ctl1 register is an 8-bit register that controls the operation of tmp0. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00h. 0 tp0est 0 ...

Page 141

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 141 (3) tmp0 i/o control register 0 (tp0ioc0) the tp0ioc0 register is an 8-bit register that controls the timer output (top00, top01 pins). This register can be read or written in 8-bit or 1-bit units. Reset sets this register ...

Page 142

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 142 (4) tmp0 i/o control register 1 (tp0ioc1) the tp0ioc1 register is an 8-bit register that controls the valid edge of the capture trigger input signals (tip00, tip01 pins). This register can be read or written in 8-bit or 1-b...

Page 143

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 143 (5) tmp0 i/o control register 2 (tp0ioc2) the tp0ioc2 register is an 8-bit register that controls the valid edge of the external event count input signal (tip00 pin) and external trigger input signal (tip00 pin). This regis...

Page 144

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 144 (6) tmp0 option register 0 (tp0opt0) the tp0opt0 register is an 8-bit register used to set the capture/compare operation and detect an overflow. This register can be read or written in 8-bit or 1-bit units. Reset sets this ...

Page 145

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 145 (7) tmp0 capture/compare register 0 (tp0ccr0) the tp0ccr0 register can be used as a capture register or a compare register depending on the mode. This register can be used as a capture register or a compare register only in...

Page 146

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 146 (a) function as compare register the tp0ccr0 register can be rewritten even when the tp0ctl0.Tp0ce bit = 1. The set value of the tp0ccr0 register is transferred to the ccr0 buffer register. When the value of the 16-bit coun...

Page 147

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 147 (8) tmp0 capture/compare register 1 (tp0ccr1) the tp0ccr1 register can be used as a capture register or a compare register depending on the mode. This register can be used as a capture register or a compare register only in...

Page 148

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 148 (a) function as compare register the tp0ccr1 register can be rewritten even when the tp0ctl0.Tp0ce bit = 1. The set value of the tp0ccr1 register is transferred to the ccr1 buffer register. When the value of the 16-bit coun...

Page 149

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 149 (9) tmp0 counter read buffer register (tp0cnt) the tp0cnt register is a read buffer register that can read the count value of the 16-bit counter. If this register is read when the tp0ctl0.Tp0ce bit = 1, the count value of t...

Page 150

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 150 6.5 operation tmp0 can perform the following operations. Operation tp0ctl1.Tp0est bit (software trigger bit) tip00 pin (external trigger input) capture/compare register setting compare register write interval timer mode inv...

Page 151

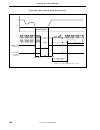

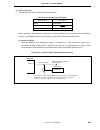

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 151 6.5.1 interval timer mode (tp0md2 to tp0md0 bits = 000) in the interval timer mode, an interrupt request signal (inttp0cc0) is generated at the specified interval if the tp0ctl0.Tp0ce bit is set to 1. A square wave whose ha...

Page 152

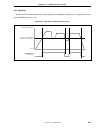

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 152 when the tp0ce bit is set to 1, the value of the 16-bit counter is cleared from ffffh to 0000h in synchronization with the count clock, and the counter starts counting. At this time, the output of the top00 pin is inverted....

Page 153

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 153 figure 6-4. Register setting for interval timer mode operation (2/2) (c) tmp0 i/o control register 0 (tp0ioc0) 0 0 0 0 0/1 tp0ioc0 0: disable top00 pin output 1: enable top00 pin output setting of output level with operatio...

Page 154

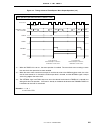

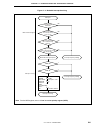

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 154 (1) interval timer mode operation flow figure 6-5. Software processing flow in interval timer mode ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register top00 pin output inttp0cc0 signal d 0 d 0 d 0 d 0 tp0ce bit = 1 tp0ce ...

Page 155

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 155 (2) interval timer mode operation timing (a) operation if tp0ccr0 register is cleared to 0000h if the tp0ccr0 register is cleared to 0000h, the inttp0cc0 signal is generated at each count clock, and the output of the top00 ...

Page 156

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 156 (b) operation if tp0ccr0 register is set to ffffh if the tp0ccr0 register is set to ffffh, the 16-bit counter counts up to ffffh. The counter is cleared to 0000h in synchronization with the next count-up timing. The inttp0c...

Page 157

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 157 (c) notes on rewriting tp0ccr0 register to change the value of the tp0ccr0 register to a smaller value, stop counting once and then change the set value. If the value of the tp0ccr0 register is rewritten to a smaller value ...

Page 158

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 158 (d) operation of tp0ccr1 register figure 6-6. Configuration of tp0ccr1 register ccr0 buffer register tp0ccr0 register tp0ccr1 register ccr1 buffer register top00 pin inttp0cc0 signal top01 pin inttp0cc1 signal 16-bit counte...

Page 159

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 159 if the set value of the tp0ccr1 register is less than the set value of the tp0ccr0 register, the inttp0cc1 signal is generated once per cycle. At the same time, the output of the top01 pin is inverted. The top01 pin outputs...

Page 160

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 160 if the set value of the tp0ccr1 register is greater than the set value of the tp0ccr0 register, the count value of the 16-bit counter does not match the value of the tp0ccr1 register. Consequently, the inttp0cc1 signal is n...

Page 161

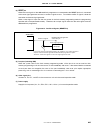

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 161 6.5.2 external event count mode (tp0md2 to tp0md0 bits = 001) in the external event count mode, the valid edge of the external event count input is counted when the tp0ctl0.Tp0ce bit is set to 1, and an interrupt request si...

Page 162

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 162 when the tp0ce bit is set to 1, the value of the 16-bit counter is cleared from ffffh to 0000h. The counter counts each time the valid edge of external event count input is detected. Additionally, the set value of the tp0cc...

Page 163

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 163 figure 6-11. Register setting for operation in external event count mode (2/2) (e) tmp0 counter read buffer register (tp0cnt) the count value of the 16-bit counter can be read by reading the tp0cnt register. (f) tmp0 captur...

Page 164

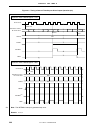

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 164 (1) external event count mode operation flow figure 6-12. Flow of software processing in external event count mode ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register inttp0cc0 signal d 0 d 0 d 0 d 0 tp0ce bit = 1 tp0ce b...

Page 165

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 165 (2) operation timing in external event count mode cautions 1. In the external event count mode, do not set the tp0ccr0 and tp0ccr1 registers to 0000h. 2. In the external event count mode, use of the timer output is disabled...

Page 166

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 166 (b) notes on rewriting the tp0ccr0 register to change the value of the tp0ccr0 register to a smaller value, stop counting once and then change the set value. If the value of the tp0ccr0 register is rewritten to a smaller va...

Page 167

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 167 (c) operation of tp0ccr1 register figure 6-13. Configuration of tp0ccr1 register ccr0 buffer register tp0ce bit tp0ccr0 register 16-bit counter tp0ccr1 register ccr1 buffer register clear match signal match signal inttp0cc0...

Page 168

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 168 if the set value of the tp0ccr1 register is greater than the set value of the tp0ccr0 register, the inttp0cc1 signal is not generated because the count value of the 16-bit counter and the value of the tp0ccr1 register do no...

Page 169

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 169 6.5.3 external trigger pulse output mode (tp0md2 to tp0md0 bits = 010) in the external trigger pulse output mode, 16-bit timer/event counter p waits for a trigger when the tp0ctl0.Tp0ce bit is set to 1. When the valid edge ...

Page 170

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 170 figure 6-17. Basic timing in external trigger pulse output mode external trigger input (tip00 pin input) top00 pin output (software trigger) d 1 d 0 d 0 d 1 d 1 d 1 d 1 d 0 d 0 d 0 wait for trigger active level width (d 1 )...

Page 171

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 171 figure 6-18. Setting of registers in external trigger pulse output mode (1/2) (a) tmp0 control register 0 (tp0ctl0) 0/1 0 0 0 0 tp0ctl0 select count clock note 0: stop counting 1: enable counting 0/1 0/1 0/1 tp0cks2 tp0cks1...

Page 172

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 172 figure 6-18. Setting of registers in external trigger pulse output mode (2/2) (d) tmp0 i/o control register 2 (tp0ioc2) 0 0 0 0 0/1 tp0ioc2 select valid edge of external trigger input select valid edge of external event cou...

Page 173

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 173 (1) operation flow in external trigger pulse output mode figure 6-19. Software processing flow in external trigger pulse output mode (1/2) ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register ccr0 buffer register inttp0cc0...

Page 174

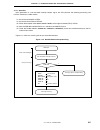

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 174 figure 6-19. Software processing flow in external trigger pulse output mode (2/2) tp0ce bit = 1 setting of tp0ccr0 register register initial setting tp0ctl0 register (tp0cks0 to tp0cks2 bits) tp0ctl1 register, tp0ioc0 regis...

Page 175

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 175 (2) external trigger pulse output mode operation timing (a) note on changing pulse width during operation to change the pwm waveform while the counter is operating, write the tp0ccr1 register last. Rewrite the tp0ccra regis...

Page 176

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 176 in order to transfer data from the tp0ccra register to the ccra buffer register, the tp0ccr1 register must be written. To change both the cycle and active level width of the pwm waveform at this time, first set the cycle to...

Page 177

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 177 (b) 0%/100% output of pwm waveform to output a 0% waveform, clear the tp0ccr1 register to 0000h. If the set value of the tp0ccr0 register is ffffh, the inttp0cc1 signal is generated periodically. Count clock 16-bit counter ...

Page 178

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 178 (c) conflict between trigger detection and match with tp0ccr1 register if the trigger is detected immediately after the inttp0cc1 signal is generated, the 16-bit counter is immediately cleared to 0000h, the output signal of...

Page 179

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 179 (d) conflict between trigger detection and match with tp0ccr0 register if the trigger is detected immediately after the inttp0cc0 signal is generated, the 16-bit counter is cleared to 0000h and continues counting up. Theref...

Page 180

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 180 (e) generation timing of compare match interrupt request signal (inttp0cc1) the timing of generation of the inttp0cc1 signal in the external trigger pulse output mode differs from the timing of other inttp0cc1 signals; the ...

Page 181

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 181 6.5.4 one-shot pulse output mode (tp0md2 to tp0md0 bits = 011) in the one-shot pulse output mode, 16-bit timer/event counter p waits for a trigger when the tp0ctl0.Tp0ce bit is set to 1. When the valid edge of an external t...

Page 182

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 182 figure 6-21. Basic timing in one-shot pulse output mode ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register inttp0cc0 signal tp0ccr1 register inttp0cc1 signal top01 pin output external trigger input (tip00 pin input) d 1 ...

Page 183

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 183 figure 6-22. Setting of registers in one-shot pulse output mode (1/2) (a) tmp0 control register 0 (tp0ctl0) 0/1 0 0 0 0 tp0ctl0 select count clock note 0: stop counting 1: enable counting 0/1 0/1 0/1 tp0cks2 tp0cks1 tp0cks0...

Page 184

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 184 figure 6-22. Setting of registers in one-shot pulse output mode (2/2) (d) tmp0 i/o control register 2 (tp0ioc2) 0 0 0 0 0/1 tp0ioc2 select valid edge of external trigger input select valid edge of external event count input...

Page 185

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 185 (1) operation flow in one-shot pulse output mode figure 6-23. Software processing flow in one-shot pulse output mode ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register inttp0cc0 signal tp0ccr1 register inttp0cc1 signal t...

Page 186

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 186 (2) operation timing in one-shot pulse output mode (a) note on rewriting tp0ccra register to change the set value of the tp0ccra register to a smaller value, stop counting once, and then change the set value. If the value o...

Page 187

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 187 (b) generation timing of compare match interrupt request signal (inttp0cc1) the generation timing of the inttp0cc1 signal in the one-shot pulse output mode is different from other inttp0cc1 signals; the inttp0cc1 signal is ...

Page 188

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 188 6.5.5 pwm output mode (tp0md2 to tp0md0 bits = 100) in the pwm output mode, a pwm waveform is output from the top01 pin when the tp0ctl0.Tp0ce bit is set to 1. In addition, a pulse with one cycle of the pwm waveform as half...

Page 189

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 189 figure 6-25. Basic timing in pwm output mode ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register ccr0 buffer register inttp0cc0 signal top00 pin output tp0ccr1 register ccr1 buffer register inttp0cc1 signal top01 pin outp...

Page 190

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 190 figure 6-26. Register setting in pwm output mode (1/2) (a) tmp0 control register 0 (tp0ctl0) 0/1 0 0 0 0 tp0ctl0 select count clock note 0: stop counting 1: enable counting 0/1 0/1 0/1 tp0cks2 tp0cks1 tp0cks0 tp0ce note the...

Page 191

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 191 figure 6-26. Register setting in pwm output mode (2/2) (d) tmp0 i/o control register 2 (tp0ioc2) 0 0 0 0 0/1 tp0ioc2 select valid edge of external event count input. 0/1 0 0 tp0ees0 tp0ets1 tp0ets0 tp0ees1 (e) tmp0 counter ...

Page 192

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 192 (1) operation flow in pwm output mode figure 6-27. Software processing flow in pwm output mode (1/2) ffffh 16-bit counter 0000h tp0ce bit tp0ccr0 register ccr0 buffer register inttp0cc0 signal top00 pin output tp0ccr1 regis...

Page 193

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 193 figure 6-27. Software processing flow in pwm output mode (2/2) tp0ce bit = 1 setting of tp0ccr0 register register initial setting tp0ctl0 register (tp0cks0 to tp0cks2 bits) tp0ctl1 register, tp0ioc0 register, tp0ioc2 regist...

Page 194

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 194 (2) pwm output mode operation timing (a) changing pulse width during operation to change the pwm waveform while the counter is operating, write the tp0ccr1 register last. Rewrite the tp0ccra register after writing the tp0cc...

Page 195

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 195 (b) 0%/100% output of pwm waveform to output a 0% waveform, set the tp0ccr1 register to 0000h. If the set value of the tp0ccr0 register is ffffh, the inttp0cc1 signal is generated periodically. Count clock 16-bit counter tp...

Page 196

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 196 (c) generation timing of compare match interrupt request signal (inttp0cc1) the timing of generation of the inttp0cc1 signal in the pwm output mode differs from the timing of other inttp0cc1 signals; the inttp0cc1 signal is...

Page 197

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 197 6.5.6 free-running timer mode (tp0md2 to tp0md0 bits = 101) in the free-running timer mode, 16-bit timer/event counter p starts counting when the tp0ctl0.Tp0ce bit is set to 1. At this time, the tp0ccra register can be used...

Page 198

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 198 when the tp0ce bit is set to 1, 16-bit timer/event counter p starts counting, and the output signals of the top00 and top01 pins are inverted. When the count value of the 16-bit counter later matches the set value of the tp...

Page 199

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 199 when the tp0ce bit is set to 1, the 16-bit counter starts counting. When the valid edge input to the tip0a pin is detected, the count value of the 16-bit counter is stored in the tp0ccra register, and a capture interrupt re...

Page 200

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 200 figure 6-31. Register setting in free-running timer mode (1/2) (a) tmp0 control register 0 (tp0ctl0) 0/1 0 0 0 0 tp0ctl0 select count clock note 0: stop counting 1: enable counting 0/1 0/1 0/1 tp0cks2 tp0cks1 tp0cks0 tp0ce ...

Page 201

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 201 figure 6-31. Register setting in free-running timer mode (2/2) (d) tmp0 i/o control register 1 (tp0ioc1) 0 0 0 0 0/1 tp0ioc1 select valid edge of tip00 pin input select valid edge of tip01 pin input 0/1 0/1 0/1 tp0is2 tp0is...

Page 202

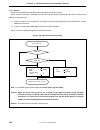

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 202 (1) operation flow in free-running timer mode (a) when using capture/compare register as compare register figure 6-32. Software processing flow in free-running timer mode (compare function) (1/2) ffffh 16-bit counter 0000h ...

Page 203

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 203 figure 6-32. Software processing flow in free-running timer mode (compare function) (2/2) tp0ce bit = 1 read tp0opt0 register (check overflow flag). Register initial setting tp0ctl0 register (tp0cks0 to tp0cks2 bits) tp0ctl...

Page 204

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 204 (b) when using capture/compare register as capture register figure 6-33. Software processing flow in free-running timer mode (capture function) (1/2) ffffh 16-bit counter 0000h tp0ce bit tip00 pin input tp0ccr0 register int...

Page 205

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 205 figure 6-33. Software processing flow in free-running timer mode (capture function) (2/2) tp0ce bit = 1 read tp0opt0 register (check overflow flag). Register initial setting tp0ctl0 register (tp0cks0 to tp0cks2 bits) tp0ctl...

Page 206

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 206 (2) operation timing in free-running timer mode (a) interval operation with compare register when 16-bit timer/event counter p is used as an interval timer with the tp0ccra register used as a compare register, software proc...

Page 207

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 207 (b) pulse width measurement with capture register when pulse width measurement is performed with the tp0ccra register used as a capture register, software processing is necessary for reading the capture register each time t...

Page 208

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 208 (c) processing of overflow when two capture registers are used care must be exercised in processing the overflow flag when two capture registers are used. First, an example of incorrect processing is shown below. Example of...

Page 209

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 209 (1/2) example when two capture registers are used (using overflow interrupt) ffffh 16-bit counter 0000h tp0ce bit inttp0ov signal tp0ovf bit tp0ovf0 flag note tip00 pin input tp0ccr0 register tp0ovf1 flag note tip01 pin inp...

Page 210

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 210 (2/2) example when two capture registers are used (without using overflow interrupt) ffffh 16-bit counter 0000h tp0ce bit inttp0ov signal tp0ovf bit tp0ovf0 flag note tip00 pin input tp0ccr0 register tp0ovf1 flag note tip01...

Page 211

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 211 (d) processing of overflow if capture trigger interval is long if the pulse width is greater than one cycle of the 16-bit counter, care must be exercised because an overflow may occur more than once from the first capture t...

Page 212

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 212 example when capture trigger interval is long ffffh 16-bit counter 0000h tp0ce bit tip0a pin input tp0ccra register inttp0ov signal tp0ovf bit overflow counter note d a0 d a1 1h 0h 2h 0h d a0 d a1 1 cycle of 16-bit counter ...

Page 213

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 213 (e) clearing overflow flag the overflow flag can be cleared to 0 by clearing the tp0ovf bit to 0 with the clr instruction and by writing 8-bit data (bit 0 is 0) to the tp0opt0 register. To accurately detect an overflow, rea...

Page 214

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 214 6.5.7 pulse width measurement mode (tp0md2 to tp0md0 bits = 110) in the pulse width measurement mode, 16-bit timer/event counter p starts counting when the tp0ctl0.Tp0ce bit is set to 1. Each time the valid edge input to th...

Page 215

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 215 figure 6-35. Basic timing in pulse width measurement mode ffffh 16-bit counter 0000h tp0ce bit tip0a pin input tp0ccra register inttp0cca signal inttp0ov signal tp0ovf bit d 0 0000h d 1 d 2 d 3 cleared to 0 by clr instructi...

Page 216

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 216 figure 6-36. Register setting in pulse width measurement mode (1/2) (a) tmp0 control register 0 (tp0ctl0) 0/1 0 0 0 0 tp0ctl0 select count clock note 0: stop counting 1: enable counting 0/1 0/1 0/1 tp0cks2 tp0cks1 tp0cks0 t...

Page 217

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 217 figure 6-36. Register setting in pulse width measurement mode (2/2) (e) tmp0 option register 0 (tp0opt0) 0 0 0 0 0 tp0opt0 overflow flag 0 0 0/1 tp0ccs0 tp0ovf tp0ccs1 (f) tmp0 counter read buffer register (tp0cnt) the valu...

Page 218

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 218 (1) operation flow in pulse width measurement mode figure 6-37. Software processing flow in pulse width measurement mode set tp0ctl0 register (tp0ce bit = 1) tp0ce bit = 0 register initial setting tp0ctl0 register (tp0cks0 ...

Page 219

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 219 (2) operation timing in pulse width measurement mode (a) clearing overflow flag the overflow flag can be cleared to 0 by clearing the tp0ovf bit to 0 with the clr instruction and by writing 8-bit data (bit 0 is 0) to the tp...

Page 220

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 220 6.5.8 timer output operations the following table shows the operations and output levels of the top00 and top01 pins. Table 6-4. Timer output control in each mode operation mode top01 pin top00 pin interval timer mode squar...

Page 221

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 221 6.6 eliminating noise on capture trigger input pin (tip0a) the tip0a pin has a digital noise eliminator. However, this circuit is valid only when the pin is used as a capture trigger input pin; it is invalid when the pin is...

Page 222

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 222 select the number of times of sampling and the sampling clock by using the panfc register. Select the alternate function (of the tip0a pin) by using the pmc3, pfc3, and pfce3 registers. Set the operating mode of tmp0 (such ...

Page 223

Chapter 6 16-bit timer/event counter p (tmp) user’s manual u16896ej2v0ud 223 6.7 cautions (1) capture operation when the capture operation is used and f xx /8, f xx /16, f xx /32, f xx /64, f xx /128, or the external event counter (tp0ctl1.Tp0eee bit = 1) is selected as the count clock, ffffh, not 0...

Page 224

User’s manual u16896ej2v0ud 224 chapter 7 16-bit timer/event counter 0 in the v850es/ke1+, one channel of 16-bit timer/event counter 0 is provided. 7.1 functions 16-bit timer/event counter 01 has the following functions. (1) interval timer 16-bit timer/event counter 01 generates an interrupt request...

Page 225

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 225 7.2 configuration 16-bit timer/event counter 01 includes the following hardware. Table 7-1. Configuration of 16-bit timer/event counter 01 item configuration time/counter 16-bit timer counter 01 (tm01) register 16-bit timer captu...

Page 226

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 226 (1) 16-bit timer counter 01 (tm01) the tm01 register is a 16-bit read-only register that counts count pulses. The counter is incremented in synchronization with the rising edge of the count clock. Tm01 12 10 8 6 4 2 after reset: ...

Page 227

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 227 (2) 16-bit timer capture/compare register 010 (cr010), 16-bit timer capture/compare register 011 (cr011) the cr010 and cr011 registers are 16-bit registers that are used with a capture function or comparison function selected by ...

Page 228

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 228 (b) 16-bit timer capture/compare register 011 (cr011) cr011 12 10 8 6 4 2 after reset: 0000h r/w address: fffff614h 14 0 13 11 9 7 5 3 15 1 (i) when using the cr011 register as a compare register the value set to the cr011 regist...

Page 229

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 229 (c) setting range when used as compare register when the cr010 or cr011 register is used as a compare register, set it as shown below. Operation cr010 register cr011 register • operation as interval timer • operation as square-wa...

Page 230

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 230 table 7-2. Capture operation of cr010 and cr011 registers external input signal capture operation ti010 pin input ti011 pin input set values of es101 and es100 position of edge to be captured set values of es111 and es110 positio...

Page 231

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 231 7.3 registers registers used to control 16-bit timer/event counter 01 are shown below. • 16-bit timer mode control register 01 (tmc01) • capture/compare control register 01 (crc01) • 16-bit timer output control register 01 (toc01...

Page 232

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 232 after reset: 00h r/w address: fffff616h 7 6 5 4 3 2 1 tmc01 0 0 0 0 tmc013 tmc012 tmc011 ovf01 tmc013 tmc012 enable operation of 16-bit timer/event counter 01 0 0 disables tm01 operation. Stops supplying operating clock. Clears 1...

Page 233

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 233 (2) capture/compare control register 01 (crc01) the crc01 register is the register that controls the operation of the cr010 and cr011 registers. Changing the value of the crc01 register is prohibited during operation (when the tm...

Page 234

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 234 (3) 16-bit timer output control register 01 (toc01) the toc01 register is an 8-bit register that controls the to01 pin output. The toc01 register can be rewritten while only the ospt01 bit is operating (when the tmc01.Tmc013 and ...

Page 235

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 235 (2/2) lvs01 lvr01 setting of to01 pin output status 0 0 no change 0 1 initial value of to01 pin output is low level (to01 pin output is cleared to 0). 1 0 initial value of to01 pin output is high level (to01 pin output is set to ...

Page 236

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 236 (4) prescaler mode register 01 (prm01) the prm01 register is the register that sets the tm01 register count clock and ti010 and ti011 pin input valid edges. The prm011 and prm010 bits are set in combination with the selcnt1.Isel1...

Page 237

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 237 (5) selector operation control register 1 (selcnt1) the selcnt1 register sets the count clock of 16-bit timer/event counter 01. The selcnt1 register is set in combination with the prm01.Prm101 and prm01.Prm100 bits. Refer to 7.3 ...

Page 238

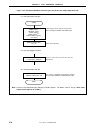

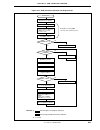

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 238 7.4 operation 7.4.1 interval timer operation if the tmc01.Tmc013 and tmc01.Tmc012 bits are set to 11 (clear & start mode entered upon a match between the tm01 register and the cr010 register), the count operation is started in sy...

Page 239

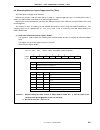

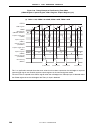

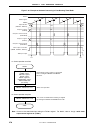

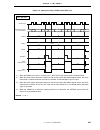

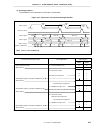

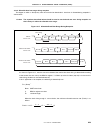

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 239 figure 7-4. Example of register settings for interval timer operation (a) 16-bit timer mode control register 01 (tmc01) 0 0 0 0 1 1 0 0 tmc013 tmc012 tmc011 ovf01 clears and starts on match between tm01 and cr010. (b) capture/com...

Page 240

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 240 figure 7-5. Example of software processing for interval timer function tm01 register 0000h operable bits (tmc013, tmc012) compare register (cr010) compare match interrupt (inttm010) n 11 00 00 n n n tmc013, tmc012 bits = 11 tmc01...

Page 241

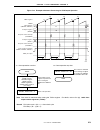

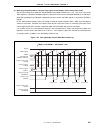

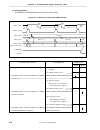

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 241 7.4.2 square wave output operation when 16-bit timer/event counter 01 operates as an interval timer (refer to 7.4.1), a square wave can be output from the to01 pin by setting the toc01 register to 03h. When the tmc01.Tmc013 and t...

Page 242

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 242 figure 7-8. Example of register settings for square wave output operation (a) 16-bit timer mode control register 01 (tmc01) 0 0 0 0 1 1 0 0 tmc013 tmc012 tmc011 ovf01 clears and starts on match between tm01 and cr010. (b) capture...

Page 243

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 243 figure 7-9. Example of software processing for square wave output function tm01 register 0000h operable bits (tmc013, tmc012) compare register (cr010) to01 pin output compare match interrupt (inttm010) to01 output control bit (to...

Page 244

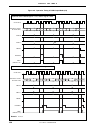

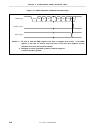

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 244 7.4.3 external event counter operation when the prm01.Prm011 and prm01.Prm010 bits are set to 11 (for counting up with the valid edge of the ti010 pin) and the tmc01.Tmc013 and tmc01.Tmc012 bits are set to 11, the valid edge of a...

Page 245

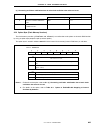

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 245 figure 7-11. Example of register settings in external event counter mode (a) 16-bit timer mode control register 01 (tmc01) 0 0 0 0 1 1 0 0 tmc013 tmc012 tmc011 ovf01 clears and starts on match between tm01 and cr010. (b) capture/...

Page 246

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 246 figure 7-12. Example of software processing in external event counter mode compare register (cr010) operable bits (tmc013, tmc012) 0000h tm01 register to01 pin output compare match interrupt (inttm010) to01 output control bit (to...

Page 247

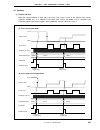

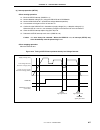

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 247 7.4.4 operation in clear & start mode entered by ti010 pin valid edge input when the tmc01.Tmc013 and tmc01.Tmc012 bits are set to 10 (clear & start mode entered by the ti010 pin valid edge input) and the count clock (set by the ...

Page 248

Chapter 7 16-bit timer/event counter 0 user’s manual u16896ej2v0ud 248 (1) operation in clear & start mode entered by ti010 pin valid edge input (cr010 register: compare register, cr011 register: compare register) figure 7-13. Block diagram of clear & start mode entered by ti010 pin valid edge input...

Page 249