- DL manuals

- NEC

- Computer Hardware

- PD789488

- User Manual

NEC PD789488 User Manual

Summary of PD789488

Page 1

User’s manual µ pd789488 µ pd789489 µ pd78f9488 µ pd78f9489 µ pd789489 subseries 8-bit single-chip microcontrollers printed in japan document no. U15331ej4v1ud00 (4th edition) date published july 2005 ns cp(k) ©.

Page 2

2 user’s manual u15331ej4v1ud [memo].

Page 3

User’s manual u15331ej4v1ud 3 1 2 3 4 voltage application waveform at input pin waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the cmos device stays in the area between v il (max) and v ih (min) due to noise, etc., the device may malfunction. Take c...

Page 4

4 user’s manual u15331ej4v1ud eeprom and fip are trademarks of nec electronics corporation. Windows and windows nt are either registered trademarks or trademarks of microsoft corporation in the united states and/or other countries. Pc/at is a trademark of international business machines corporation....

Page 5

User’s manual u15331ej4v1ud 5 the information in this document is current as of july, 2005. The information is subject to change without notice. For actual design-in, refer to the latest publications of nec electronics data sheets or data books, etc., for the most up-to-date specifications of nec el...

Page 6: Regional Information

6 user’s manual u15331ej4v1ud regional information • device availability • ordering information • product release schedule • availability of related technical literature • development environment specifications (for example, specifications for third-party tools and components, host computers, power ...

Page 7

User’s manual u15331ej4v1ud 7 major revisions in this edition page description throughout change of descriptions of µ pd789489, 78f9489 • change of status from under development to development completed • change of the subseries name to “ µ pd789489 subseries” pp.31 to 33 update of 1.5 78k/0s series...

Page 8

8 user’s manual u15331ej4v1ud introduction target readers this manual is intended for user engineers who wish to understand the functions of the µ pd789489 subseries and design and develop application systems and programs for these devices. Target products: • µ pd789489 subseries: µ pd789488, 789489...

Page 9

User’s manual u15331ej4v1ud 9 conventions data significance: higher digits on the left and lower digits on the right active low representation: xxx (overscore over pin or signal name) note: footnote for item marked with note in the text caution: information requiring particular attention remark: sup...

Page 10

10 user’s manual u15331ej4v1ud documents related to flash memory writing document name document no. Pg-fp3 flash memory programmer user’s manual u13502e pg-fp4 flash memory programmer user’s manual u15260e other related documents document name document no. Semiconductor selection guide - products an...

Page 11

User’s manual u15331ej4v1ud 11 contents chapter 1 general ..........................................................................................................................26 1.1 features ...........................................................................................................

Page 12

12 user’s manual u15331ej4v1ud 3.1.4 data memory addressing .............................................................................................................. 54 3.2 processor registers .........................................................................................................

Page 13

User’s manual u15331ej4v1ud 13 5.4.5 when subsystem clock is not used ............................................................................................. 104 5.4.6 subsystem clock ×4 multiplication circuit .......................................................................................

Page 14

14 user’s manual u15331ej4v1ud 9.4.1 operation as watchdog timer ...................................................................................................... 171 9.4.2 operation as interval timer .................................................................................................

Page 15

User’s manual u15331ej4v1ud 15 14.1 multiplier function...................................................................................................................267 14.2 multiplier configuration ...................................................................................................

Page 16

16 user’s manual u15331ej4v1ud chapter 20 mask options ...........................................................................................................331 chapter 21 instruction set ......................................................................................................332 2...

Page 17

User’s manual u15331ej4v1ud 17 list of figures (1/6) figure no. Title page 2-1 i/o circuit types ..........................................................................................................................................46 3-1 memory map ( µ pd789488).....................................

Page 18

18 user’s manual u15331ej4v1ud list of figures (2/6) figure no. Title page 5-5 format of subclock control register............................................................................................................99 5-6 subclock selection register format .......................................

Page 19

User’s manual u15331ej4v1ud 19 list of figures (3/6) figure no. Title page 7-21 timing of square-wave output with 16-bit resolution ..............................................................................149 7-22 timing of carrier generator operation (when cr60 = n, crh60 = m (m > n))............

Page 20

20 user’s manual u15331ej4v1ud list of figures (4/6) figure no. Title page 11-4 format of asynchronous serial interface mode register 20 ......................................................................191 11-5 format of asynchronous serial interface status register 20.............................

Page 21

User’s manual u15331ej4v1ud 21 list of figures (5/6) figure no. Title page 13-12 four-time-slice lcd display pattern and electrode connections ............................................................263 13-13 example of connecting four-time-slice lcd panel ..........................................

Page 22

22 user’s manual u15331ej4v1ud list of figures (6/6) figure no. Title page 17-3 releasing halt mode by reset input.....................................................................................................311 17-4 releasing stop mode by interrupt...............................................

Page 23

User’s manual u15331ej4v1ud 23 list of tables (1/3) table no. Title page 2-1 types of pin i/o circuits ..............................................................................................................................45 3-1 internal rom capacity..............................................

Page 24

24 user’s manual u15331ej4v1ud list of tables (2/3) table no. Title page 10-1 configuration of 10-bit a/d converter ........................................................................................................173 11-1 configuration of serial interface 20 .....................................

Page 25

User’s manual u15331ej4v1ud 25 list of tables (3/3) table no. Title page 21-1 operand identifiers and description methods ............................................................................................332 25-1 surface mounting type soldering conditions .....................................

Page 26

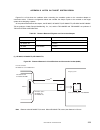

26 user’s manual u15331ej4v1ud chapter 1 general 1.1 features • rom and ram capacities item data memory part number program memory (rom) internal ram lcd display ram µ pd789488 mask rom µ pd78f9488 flash memory 32 kb 1024 bytes 28 × 4 bits µ pd789489 mask rom 1536 bytes µ pd78f9489 flash memory 48 k...

Page 27

Chapter 1 general user’s manual u15331ej4v1ud 27 1.3 ordering information part number package internal rom µ pd789488gc- ×××-8bt 80-pin plastic qfp (14 × 14) mask rom µ pd789488gk- ×××-9eu 80-pin plastic tqfp (fine pitch) (12 × 12) mask rom µ pd78f9488gc-8bt 80-pin plastic qfp (14 × 14) flash memory...

Page 28

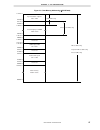

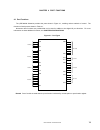

Chapter 1 general 28 user’s manual u15331ej4v1ud 1.4 pin configuration (top view) (1) µ pd789488, 78f9488 80-pin plastic qfp (14 × 14) µ pd789488gc- ×××-8bt µ pd78f9488gc-8bt µ pd789488gc- ×××-8bt-a µ pd78f9488gc-8bt-a 80-pin plastic tqfp (fine pitch) (12 × 12) µ pd789488gk- ×××-9eu µ pd78f9488gk-9e...

Page 29

Chapter 1 general user’s manual u15331ej4v1ud 29 cautions 1. Connect the ic (internally connected) pin directly to v ss . 2. Connect the av dd pin to v dd . 3. Connect the av ss pin to v ss . Remark the parenthesized values apply to the µ pd78f9488 (2) µ pd789489, 78f9489 80-pin plastic qfp (14 × 14...

Page 30

Chapter 1 general 30 user’s manual u15331ej4v1ud notes 1. Whether to use these pins as input port pins (p70 to p73) or segment outputs (s16 to s19) can be selected in 1-bit units by means of a mask option or port function register (refer to 4.3 (3) port function registers and chapter 20 mask options...

Page 31

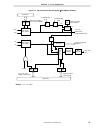

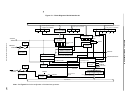

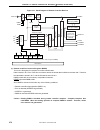

Chapter 1 general user’s manual u15331ej4v1ud 31 1.5 78k/0s series lineup the products in the 78k/0s series are listed below. The names enclosed in boxes are subseries names. 80-pin sio, 8-bit a/d converter, and resistance division type lcd (28 × 4) 52-pin 52-pin sio and resistance division type lcd...

Page 32

Chapter 1 general 32 user’s manual u15331ej4v1ud the major functional differences between the subseries are listed below. Series for general-purpose applications and lcd drive timer v dd function subseries name rom capacity 8-bit 16-bit watc h wdt 8-bit a/d 10-bit a/d serial interface i/o min. Value...

Page 33

Chapter 1 general user’s manual u15331ej4v1ud 33 series for assp timer v dd function subseries name rom capacity 8-bit 16-bit watc h wdt 8-bit a/d 10-bit a/d serial interface i/o min. Value remarks usb µ pd789800 8 kb 2 ch − − 1 ch − − 2 ch (usb: 1 ch) 31 4.0 v − inverter control µ pd789842 8 kb to ...

Page 34

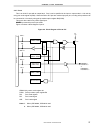

Chapter 1 general 34 user’s manual u15331ej4v1ud 1.6 block diagram 78k/0s cpu core rom (flash memory) ram v dd v ss ic0 (v pp ) cpt20/to20/p33 8-bit timer/ event counter 60 p00 to p07 port 0 p10 to p11 port 1 p20 to p25 port 2 p30 to p34 port 3 p50 to p53 port 5 p60 to p67 port 6 p70 to p73 note 1 p...

Page 35

Chapter 1 general user’s manual u15331ej4v1ud 35 1.7 overview of functions (1/2) item µ pd789488 µ pd78f9488 µ pd789489 µ pd78f9489 rom 32 kb 32 kb (flash memory) 48 kb 48 kb (flash memory) high-speed ram 1024 bytes low-speed ram − 512 bytes internal memory lcd display ram 28 bytes main system clock...

Page 36

Chapter 1 general 36 user’s manual u15331ej4v1ud (2/2) item µ pd789488 µ pd78f9488 µ pd789489 µ pd78f9489 supply voltage v dd = 1.8 to 5.5 v operating ambient temperature t a = −40 to +85°c package • 80-pin plastic qfp (14 × 14) • 80-pin plastic tqfp (fine pitch) (12 × 12) an outline of the timer is...

Page 37

User’s manual u15331ej4v1ud 37 chapter 2 pin functions 2.1 list of pin functions (1) port pins (1/2) pin name i/o function after reset alternate function p00 to p07 i/o port 0. 8-bit i/o port. Input/output can be specified in 1-bit units. When used as an input port, an on-chip pull-up resistor can b...

Page 38

Chapter 2 pin functions user’s manual u15331ej4v1ud 38 (1) port pins (2/2) pin name i/o function after reset alternate function p70 to p73 note 1 input port 7. 4-bit input port. (only when input port is selected by mask option or port function register) input − p80 to p87 note 2 i/o port 8. 8-bit i/...

Page 39

Chapter 2 pin functions user’s manual u15331ej4v1ud 39 (2) non-port pins (2/2) pin name i/o function after reset alternate function s0 to s15 lcd controller/driver segment signal outputs low-level output – s16 to s19 note 1 only when segment output is selected by mask option – s20 to s27 note 2 outp...

Page 40

Chapter 2 pin functions user’s manual u15331ej4v1ud 40 2.2 description of pin functions 2.2.1 p00 to p07 (port 0) these pins constitute an 8-bit i/o port. In addition, these pins enable key return signal detection. Port 0 can be specified in the following operation modes in 1-bit units. (1) port mod...

Page 41

Chapter 2 pin functions user’s manual u15331ej4v1ud 41 2.2.4 p30 to p34 (port 3) these pins constitute a 5-bit i/o port. In addition, they also function as timer i/o, external interrupt input, and remote control receive data input note . Port 3 can be specified in the following operation modes in 1-...

Page 42

Chapter 2 pin functions user’s manual u15331ej4v1ud 42 2.2.6 p60 to p67 (port 6) this is an 8-bit input-only port. In addition to a general-purpose input port function, it has a/d converter input and key return signal detection note functions. (1) port mode in this mode, p60 to p67 function as an 8-...

Page 43

Chapter 2 pin functions user’s manual u15331ej4v1ud 43 2.2.13 reset this pin inputs an active-low system reset signal. 2.2.14 x1, x2 these pins are used to connect a crystal resonator for main system clock oscillation. To supply an external clock, input the clock to x1 and input the inverted signal ...

Page 44

Chapter 2 pin functions user’s manual u15331ej4v1ud 44 2.2.21 ic0 (mask rom version only) the ic0 (internally connected) pin is used to set the µ pd789489 subseries in the test mode before shipment. In the normal operation mode, directly connect this pin to the v ss pin with as short a wiring length...

Page 45

Chapter 2 pin functions user’s manual u15331ej4v1ud 45 2.3 pin i/o circuits and recommended connection of unused pins the i/o circuit type of each pin and recommended connection of unused pins are shown in table 2-1. For the i/o circuit configuration of each type, see figure 2-1. Table 2-1. Types of...

Page 46

Chapter 2 pin functions user’s manual u15331ej4v1ud 46 table 2-1. Types of pin i/o circuits (2/2) pin name i/o circuit type i/o recommended connection of unused pins xt1 input connect to v ss . Xt2 – – leave open. Reset 2 input – ic0 connect directly to v ss . V pp – – independently connect a 10 k Ω...

Page 47

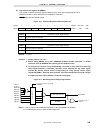

Chapter 2 pin functions user’s manual u15331ej4v1ud 47 figure 2-1. I/o circuit types (2/2) type 13-w type 13-v data output disable input enable in/out n-ch v ss mask option v dd middle-voltage input buffer data output disable input enable in/out n-ch v ss middle-voltage input buffer type 17 type 18 ...

Page 48

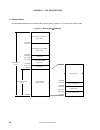

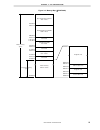

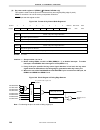

48 user’s manual u15331ej4v1ud chapter 3 cpu architecture 3.1 memory space the µ pd789489 subseries can access 64 kb of memory space. Figures 3-1 to 3-4 show the memory maps. Figure 3-1. Memory map ( µ pd789488) 8 0 0 0 h 7 f f f h special function registers 256 × 8 bits internal high-speed ram 1024...

Page 49

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 49 figure 3-2. Memory map ( µ pd78f9488) 8 0 0 0 h 7 f f f h special function registers 256 × 8 bits internal high-speed ram 1024 × 8 bits lcd display ram 28 × 4 bits f f f f h f f 0 0 h f e f f h f b 0 0 h f a f f h 0 0 0 0 h program memory spa...

Page 50

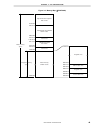

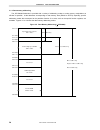

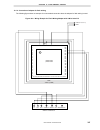

Chapter 3 cpu architecture 50 user’s manual u15331ej4v1ud figure 3-3. Memory map ( µ pd789489) b f f f h 0 0 0 0 h 0 0 8 0 h 0 0 7 f h 0 0 4 0 h 0 0 3 f h 0 0 3 0 h 0 0 2 f h program area program area callt table area vector table area special function registers 256 × 8 bits internal high-speed ram ...

Page 51

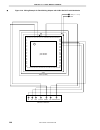

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 51 figure 3-4. Memory map ( µ pd78f9489) b f f f h 0 0 0 0 h 0 0 8 0 h 0 0 7 f h 0 0 4 0 h 0 0 3 f h 0 0 3 0 h 0 0 2 f h f f f f h f f 0 0 h f e f f h f b 0 0 h f a f f h 0 0 0 0 h f a 1 c h f a 1 b h f a 0 0 h f 9 f f h f 7 0 0 h f 6 f f h c 0 ...

Page 52

Chapter 3 cpu architecture 52 user’s manual u15331ej4v1ud 3.1.1 internal program memory space the internal program memory space stores programs and table data. This space is usually addressed by the program counter (pc). The µ pd789489 subseries provide internal rom (or flash memory) with the follow...

Page 53

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 53 3.1.2 internal data memory space (1) internal high-speed ram and internal low-speed ram the µ pd789489 subseries products incorporate the internal high-speed ram and internal low-speed ram of the following capacity for each product. The inter...

Page 54

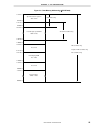

Chapter 3 cpu architecture 54 user’s manual u15331ej4v1ud 3.1.4 data memory addressing the µ pd789489 subseries is provided with a variety of addressing modes to make memory manipulation as efficient as possible. At the addresses corresponding to data memory area (fb00h to ffffh) especially, specifi...

Page 55

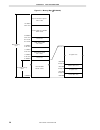

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 55 figure 3-6. Data memory addressing ( µ pd78f9488) special function registers 256 × 8 bits internal high-speed ram 1024 × 8 bits lcd display ram 28 × 4 bits f f f f h 8 0 0 0 h 7 f f f h 0 0 0 0 h direct addressing register indirect addressing...

Page 56

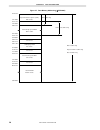

Chapter 3 cpu architecture 56 user’s manual u15331ej4v1ud figure 3-7. Data memory addressing ( µ pd789489) direct addressing register indirect addressing based addressing sfr addressing short direct addressing f f f f h 0 0 0 0 h f f 0 0 h f e f f h f f 2 0 h f f 1 f h f e 2 0 h f e 1 f h f b 0 0 h ...

Page 57

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 57 figure 3-8. Data memory addressing ( µ pd78f9489) direct addressing register indirect addressing based addressing sfr addressing short direct addressing f f f f h c 0 0 0 h b f f f h 0 0 0 0 h f f 0 0 h f e f f h f f 2 0 h f f 1 f h f e 2 0 h...

Page 58

Chapter 3 cpu architecture 58 user’s manual u15331ej4v1ud 3.2 processor registers the µ pd789489 subseries is provided with the following on-chip processor registers. 3.2.1 control registers the control registers contain special functions to control the program sequence status and stack memory. The ...

Page 59

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 59 (a) interrupt enable flag (ie) this flag controls interrupt request acknowledgement operations of the cpu. When 0, ie is set to the interrupt disabled status (di), and interrupt requests other than non-maskable interrupts are all disabled. Wh...

Page 60

Chapter 3 cpu architecture 60 user’s manual u15331ej4v1ud (3) stack pointer (sp) this is a 16-bit register that holds the start address of the memory stack area. Only the internal high-speed ram area can be set as the stack area. Figure 3-11. Stack pointer configuration 0 15 sp14 sp15 sp sp13 sp12 s...

Page 61

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 61 3.2.2 general-purpose registers the general-purpose registers consist of eight 8-bit registers (x, a, c, b, e, d, l, and h). Each register can be used as an 8-bit register, or two 8-bit registers in pairs can be used as a 16-bit register (ax,...

Page 62

Chapter 3 cpu architecture 62 user’s manual u15331ej4v1ud 3.2.3 special function registers (sfrs) unlike a general-purpose register, each special function register has a special function. The special function registers are allocated in the 256-byte area of ff00h to ffffh. Special function registers ...

Page 63

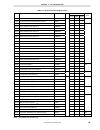

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 63 table 3-4. Special function registers (1/3) bit unit for manipulation address special function register (sfr) name symbol r/w 1 bit 8 bits 16 bits after reset ff00h port 0 p0 √ √ − ff01h port 1 p1 √ √ − ff02h port 2 p2 √ √ − ff03h port 3 p3 √...

Page 64

Chapter 3 cpu architecture 64 user’s manual u15331ej4v1ud table 3-4. Special function registers (2/3) bit unit for manipulation address special function register (sfr) name symbol r/w 1 bit 8 bits 16 bits after reset ff40h 8-bit h width compare register 61 crh61 w − √ − undefined ff41h 8-bit timer m...

Page 65

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 65 table 3-4. Special function registers (3/3) bit unit for manipulation address special function register (sfr) name symbol r/w 1 bit 8 bits 16 bits after reset ff80h a/d converter mode register 0 adml0 √ √ − ff84h analog input channel specific...

Page 66

Chapter 3 cpu architecture 66 user’s manual u15331ej4v1ud 3.3 instruction address addressing an instruction address is determined by the program counter (pc) contents. The pc contents are normally incremented (+1 for each byte) automatically according to the number of bytes of an instruction to be f...

Page 67

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 67 3.3.2 immediate addressing [function] immediate data in the instruction word is transferred to the program counter (pc) and branched. This function is carried out when the call !Addr16 or br !Addr16 instruction is executed. Call !Addr16 and b...

Page 68

Chapter 3 cpu architecture 68 user’s manual u15331ej4v1ud 3.3.3 table indirect addressing [function] table contents (branch destination address) of the particular location to be addressed by the lower 5-bit immediate data of an instruction code from bit 1 to bit 5 are transferred to the program coun...

Page 69

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 69 3.4 operand address addressing the following various methods are available to specify the register and memory (addressing) which undergo manipulation during instruction execution. 3.4.1 direct addressing [function] the memory indicated with i...

Page 70

Chapter 3 cpu architecture 70 user’s manual u15331ej4v1ud 3.4.2 short direct addressing [function] the memory to be manipulated in the fixed space is directly addressed with 8-bit data in an instruction word. The fixed space is the 256-byte space fe20h to ff1fh where the addressing is applied. Inter...

Page 71

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 71 3.4.3 special function register (sfr) addressing [function] the memory-mapped special function registers (sfrs) are addressed with 8-bit immediate data in an instruction word. This addressing is applied to the 256-byte space ff00h to ffffh. H...

Page 72

Chapter 3 cpu architecture 72 user’s manual u15331ej4v1ud 3.4.4 register addressing [function] in the register addressing mode, general-purpose registers are accessed as operands. The general-purpose register to be accessed is specified by a register specification code or functional name in the inst...

Page 73

Chapter 3 cpu architecture user’s manual u15331ej4v1ud 73 3.4.5 register indirect addressing [function] in the register indirect addressing mode, memory is manipulated according to the contents of a register pair specified as an operand. The register pair to be accessed is specified by the register ...

Page 74

Chapter 3 cpu architecture 74 user’s manual u15331ej4v1ud 3.4.6 based addressing [function] 8-bit immediate data is added to the contents of the base register, that is, the hl register pair, and the sum is used to address the memory. Addition is performed by expanding the offset data as a positive n...

Page 75

User’s manual u15331ej4v1ud 75 chapter 4 port functions 4.1 port functions the µ pd789489 subseries provides the ports shown in figure 4-1, enabling various methods of control. The functions of each port are shown in table 4-1. Numerous other functions are provided that can be used in addition to th...

Page 76

Chapter 4 port functions 76 user’s manual u15331ej4v1ud table 4-1. Port functions port name pin name function port 0 p00 to p07 i/o port. Input/output can be specified in 1-bit units. When used as an input port, an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option r...

Page 77

Chapter 4 port functions user’s manual u15331ej4v1ud 77 4.2.1 port 0 this is an 8-bit i/o port with an output latch. Port 0 can be specified in the input or output mode in 1-bit units by using port mode register 0 (pm0). When the p00 to p07 pins are used as input port pins, on-chip pull-up resistors...

Page 78

Chapter 4 port functions 78 user’s manual u15331ej4v1ud 4.2.2 port 1 this is a 2-bit i/o port with an output latch. Port 1 can be specified in the input or output mode in 1-bit units by using port mode register 1 (pm1). When using the p10 and p11 pins as input port pins, on-chip pull-up resistors ca...

Page 79

Chapter 4 port functions user’s manual u15331ej4v1ud 79 4.2.3 port 2 this is a 6-bit i/o port with an output latch. Port 2 can be specified in the input or output mode in 1-bit units by using port mode register 2 (pm2). When using the p20 to p25 pins as input port pins, on-chip pull-up resistors can...

Page 80

Chapter 4 port functions 80 user’s manual u15331ej4v1ud figure 4-5. Block diagram of p21 internal bus v dd p21/so20/txd20 wr pub2 rd wr port wr pm pub21 alternate function output latch (p21) pm21 selector p-ch pub2: pull-up resistor option register b2 pm: port mode register rd: port 2 read signal wr...

Page 81

Chapter 4 port functions user’s manual u15331ej4v1ud 81 figure 4-6. Block diagram of p22 and p25 p22/si20/ rxd20, p25/si10 wr pub2 rd wr port wr pm pub22, pub25 alternate function output latch (p22, p25) pm22, pm25 v dd p-ch internal bus selector pub2: pull-up resistor option register b2 pm: port mo...

Page 82

Chapter 4 port functions 82 user’s manual u15331ej4v1ud figure 4-7. Block diagram of p23 internal bus v dd p-ch p23/sck10 wr pub2 rd wr port wr pm pub23 alternate function output latch (p23) pm23 alternate function selector pub2: pull-up resistor option register b2 pm: port mode register rd: port 2 ...

Page 83

Chapter 4 port functions user’s manual u15331ej4v1ud 83 figure 4-8. Block diagram of p24 internal bus v dd p24/so10 wr pub2 rd wr port wr pm pub24 alternate function output latch (p24) pm24 selector p-ch pub2: pull-up resistor option register b2 pm: port mode register rd: port 2 read signal wr: port...

Page 84

Chapter 4 port functions 84 user’s manual u15331ej4v1ud 4.2.4 port 3 this is a 5-bit i/o port with an output latch. Port 3 can be specified in the input or output mode in 1-bit units by using port mode register 3 (pm3). When using the p30 to p34 pins as input port pins, on-chip pull-up resistors can...

Page 85

Chapter 4 port functions user’s manual u15331ej4v1ud 85 figure 4-10. Block diagram of p34 (a) when µ pd789488, 78f9488 is used p34 wr pub3 rd wr port wr pm pub34 pm34 v dd p-ch internal bus selector output latch (p34) (b) when µ pd789489, 78f9489 is used p34/rin wr pub3 rd wr port wr pm pub34 pm34 v...

Page 86

Chapter 4 port functions 86 user’s manual u15331ej4v1ud 4.2.5 port 5 this is a 4-bit n-ch open-drain i/o port with an output latch. Port 5 can be specified in the input or output mode in 1-bit units by using port mode register 5 (pm5). For a mask rom version, use of an on-chip pull-up resistor can b...

Page 87

Chapter 4 port functions user’s manual u15331ej4v1ud 87 4.2.6 port 6 this is an 8-bit input-only port. This port is also used for the analog input of an a/d converter and key return signal input note . Figure 4-12 shows a block diagram of port 6. Note µ pd789489 and 78f9489 only. Figure 4-12. Block ...

Page 88

Chapter 4 port functions 88 user’s manual u15331ej4v1ud figure 4-12. Block diagram of p60 to p67 (2/2) (b) when µ pd789489, 78f9489 is used v ref rd alternate function p60/ani0/kr10 to p67/ani7/kr17 + − krm010, krm014 to krm017 wr krm01 a/d converter internal bus krm01: key return mode register 01 r...

Page 89

Chapter 4 port functions user’s manual u15331ej4v1ud 89 4.2.7 port 7 this is a 4-bit input-only port. Only the bits for which the port function is selected can be used, by using a mask option in the µ pd789488 and 789489 or port function register 7 (pf7) in the µ pd78f9488 and 78f9489. Figure 4-13 s...

Page 90

Chapter 4 port functions 90 user’s manual u15331ej4v1ud 4.2.8 port 8 this is an 8-bit i/o port with an output latch. Only the bits for which the port function is selected can be used, by using a mask option in the µ pd789488 and 789489 or port function register 8 (pf8) in the µ pd78f9488 and 78f9489...

Page 91

Chapter 4 port functions user’s manual u15331ej4v1ud 91 4.3 registers controlling port function the ports are controlled by the following three types of registers. • port mode registers (pm0 to pm3, pm5, pm8) • pull-up resistor option registers (pub0 to pub3) • port function registers (pf7, pf8) ( µ...

Page 92

Chapter 4 port functions 92 user’s manual u15331ej4v1ud table 4-3. Port mode registers and output latch settings when using alternate functions alternate function pin name name i/o pm ×× p ×× p00 to p07 kr0 to kr7 or kr00 to kr07 input 1 × intp0 input 1 × to50 output 0 0 p30 tmi60 input 1 × intp1 in...

Page 93

Chapter 4 port functions user’s manual u15331ej4v1ud 93 (2) pull-up resistor option registers (pub0 to pub3) these registers set whether to use on-chip pull-up resistors for pins p00 to p07, p10, p11, p20 to p25, and p30 to p34. An on-chip pull-up resistor can be used only for those bits set to the ...

Page 94

Chapter 4 port functions 94 user’s manual u15331ej4v1ud 4.4 port function operation the operation of a port differs depending on whether the port is set in the input or output mode, as described below. 4.4.1 writing to i/o port (1) in output mode a value can be written to the output latch of a port ...

Page 95

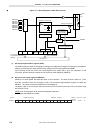

User’s manual u15331ej4v1ud 95 chapter 5 clock generator 5.1 clock generator functions the clock generator generates the clock to be supplied to the cpu and peripheral hardware. The following two types of system clock oscillators are used. • main system clock oscillator this circuit oscillates at 1....

Page 96

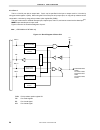

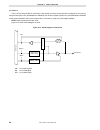

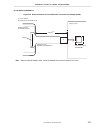

Chapter 5 clock generator 96 user’s manual u15331ej4v1ud figure 5-1. Clock generator block diagram ( µ pd789488, 789489) f xt 8f xt f xtt x1 x2 xt1 xt2 f x f x 2 2 f xtt 2 1/2 prescaler standby controller wait controller mask option stop mcc pcc1 cls internal bus css0 frc scc internal bus timer 50 w...

Page 97

Chapter 5 clock generator user’s manual u15331ej4v1ud 97 figure 5-2. Clock generator block diagram ( µ pd78f9488, 78f9489) subsystem clock oscillator f xt x1 x2 xt1 xt2 main system clock oscillator f x f x 2 2 f xtt 2 1/2 prescaler clock to peripheral hardware timer 50 watch timer lcd controller/dri...

Page 98

Chapter 5 clock generator 98 user’s manual u15331ej4v1ud 5.3 registers controlling clock generator the clock generator is controlled by the following four registers. • processor clock control register (pcc) • subclock oscillation mode register (sckm) • subclock control register (css) • subclock sele...

Page 99

Chapter 5 clock generator user’s manual u15331ej4v1ud 99 (2) subclock oscillation mode register (sckm) sckm selects a feedback resistor for the subsystem clock, and controls the oscillation of the clock. Sckm is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets sckm to 00h....

Page 100

Chapter 5 clock generator 100 user’s manual u15331ej4v1ud (4) subclock selection register (ssck) ( µ pd78f9488, 78f9489 only) this register is used to control the operation of the ×4 subsystem clock multiplication circuit. Ssck is set via a 1-bit or 8-bit memory manipulation instruction. Reset input...

Page 101

Chapter 5 clock generator user’s manual u15331ej4v1ud 101 5.4 system clock oscillators 5.4.1 main system clock oscillator the main system clock oscillator is oscillated by the crystal or ceramic resonator (5.0 mhz typ.) connected across the x1 and x2 pins. An external clock can also be input to the ...

Page 102

Chapter 5 clock generator 102 user’s manual u15331ej4v1ud 5.4.2 subsystem clock oscillator the subsystem clock oscillator is oscillated by the crystal resonator (32.768 khz typ.) connected across the xt1 and xt2 pins. An external clock can also be input to the circuit. In this case, input the clock ...

Page 103

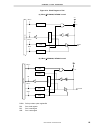

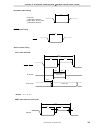

Chapter 5 clock generator user’s manual u15331ej4v1ud 103 5.4.3 example of incorrect resonator connection figure 5-9 shows examples of incorrect resonator connection. Figure 5-9. Examples of incorrect resonator connection (1/2) (a) too long wiring (b) crossed signal line v ss x1 x2 v ss x1 x2 portn ...

Page 104

Chapter 5 clock generator 104 user’s manual u15331ej4v1ud figure 5-9. Examples of incorrect resonator connection (2/2) (e) signal is fetched v ss x1 x2 remark when using the subsystem clock, read x1 and x2 as xt1 and xt2, respectively, and connect a resistor to xt2 in series. 5.4.4 divider circuit t...

Page 105

Chapter 5 clock generator user’s manual u15331ej4v1ud 105 5.5 clock generator operation the clock generator generates the following clocks and controls the operation modes of the cpu, such as the standby mode. • main system clock f x • subsystem clock f xt • cpu clock f cpu • clock to peripheral har...

Page 106

Chapter 5 clock generator 106 user’s manual u15331ej4v1ud 5.6 changing setting of system clock and cpu clock 5.6.1 time required for switching between system clock and cpu clock the cpu clock can be selected by using bit 1 (pcc1) of the processor clock control register (pcc) and bit 4 (css0) of the ...

Page 107

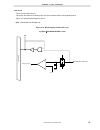

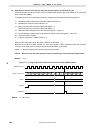

Chapter 5 clock generator user’s manual u15331ej4v1ud 107 5.6.2 switching between system clock and cpu clock the following figure illustrates how the cpu clock and system clock switch. Figure 5-10. Switching between system clock and cpu clock system clock cpu clock interrupt request signal reset v d...

Page 108

108 user’s manual u15331ej4v1ud chapter 6 16-bit timer 20 6.1 16-bit timer 20 functions 16-bit timer 20 has the following functions. • timer interrupt • timer output • count value capture (1) timer interrupt an interrupt is generated when a count value and compare value match. (2) timer output timer...

Page 109

Chapter 6 16-bit timer 20 user’s manual u15331ej4v1ud 109 figure 6-1. Block diagram of 16-bit timer 20 cpt20/to20 /intp3/p33 internal bus internal bus 16-bit timer mode control register 20 (tmc20) 16-bit timer mode control register 20 tof20 cpt201 cpt200 toc20 tcl201 tcl200 toe20 f x f x /2 2 edge d...

Page 110

Chapter 6 16-bit timer 20 110 user’s manual u15331ej4v1ud (4) 16-bit counter read buffer 20 this buffer is used to latch and hold the count value for tm20. 6.3 registers controlling 16-bit timer 20 16-bit timer 20 is controlled by the following three registers. • 16-bit timer mode control register 2...

Page 111

Chapter 6 16-bit timer 20 user’s manual u15331ej4v1ud 111 figure 6-2. Format of 16-bit timer mode control register 20 symbol 5 4 3 2 1 address after reset r/w tmc20 tod20 tof20 cpt201 cpt200 toc20 tcl201 tcl200 toe20 ff48h 00h r/w note 1 tod20 timer output data 0 timer output is “0” 1 timer output i...

Page 112

Chapter 6 16-bit timer 20 112 user’s manual u15331ej4v1ud (2) port mode register 3 (pm3) this register is used to set the i/o mode of port 3 in 1-bit units. When using the p33/intp3/cpt20/to20 pin as a capture input (cpt20), set pm33 to 1. When using the above pin as a timer output (to20), set the p...

Page 113

Chapter 6 16-bit timer 20 user’s manual u15331ej4v1ud 113 6.4 16-bit timer 20 operation 6.4.1 operation as timer interrupt 16-bit timer 20 can generate interrupts repeatedly each time the free-running counter value reaches the value set to cr20. Since this counter is not cleared and holds the count ...

Page 114

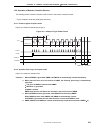

Chapter 6 16-bit timer 20 114 user’s manual u15331ej4v1ud figure 6-5. Timing of timer interrupt operation cr20 inttm20 to20 tof20 n n n n n t 0000h n ffffh n 0000h 0001h 0001h count clock tm20 count value interrupt acknowledgement interrupt acknowledgement overflow flag set remark n = 0000h to ffffh.

Page 115

Chapter 6 16-bit timer 20 user’s manual u15331ej4v1ud 115 6.4.2 operation as timer output 16-bit timer 20 can invert the timer output repeatedly each time the free-running counter value reaches the value set to cr20. Since this counter is not cleared and holds the count even after the timer output i...

Page 116

Chapter 6 16-bit timer 20 116 user’s manual u15331ej4v1ud 6.4.3 capture operation the capture operation consists of latching the count value of 16-bit timer counter 20 (tm20) into a capture register in synchronization with a capture trigger, and retaining the count value. Set tmc20 as shown in figur...

Page 117

Chapter 6 16-bit timer 20 user’s manual u15331ej4v1ud 117 6.4.4 16-bit timer counter 20 readout the count value of 16-bit timer counter 20 (tm20) is read out using a 16-bit manipulation instruction. Tm20 readout is performed via the counter read buffer. The counter read buffer latches the tm20 count...

Page 118

Chapter 6 16-bit timer 20 118 user’s manual u15331ej4v1ud 6.5 cautions on using 16-bit timer 20 6.5.1 restrictions when rewriting 16-bit compare register 20 (1) disable interrupts (tmmk20 = 1) and inversion control of timer output (toc20 = 0) before rewriting the compare register (cr20). If the valu...

Page 119

Chapter 6 16-bit timer 20 user’s manual u15331ej4v1ud 119 when rewriting using 16-bit access disable interrupts (tmmk20 = 1) and inversion control of timer output (toc20 = 0). Rewrite cr20 (16 bits). Wait for one cycle or more of the count clock. Clear the interrupt request flag (tmif20). Enable tim...

Page 120

120 user’s manual u15331ej4v1ud chapter 7 8-bit timers 50, 60, and 61 7.1 functions of 8-bit timers 50, 60, and 61 one 8-bit timer channel (timer 50) and two 8-bit timer/event counter channels (timer 60 and 61) are incorporated in the µ pd789489 subseries. The operation modes listed in the following...

Page 121

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 121 (5) ppg output mode (ppg: programmable pulse generator) pulses are output using any cycle or duty ratio (pulse width) set (both the cycle and pulse width are programmable). (6) 24-bit event counter mode operation as an external ev...

Page 122

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 122 7.2 configuration of 8-bit timers 50, 60, and 61 8-bit timers 50, 60, and 61 include the following hardware. Table 7-2. Configuration of 8-bit timers 50, 60, and 61 item configuration timer counter 8 bits × 3 (tm50, tm60, tm61) re...

Page 123

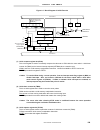

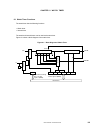

Cha pter 7 8-bit timers 50, 60, a nd 61 user’s manual u15331ej4v1ud 123 figure 7-2. Block diagram of timer 50 teg50 tcl500 tcl501 8-bit timer mode control register 50 (tmc50) decoder selector selector 8-bit compare register 50 (cr50) 8-bit timer counter 50 (tm50) selector count operation start signa...

Page 124

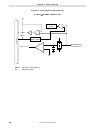

Cha pter 7 8-bit timers 50, 60, a nd 61 user’s manual u15331ej4v1ud 124 tce60 tcl602 tcl601 tcl600 tmd601 tmd600 toe600 8-bit timer mode control register 60 (tmc60) carrier generator output control register 60 (tca60) decoder 8-bit timer counter 60 (tm60) f/f tm50 match signal (in cascade connection...

Page 125

Cha pter 7 8-bit timers 50, 60, a nd 61 user’s manual u15331ej4v1ud 125 tce61 tcl612 tcl611 tcl610 tmd611 tmd610 toe610 8-bit timer mode control register 61 (tmc61) decoder 8-bit timer counter 61 (tm61) f/f clear 8-bit compare register 61 (cr61) selector inttm61 match to61/tmi61 /intp2/p32 reset ppg...

Page 126

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 126 figure 7-5. Block diagram of output controller (timer 60) f/f rmc60 nrz60 toe60 pm31 p31 output latch selector to60/intp1/p31 carrier generator mode carrier clock (1) 8-bit compare register 50 (cr50) this 8-bit register is used to...

Page 127

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 127 (4) 8-bit h width compare registers 60 and 61 (crh60, crh61) in carrier generator mode and ppg output mode, the high-level width of timer output is set by writing a value to crh6n. This 8-bit register is used to continually compar...

Page 128

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 128 7.3 control registers for 8-bit timers 50, 60, and 61 8-bit timers 50, 60, and 61 are controlled by the following six registers. • 8-bit timer mode control register 50 (tmc50) • 8-bit timer mode control register 60 (tmc60) • carri...

Page 129

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 129 figure 7-6. Format of 8-bit timer mode control register 50 (2/2) symbol 5 4 3 2 1 address after reset r/w tmc50 tce50 teg50 tcl502 tcl501 tcl500 tmd501 tmd500 toe50 ff4dh 00h r/w toe50 control of timer output note 4 0 output disab...

Page 130

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 130 figure 7-7. Format of 8-bit timer mode control register 60 symbol 6 5 4 3 2 1 address after reset r/w tmc60 tce60 0 tcl602 tcl601 tcl600 tmd601 tmd600 toe600 ff4eh 00h r/w tce60 control of tm60 count operation note 1 0 clear tm60 ...

Page 131

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 131 (3) carrier generator output control register 60 (tca60) this register is used to set the timer output data in carrier generator mode. Tca60 is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets this regis...

Page 132

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 132 (4) 8-bit timer mode control register 61 (tmc61) 8-bit timer mode control register 61 (tmc61) is used to control the timer 61 count clock setting and the operation mode setting. Tmc61 is set with a 1-bit or 8-bit memory manipulati...

Page 133

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 133 (5) port mode register 3 (pm3) this register is used to set the i/o mode of port 3 in 1-bit units. When using the p30/intp0/to50/tmi60 pin as a timer output (to50), set pm30 and the p30 output latch to 0. When used as a timer inpu...

Page 134

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 134 7.4 operation of 8-bit timers 50, 60, and 61 7.4.1 operation as 8-bit timer counter timer 50, timer 60, and timer 61 can be independently used as 8-bit timer counters. The following modes can be used for the 8-bit timer counter. •...

Page 135

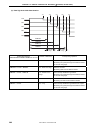

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 135 table 7-3. Interval time of timer 50 tcl502 tcl501 tcl500 minimum interval time maximum interval time resolution 0 0 0 1/f x (0.2 µ s) 2 8 /f x (51.2 µ s) 1/f x (0.2 µ s) 0 0 1 2 3 /f x (1.6 µ s) 2 11 /f x (409.6 µ s) 2 3 /f x (1....

Page 136

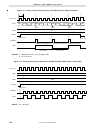

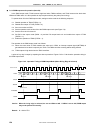

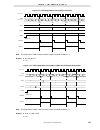

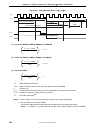

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 136 figure 7-11. Timing of interval timer operation with 8-bit resolution (basic operation) count stop count clock crnm tcenm inttmnm tonm n t tmnm n 00h 01h n 00h 01h n 00h 00h 01h 00h 01h clear clear clear count start interrupt ackn...

Page 137

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 137 figure 7-13. Timing of interval timer operation with 8-bit resolution (when crnm is set to ffh) count clock crnm tcenm inttmnm tonm ffh tmnm ffh 00h 01h 00h 01h 00h ffh 00h 01h ffh ffh 00h clear clear clear count start remark nm =...

Page 138

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 138 figure 7-15. Timing of interval timer operation with 8-bit resolution (when crnm changes from n to m (n > m)) count clock crnm tcenm inttmnm tonm tmnm 00h 00h 00h n − 1 n m n m n m 00h ffh m h clear clear clear tmnm overflows beca...

Page 139

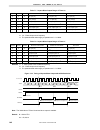

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 139 figure 7-16. Timing of interval timer operation with 8-bit resolution (when timer 60 match signal is selected for timer 50 count clock) timer 60 count clock cr60 tce60 inttm60 to60 tm60 n 00h m 00h 00h 01h m n m 00h m 00h 00h 01h ...

Page 140

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 140 (2) operation as external event counter with 8-bit resolution (timer 60 and timer 61 only) the external event counter counts the number of external clock pulses input to the tmi6m pin by using 8-bit timer counter 6m (tm6m). To ope...

Page 141

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 141 (3) operation as square-wave output with 8-bit resolution square waves of any frequency can be output at an interval specified by the value preset in 8-bit compare register nm (crnm). To operate timer nm for square-wave output, se...

Page 142

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 142 table 7-7. Square-wave output range of timer 60 tcl602 tcl601 tcl600 minimum pulse width maximum pulse width resolution 0 0 0 1/f x (0.2 µ s) 2 8 /f x (51.2 µ s) 1/f x (0.2 µ s) 0 0 1 2 2 /f x (0.8 µ s) 2 10 /f x (204 µ s) 2 2 /f ...

Page 143

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 143 7.4.2 operation as 16-bit timer counter timer 50 and timer 60 can be used as a 16-bit timer counter using cascade connection. In this case, 8-bit timer counter 50 (tm50) is the higher 8 bits and 8-bit timer counter 60 (tm60) is th...

Page 144

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 144 table 7-9. Interval time with 16-bit resolution tcl602 tcl601 tcl600 minimum interval time maximum interval time resolution 0 0 0 1/f x (0.2 µ s) 2 16 /f x (13.1 ms) 1/f x (0.2 µ s) 0 0 1 2 2 /f x (0.8 µ s) 2 18 /f x (52.4 ms) 2 2...

Page 145

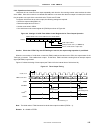

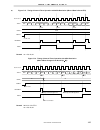

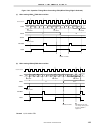

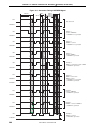

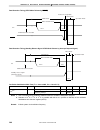

Cha pter 7 8-bit timers 50, 60, a nd 61 user’s manual u15331ej4v1ud 145 interval time count clock tm60 count value cr60 tce60 inttm60 to60 ffh 00h 7fh 00h n 00h n n n n 80h 7fh 80h ffh 00h n 00h n n n tm50 count pulse tm50 00h x x − 1 01h cr50 x x x 7fh 80h ffh 00h n 00h n n n x x − 1 00h t not clea...

Page 146

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 146 (2) operation as external event counter with 16-bit resolution the external event counter counts the number of external clock pulses input to the tmi60 pin by tm50 and tm60. To operate as an external event counter with 16-bit reso...

Page 147

Cha pter 7 8-bit timers 50, 60, a nd 61 user’s manual u15331ej4v1ud 147 tmi60 pin input tm60 count value cr60 tce60 inttm60 ffh 00h 7fh 00h n 00h n n n n 80h 7fh 80h ffh 00h n 00h n n n tm50 count pulse tm50 00h x 01h cr50 x x x 7fh 80h ffh 00h n 00h n n n x x − 1 00h x − 1 not cleared because tm50 ...

Page 148

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 148 (3) operation as square-wave output with 16-bit resolution square waves of any frequency can be output at an interval specified by the count value preset in cr50 and cr60. To operate as a square-wave output with 16-bit resolution,...

Page 149

Cha pter 7 8-bit timers 50, 60, a nd 61 user’s manual u15331ej4v1ud 149 count clock tm60 count value cr60 tce60 inttm60 to60 note ffh 00h 7fh 00h n 00h n n n n 80h 7fh 80h ffh 00h n 00h n n n tm50 count pulse tm50 00h x x − 1 01h cr50 x x x 7fh 80h ffh 00h n 00h n n n x x − 1 00h not cleared because...

Page 150

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 150 7.4.3 operation as carrier generator an arbitrary carrier clock generated by tm60 can be output in the cycle set in tm50. To operate timer 50 and timer 60 as carrier generators, settings must be made in the following sequence. Dis...

Page 151

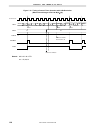

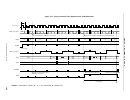

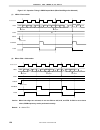

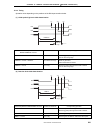

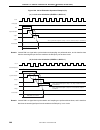

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 151 figure 7-22. Timing of carrier generator operation (when cr60 = n, crh60 = m (m > n)) tm60 count clock tm60 count value cr60 tce60 inttm60 m 00h n 00h 01h n crh60 m n 00h carrier clock n 00h 00h n m 00h 01h l l 00h 01h l 00h 01h l...

Page 152

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 152 figure 7-23. Timing of carrier generator operation (when cr60 = n, crh60 = m (m n)) tm60 count clock tm60 count value cr60 tce60 inttm60 n 00h n l crh60 m carrier clock n 00h 00h 01h l 00h 01h l 00h 01h l 00h l 00h 01h tm50 count ...

Page 153

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 153 figure 7-24. Timing of carrier generator operation (when cr60 = crh60 = n) tm60 count clock tm60 count value cr60 tce60 inttm60 n 00h 00h 00h n crh60 n n carrier clock 00h 00h n n 00h 01h l 00h 01h l 00h 01h l 00h l 00h 01h tm50 c...

Page 154

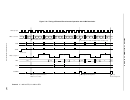

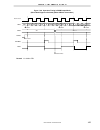

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 154 7.4.4 pwm output mode operation (timer 50) in the pwm output mode, to50 becomes high level when tm50 overflows, and to50 becomes low level when cr50 and tm50 match. It is thus possible to output a pulse with any duty ratio (free-r...

Page 155

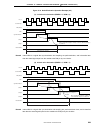

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 155 figure 7-26. Operation timing when overwriting cr50 (when rising edge is selected) (1) when setting cr50 > tm50 after overflow count clock cr50 tce50 inttm50 to50 n tm50 n 00h 00h 00h 01h ffh m ffh 01h m overflow overflow overflow...

Page 156

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 156 figure 7-27. Operation timing in pwm output mode (when both edges are selected) (1) cr50 = even number count clock cr50 tce50 inttm50 to50 2n tm50 2n 00h 00h 01h ffh ffh 2n 02h feh 01h 02h feh overflow overflow count start (2) whe...

Page 157

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 157 figure 7-28. Operation timing in pwm output mode (when both edges are selected) (when cr50 is overwritten) count clock cr50 tce50 inttm50 to50 2n + 1 tm50 2n 00h 00h 00h 01h ffh ffh 01h 2n + 1 01h 02h feh 2n overflow overflow over...

Page 158

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 158 7.4.5 ppg output mode operation (timer 60 and timer 61) in the ppg output mode, a pulse of any duty ratio can be output by setting a low-level width using cr6m and a high-level width using crh6m. To operate timer 6m in ppg output ...

Page 159

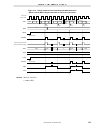

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 159 figure 7-29. Ppg output mode timing (basic operation) count clock tm6m count value cr6m tce6m inttm6m 00h n 00h 01h n crh6m m n to6m note 00h 00h 01h m 01h 01h m 00h clear clear clear clear count start note the initial value of to...

Page 160

Chapter 7 8-bit timers 50, 60, and 61 user’s manual u15331ej4v1ud 160 7.5 cautions on using 8-bit timers 50, 60, and 61 (1) error on starting timer an error of up to 1.5 clocks is included in the time between the timer being started and a match signal being generated. This is because the rising edge...

Page 161

User’s manual u15331ej4v1ud 161 chapter 8 watch timer 8.1 watch timer functions the watch timer has the following functions. • watch timer • interval timer the watch and interval timers can be used at the same time. Figure 8-1 shows a block diagram of the watch timer. Figure 8-1. Block diagram of wa...

Page 162

Chapter 8 watch timer 162 user’s manual u15331ej4v1ud (1) watch timer an interrupt request (intwt) occurs at an interval of 0.5 second when using either the 4.19 mhz main system clock or the 32.768 khz subsystem clock. Also, an interrupt request (intwt) occurs at an interval of 1.0 seconds when usin...

Page 163

Chapter 8 watch timer user’s manual u15331ej4v1ud 163 8.3 control registers for watch timer the watch timer is controlled by the following registers. • watch timer mode control register (wtm) • watch timer interrupt time selection register (wtim) (1) watch timer mode control register (wtm) this regi...

Page 164

Chapter 8 watch timer 164 user’s manual u15331ej4v1ud (2) watch timer interrupt time selection register (wtim) this register is used to set the interrupt time by selecting either the source clock or the clock divided by 2 for the subsystem clock to be input to watch timer. Wtim is set with a 1-bit o...

Page 165

Chapter 8 watch timer user’s manual u15331ej4v1ud 165 8.4 watch timer operation 8.4.1 operation as watch timer the main system clock (4.19 mhz) or subsystem clock (32.768 khz) is used to enable the watch timer to operate at 0.5-second intervals. Also, an interrupt request (intwt) occurs at an interv...

Page 166

Chapter 8 watch timer 166 user’s manual u15331ej4v1ud figure 8-4. Watch timer/interval timer operation timing 0h start overflow overflow 5-bit counter count clock f w /2 9 watch timer interrupt intwt interval timer interrupt intwti watch timer interrupt time (0.5 s) watch timer interrupt time (0.5 s...

Page 167

User’s manual u15331ej4v1ud 167 chapter 9 watchdog timer 9.1 watchdog timer functions the watchdog timer has the following functions. • watchdog timer • interval timer caution select the watchdog timer mode or interval timer mode by using the watchdog timer mode register (wdtm). (1) watchdog timer t...

Page 168

Chapter 9 watchdog timer 168 user’s manual u15331ej4v1ud 9.2 watchdog timer configuration the watchdog timer includes the following hardware. Table 9-3. Configuration of watchdog timer item configuration control registers watchdog timer clock selection register (wdcs) watchdog timer mode register (w...

Page 169

Chapter 9 watchdog timer user’s manual u15331ej4v1ud 169 9.3 watchdog timer control registers the watchdog timer is controlled by the following two registers. • watchdog timer clock selection register (wdcs) • watchdog timer mode register (wdtm) (1) watchdog timer clock selection register (wdcs) thi...

Page 170

Chapter 9 watchdog timer 170 user’s manual u15331ej4v1ud (2) watchdog timer mode register (wdtm) this register sets the operation mode of the watchdog timer, and enables/disables counting of the watchdog timer. Wdtm is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets wdtm ...

Page 171

Chapter 9 watchdog timer user’s manual u15331ej4v1ud 171 9.4 watchdog timer operation 9.4.1 operation as watchdog timer the watchdog timer detects a program loop when bit 4 (wdtm4) of the watchdog timer mode register (wdtm) is set to 1. The count clock (program loop detection time interval) of the w...

Page 172

Chapter 9 watchdog timer 172 user’s manual u15331ej4v1ud 9.4.2 operation as interval timer when bits 4 and 3 (wdtm4, wdtm3) of the watchdog timer mode register (wdtm) are set to 0 and 1, respectively, the watchdog timer operates as an interval timer that repeatedly generates an interrupt at interval...

Page 173

User’s manual u15331ej4v1ud 173 chapter 10 10-bit a/d converter 10.1 10-bit a/d converter functions the 10-bit a/d converter is a 10-bit resolution converter used to convert analog inputs into digital signals. This converter can control eight channels (ani0 to ani7) of analog inputs. A/d conversion ...

Page 174

Chapter 10 10-bit a/d converter 174 user’s manual u15331ej4v1ud figure 10-1. Block diagram of 10-bit a/d converter ani3/p63 sample & hold circuit voltage comparator successive approximation register (sar) controller a/d conversion result register 0 (adcrl0) av ss intad0 a/d converter mode register 0...

Page 175

Chapter 10 10-bit a/d converter user’s manual u15331ej4v1ud 175 (3) sample & hold circuit the sample & hold circuit samples consecutive analog inputs from the input circuit, one by one, and sends them to the voltage comparator. The sampled analog input voltage is held during a/d conversion. (4) volt...

Page 176

Chapter 10 10-bit a/d converter 176 user’s manual u15331ej4v1ud 10.3 10-bit a/d converter control registers the 10-bit a/d converter is controlled by the following two registers. • a/d converter mode register 0 (adml0) • analog input channel specification register 0 (ads0) (1) a/d converter mode reg...

Page 177

Chapter 10 10-bit a/d converter user’s manual u15331ej4v1ud 177 cautions 1. Start conversion (adcs0 = 1) after 14 µ s have elapsed following the setting of adce0. If adce0 is not used, the conversion result immediately after the setting of bit 7 (adcs0) is undefined. 2. The conversion result may be ...

Page 178

Chapter 10 10-bit a/d converter 178 user’s manual u15331ej4v1ud 10.4 10-bit a/d converter operation 10.4.1 basic operation of 10-bit a/d converter bit 0 of a/d converter mode register 0 (adml0) is set (adce0 = 1). Select a channel for a/d conversion, using analog input channel specification register...

Page 179

Chapter 10 10-bit a/d converter user’s manual u15331ej4v1ud 179 figure 10-4. Basic operation of 10-bit a/d converter conversion time sampling time sampling a/d conversion undefined conversion result conversion result a/d converter operation sar adcrl0 intad0 a/d conversion continues until bit 7 (adc...

Page 180

Chapter 10 10-bit a/d converter 180 user’s manual u15331ej4v1ud figure 10-5. Relationship between analog input voltage and a/d conversion result 1,023 1,022 1,021 3 2 1 0 a/d conversion result (adcrl0) 1 2,048 1 1,024 3 2,048 2 1,024 5 2,048 3 1,024 2,043 2,048 1,022 1,024 2,045 2,048 1,023 1,024 2,...

Page 181

Chapter 10 10-bit a/d converter user’s manual u15331ej4v1ud 181 10.4.3 operation mode of 10-bit a/d converter the a/d converter is initially in select mode. In this mode, analog input channel specification register 0 (ads0) is used to select an analog input channel from ani0 to ani7 for a/d conversi...

Page 182

Chapter 10 10-bit a/d converter 182 user’s manual u15331ej4v1ud 10.5 cautions related to 10-bit a/d converter (1) current consumption in standby mode in standby mode, the a/d converter stops operation. Clearing bit 7 (adcs0) and bit 0 (adce0) of a/d converter mode register 0 (adml0) to 0 can reduce ...

Page 183

Chapter 10 10-bit a/d converter user’s manual u15331ej4v1ud 183 (5) timing of undefined a/d conversion result the a/d conversion value may become undefined if the timing of the completion of a/d conversion and the timing to stop the a/d conversion operation conflict. Therefore, read the a/d conversi...

Page 184

Chapter 10 10-bit a/d converter 184 user’s manual u15331ej4v1ud (6) noise prevention to maintain a resolution of 10 bits, watch for noise at the av dd and ani0 to ani7 pins. The higher the output impedance of the analog input source, the larger the effect by noise. To reduce noise, attach an externa...

Page 185

Chapter 10 10-bit a/d converter user’s manual u15331ej4v1ud 185 (9) interrupt request flag (adif0) changing the contents of a/d converter mode register 0 (adml0) does not clear the interrupt request flag (adif0). If the analog input pins are changed during a/d conversion, therefore, the a/d conversi...

Page 186

186 user’s manual u15331ej4v1ud chapter 11 serial interface 20 11.1 serial interface 20 functions serial interface 20 has the following three modes. • operation stop mode • asynchronous serial interface (uart) mode • 3-wire serial i/o mode (1) operation stop mode this mode is used when serial transf...

Page 187

Cha pter 11 seria l interfa c e 20 user’s manual u15331ej4v1ud 187 internal bus receive buffer register 20 (rxb20) switch of the first bit asynchronous serial interface status register 20 (asis20) serial operation mode register 20 (csim20) receive shift register 20 (rxs20) csie20 dir20 csck20 pe20 f...

Page 188

Cha pter 11 seria l interfa c e 20 188 user’s manual u15331ej4v1ud clock for receive detection transmit shift clock receive shift clock receive detection txe20 rxe20 csie20 1/2 1/2 transmit clock counter (3 bits) receive clock counter (3 bits) 4 f x /2 f x /2 3 f x /2 4 f x /2 5 f x /2 6 f x /2 7 f ...

Page 189

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 189 (1) transmit shift register 20 (txs20) txs20 is a register in which transmit data is prepared. The transmit data is output from txs20 bit-serially. When the data length is seven bits, bits 0 to 6 of the data in txs20 will be transmit dat...

Page 190

Chapter 11 serial interface 20 190 user’s manual u15331ej4v1ud 11.3 serial interface 20 control registers serial interface 20 is controlled by the following six registers. • serial operation mode register 20 (csim20) • asynchronous serial interface mode register 20 (asim20) • asynchronous serial int...

Page 191

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 191 (2) asynchronous serial interface mode register 20 (asim20) asim20 is used to make the settings related to asynchronous serial interface mode. Asim20 is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets asim20 t...

Page 192

Chapter 11 serial interface 20 192 user’s manual u15331ej4v1ud table 11-2. Serial interface 20 operation mode settings (1) operation stop mode asim20 csim20 txe20 rxe20 csie20 dir20 csck20 pm22 p22 pm21 p21 pm20 p20 first bit shift clock p22/si20/ rxd20 pin function p21/so20/ txd20 pin function p20/...

Page 193

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 193 (3) asynchronous serial interface status register 20 (asis20) asis20 indicates the type of a reception error, if it occurs while asynchronous serial interface mode is set. Asis20 is set with a 1-bit or 8-bit memory manipulation instructi...

Page 194

Chapter 11 serial interface 20 194 user’s manual u15331ej4v1ud (4) baud rate generator control register 20 (brgc20) brgc20 is used to specify the serial clock for serial interface 20. Brgc20 is set with an 8-bit memory manipulation instruction. Reset input sets brgc20 to 00h. Figure 11-6. Format of ...

Page 195

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 195 the baud rate transmit/receive clock to be generated is either a divided system clock signal, or a signal obtained by dividing the clock input to the asck20 pin. (a) generation of uart baud rate transmit/receive clock form system clock t...

Page 196

Chapter 11 serial interface 20 196 user’s manual u15331ej4v1ud (b) generation of uart baud rate transmit/receive clock from external clock input to asck20 pin the transmit/receive clock is generated by dividing the clock input from the asck20 pin. The baud rate of a clock generated from the clock in...

Page 197

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 197 11.4 serial interface 20 operation serial interface 20 provides the following three modes. • operation stop mode • asynchronous serial interface (uart) mode • 3-wire serial i/o mode 11.4.1 operation stop mode in operation stop mode, seri...

Page 198

Chapter 11 serial interface 20 198 user’s manual u15331ej4v1ud (b) asynchronous serial interface mode register 20 (asim20) asim20 is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets asim20 to 00h. Txe20 0 1 transmit operation control transmit operation stopped transmit ope...

Page 199

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 199 11.4.2 asynchronous serial interface (uart) mode in this mode, the one-byte data following the start bit is transmitted/received, enabling full-duplex communication. This device incorporates a uart-dedicated baud rate generator that enab...

Page 200

Chapter 11 serial interface 20 200 user’s manual u15331ej4v1ud (b) asynchronous serial interface mode register 20 (asim20) asim20 is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets asim20 to 00h. Txe20 0 1 transmit operation control transmit operation stopped transmit ope...

Page 201

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 201 (c) asynchronous serial interface status register 20 (asis20) asis20 is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets asis20 to 00h. Pe20 0 1 parity error flag no parity error occurred a parity error occurre...

Page 202

Chapter 11 serial interface 20 202 user’s manual u15331ej4v1ud (d) baud rate generator control register 20 (brgc20) brgc20 is set with an 8-bit memory manipulation instruction. Reset input sets brgc20 to 00h. Tps203 0 0 0 0 0 0 0 0 1 tps202 0 0 0 0 1 1 1 1 0 f x /2 f x /2 2 f x /2 3 f x /2 4 f x /2 ...

Page 203

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 203 table 11-5. Example of relationship between system clock and baud rate error (%) baud rate (bps) n brgc20 set value f x = 5.0 mhz f x = 4.9152 mhz 1,200 8 70h 2,400 7 60h 4,800 6 50h 9,600 5 40h 19,200 4 30h 38,400 3 20h 76,800 2 10h 1.7...

Page 204

Chapter 11 serial interface 20 204 user’s manual u15331ej4v1ud (2) communication operation (a) data format the transmit/receive data format is as shown in figure 11-7. One data frame consists of a start bit, character bits, parity bit, and stop bit(s). The specification of character bit length in on...

Page 205

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 205 (b) parity types and operation the parity bit is used to detect a bit error in the communication data. Normally, the same kind of parity bit is used on the transmitting side and the receiving side. With even parity and odd parity, a one-...

Page 206

Chapter 11 serial interface 20 206 user’s manual u15331ej4v1ud (c) transmission a transmit operation is started by writing transmit data to transmit shift register 20 (txs20). The start bit, parity bit, and stop bit(s) are added automatically. When the transmit operation starts, the data in txs20 is...

Page 207

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 207 (d) reception when bit 6 (rxe20) of asynchronous serial interface mode register 20 (asim20) is set (1), a receive operation is enabled and sampling of the rxd20 pin input is performed. Rxd20 pin input sampling is performed using the seri...

Page 208

Chapter 11 serial interface 20 208 user’s manual u15331ej4v1ud (e) receive errors the following three errors may occur during a receive operation: a parity error, framing error, and overrun error. After data reception, an error flag is set in asynchronous serial interface status register 20 (asis20)...

Page 209

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 209 (f) reading receive data when the reception completion interrupt (intsr20) occurs, receive data can be read by reading the value of receive buffer register 20 (rxb20). To read the receive data stored in receive buffer register 20 (rxb20)...

Page 210

Chapter 11 serial interface 20 210 user’s manual u15331ej4v1ud (3) cautions related to uart mode (a) when bit 7 (txe20) of asynchronous serial interface mode register 20 (asim20) is cleared during transmission, be sure to set transmit shift register 20 (txs20) to ffh, then set txe20 to 1 before exec...

Page 211

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 211 11.4.3 3-wire serial i/o mode the 3-wire serial i/o mode is useful for connection of peripheral i/os and display controllers, etc., which incorporate a conventional clocked serial interface, such as the 75xl series, 78k series, and 17k s...

Page 212

Chapter 11 serial interface 20 212 user’s manual u15331ej4v1ud (b) asynchronous serial interface mode register 20 (asim20) asim20 is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets asim20 to 00h. When 3-wire serial i/o mode is selected, asim20 must be set to 00h. Txe20 0 ...

Page 213

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 213 (c) baud rate generator control register 20 (brgc20) brgc20 is set with an 8-bit memory manipulation instruction. Reset input sets brgc20 to 00h. Tps203 0 0 0 0 0 0 0 0 tps202 0 0 0 0 1 1 1 1 f x /2 f x /2 2 f x /2 3 f x /2 4 f x /2 5 f ...

Page 214

Chapter 11 serial interface 20 214 user’s manual u15331ej4v1ud (2) communication operation in 3-wire serial i/o mode, data transmission/reception is performed in 8-bit units. Data is transmitted/ received bit by bit in synchronization with the serial clock. Transmit shift register 20 (txs20/sio20) a...

Page 215

Chapter 11 serial interface 20 user’s manual u15331ej4v1ud 215 figure 11-11. 3-wire serial i/o mode timing (2/2) (ii) slave operation timing (csck20=1) 1 2 3 4 5 6 7 8 di7 di6 di5 di4 di3 di2 di1 di0 do7 do6 do5 do4 do3 do2 do1 do0 sck20 si20 note so20 sio20 write intcsi20 note the value of the last...

Page 216

216 user’s manual u15331ej4v1ud chapter 12 serial interface 1a0 12.1 function of serial interface 1a0 serial interface 1a0 has the following three modes. • operation stop mode • 3-wire serial i/o mode • 3-wire serial i/o mode with automatic transmit/receive function (1) operation stop mode this mode...

Page 217

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 217 12.2 configuration of serial interface 1a0 serial interface 1a0 includes the following hardware. Table 12-1. Configuration of serial interface 1a0 item configuration registers serial i/o shift register 1a0 (sio1a0) automatic data transm...

Page 218

Chapter 12 serial interface 1a0 218 user’s manual u15331ej4v1ud (1) serial i/o shift register 1a0 (sio1a0) this is an 8-bit register used to carry out parallel/serial conversion and to carry out serial transmission/reception (shift operation) in synchronization with the serial clock. Sio1a0 is set w...

Page 219

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 219 12.3 control registers for serial interface 1a0 serial interface 1a0 is controlled by the following five registers. • serial operation mode register 1a0 (csim1a0) • automatic data transmit/receive control register 0 (adtc0) • automatic ...

Page 220

Chapter 12 serial interface 1a0 220 user’s manual u15331ej4v1ud figure 12-2. Format of serial operation mode register 1a0 symbol 6 3 2 1 0 address after reset r/w csim1a0 csie10 dir10 ate0 lsck10 0 0 scl101 scl100 ff78h 00h r/w specification of operation enable/disable csie10 shift register operatio...

Page 221

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 221 (2) automatic data transmit/receive control register 0 (adtc0) this register sets automatic reception enable/disable, the operation mode, and displays the state of automatic transmit/receive control. Adtc0 is set via a 1-bit or 8-bit me...

Page 222

Chapter 12 serial interface 1a0 222 user’s manual u15331ej4v1ud (3) automatic data transmit/receive interval specification register 0 (adti0) this register sets the automatic data transmit/receive function data transfer interval. Adti0 is set via a 1-bit or 8-bit memory manipulation instruction. Res...

Page 223

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 223 figure 12-4. Format of automatic data transmit/receive interval specification register 0 (2/2) symbol 6 5 address after reset r/w adti0 adti07 0 0 adti04 adti03 adti02 adti01 adti00 ff7bh 00h r/w adti04 adti03 adti02 adti01 adti00 data ...

Page 224

Chapter 12 serial interface 1a0 224 user’s manual u15331ej4v1ud 12.4 serial interface 1a0 operation serial interface 1a0 provides the following three modes. • operation stop mode • 3-wire serial i/o mode • 3-wire serial i/o mode with automatic transmit/receive function 12.4.1 operation stop mode in ...

Page 225

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 225 12.4.2 3-wire serial i/o mode the 3-wire serial i/o mode is useful for connection of peripheral i/os and display controllers, etc., which incorporate a conventional clocked serial interface, such as the 75xl series, 78k series, and 17k ...

Page 226

Chapter 12 serial interface 1a0 226 user’s manual u15331ej4v1ud symbol 6 3 2 1 0 address after reset r/w csim1a0 csie10 dir10 ate0 lsck10 0 0 scl101 scl100 ff78h 00h r/w specification of operation enable/disable csie10 shift register operation serial counter port note 0 operation stopped cleared por...

Page 227

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 227 (2) communication operation in 3-wire serial i/o mode, data transmission/reception is performed in 8-bit units. Data is transmitted/received bit by bit in synchronization with the serial clock. Serial i/o shift register 1a0 (sio1a0) shi...

Page 228

Chapter 12 serial interface 1a0 228 user’s manual u15331ej4v1ud figure 12-5. 3-wire serial i/o mode timing (2/2) (ii) slave operation timing 1 2 3 4 5 6 7 8 di7 di6 di5 di4 di3 di2 di1 di0 do7 do6 do5 do4 do3 do2 do1 do0 sck10 si10 note so10 sio1a0 write intcsi10 note the value of the last bit previ...

Page 229

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 229 (3) msb/lsb switching as the start bit in the 3-wire serial i/o mode, transfer can be selected to start from the msb or lsb. Figure 12-6 shows the configuration of serial i/o shift register 1a0 (sio1a0) and the internal bus. As shown in...

Page 230

Chapter 12 serial interface 1a0 230 user’s manual u15331ej4v1ud 12.4.3 3-wire serial i/o mode with automatic transmit/receive function this 3-wire serial i/o mode is used for transmission/reception of a maximum of 16-byte data without the use of software. Once transfer is started, the set number of ...

Page 231

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 231 symbol 6 3 2 1 0 address after reset r/w csim1a0 csie10 dir10 ate0 lsck10 0 0 scl101 scl100 ff78h 00h r/w specification of operation enable/disable csie10 shift register operation serial counter port note 0 operation stopped cleared por...

Page 232

Chapter 12 serial interface 1a0 232 user’s manual u15331ej4v1ud (b) automatic data transmit/receive control register 0 (adtc0) adtc0 is set via a 1-bit or 8-bit memory manipulation instruction. Reset input sets this register to 00h. Symbol 5 4 2 1 0 address after reset r/w adtc0 re0 arld0 0 0 trf0 0...

Page 233

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 233 (c) automatic data transmit/receive interval specification register 0 (adti0) adti0 is set via a 1-bit or 8-bit memory manipulation instruction. Reset input sets this register to 00h. Symbol 6 5 address after reset r/w adti0 adti07 0 0 ...

Page 234

Chapter 12 serial interface 1a0 234 user’s manual u15331ej4v1ud symbol 6 5 address after reset r/w adti0 adti07 0 0 adti04 adti03 adti02 adti01 adti00 ff7bh 00h r/w adti04 adti03 adti02 adti01 adti00 data transfer interval specification (f x = 5.0 mhz, f sck = 1.25 mhz) note 2 n 1 0 0 0 0 13.6 µ s +...

Page 235

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 235 (2) automatic transmit/receive data setting (a) transmit data setting write transmit data from the least significant address ffa0h of buffer ram (up to ffafh). The transmit data should be in the order from higher address to lower addres...

Page 236

Chapter 12 serial interface 1a0 236 user’s manual u15331ej4v1ud (3) communication operation (a) basic transmit/receive mode this transmit/receive mode is the same as the 3-wire serial i/o mode in which the specified number of data are transmitted/received in 8-bit units. Serial transfer is started w...

Page 237

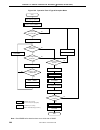

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 237 figure 12-8. Basic transmit/receive mode flowchart remark adtp0: automatic data transmit/receive address pointer 0 adti0: automatic data transmit/receive interval specification register 0 sio1a0: serial i/o shift register 1a0 trf0: bit ...

Page 238

Chapter 12 serial interface 1a0 238 user’s manual u15331ej4v1ud in 6-byte transmission/reception (bit 6 (arld0) and bit 7 (re0) of automatic data transmit/receive control register 0 (adtc0) = 0, and 1, respectively) in basic transmit/receive mode, buffer ram operates as follows. (i) before transmiss...

Page 239

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 239 figure 12-9. Buffer ram operation in 6-byte transmission/reception (in basic transmit/receive mode) (2/2) (b) 4th byte transmission/reception receive data 1 (r1) receive data 2 (r2) receive data 3 (r3) transmit data 4 (t4) transmit data...

Page 240

Chapter 12 serial interface 1a0 240 user’s manual u15331ej4v1ud (b) basic transmit mode in this mode, the specified number of 8-bit unit data are transmitted. Serial transfer is started when any data is written to serial i/o shift register 1a0 (sio1a0) while bit 7 (csie10) of serial operation mode r...

Page 241

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 241 figure 12-11. Basic transmit mode flowchart remark adtp0: automatic data transmit/receive address pointer 0 adti0: automatic data transmit/receive interval specification register 0 sio1a0: serial i/o shift register 1a0 trf0: bit 3 of au...

Page 242

Chapter 12 serial interface 1a0 242 user’s manual u15331ej4v1ud in 6-byte transmission (bit 6 (arld0) and bit 7 (re0) of automatic data transmit/receive control register 0 (adtc0) are 0) in basic transmit mode, buffer ram operates as follows. (i) before transmission (refer to figure 12-12 (a)) after...

Page 243

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 243 figure 12-12. Buffer ram operation in 6-byte transmission (in basic transmit mode) (2/2) (b) 4th byte transmission point transmit data 1 (t1) transmit data 2 (t2) transmit data 3 (t3) transmit data 4 (t4) transmit data 5 (t5) transmit d...

Page 244

Chapter 12 serial interface 1a0 244 user’s manual u15331ej4v1ud (c) repeat transmit mode in this mode, data stored in the buffer ram is transmitted repeatedly. Serial transfer is started by writing any data to serial shift i/o register 1a0 (sio1a0) when bit 7 (csie10) of serial operation mode regist...

Page 245

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 245 figure 12-14. Repeat transmit mode flowchart start write transmit data in buffer ram set adtp0 to the value (pointer value) obtained by subtracting 1 from the number of transmit data bytes set the transmission/reception operation interv...

Page 246

Chapter 12 serial interface 1a0 246 user’s manual u15331ej4v1ud in 6-byte transmission (bit 6 (arld0) and bit 7 (re0) of automatic data transmit/receive control register 0 (adtc0) are 1 and 0, respectively) in repeat transmit mode, buffer ram operates as follows. (i) before transmission (refer to fi...

Page 247

Chapter 12 serial interface 1a0 user’s manual u15331ej4v1ud 247 figure 12-15. Buffer ram operation in 6-byte transmission (in repeat transmit mode) (2/2) (c) upon completion of transmission of 6 bytes transmit data 1 (t1) transmit data 2 (t2) transmit data 3 (t3) transmit data 4 (t4) transmit data 5...

Page 248