- DL manuals

- NEC

- Computer Hardware

- µPD78081

- User Manual

NEC µPD78081 User Manual

Summary of µPD78081

Page 1

µ pd78081 µ pd78081(a) µ pd78082 µ pd78082(a) µ pd78p083 µ pd78p083(a) µ pd78p081(a2) µ pd78083 subseries 8-bit single-chip microcontroller document no. U12176ej2v0um00 (2nd edition) (o. D. No. Ieu-886) date published may 1997 n printed in japan © 1992 1994.

Page 2

Notes for cmos devices 1 precaution against esd for semiconductors note: strong electric field, when exposed to a mos device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and qui...

Page 3

Fip, iebus, and qtop are trademarks of nec corporation. Ms-dos and windows are either registered trademarks or trademarks of microsoft corporation in the united states and/or other countries. Ibm dos, pc/at and pc dos are trademarks of international business machines corporation. Hp9000 series 300, ...

Page 4

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins. The information in this document is subject to change without notice. No part of this document may be copied or reproduced in any form or by any means without the prior written con...

Page 5: Regional Information

Nec electronics inc. (u.S.) santa clara, california tel: 800-366-9782 fax: 800-729-9288 nec electronics (germany) gmbh duesseldorf, germany tel: 0211-65 03 02 fax: 0211-65 03 490 nec electronics (uk) ltd. Milton keynes, uk tel: 01908-691-133 fax: 01908-670-290 nec electronics italiana s.R.1. Milano,...

Page 6

Major revision in this edition page description throughout the following products have been already developed µ pd78081cu- ××× , 78081gb- ××× -3b4, 78082cu- ××× , 78082gb- ××× -3b4, 78p083cu, 78p083du, 78p083gb-3b4 the following products have been added µ pd78081gb- ××× -3bs-mtx, 78082gb- ××× -3bs-m...

Page 7

Preface readers this manual has been prepared for user engineers who want to understand the functions of the µ pd78083 subseries and design and develop its application systems and programs. Caution in the µ pd78083 subseries, the µ pd78p083du is not designed to maintain the reliability required for ...

Page 8

To know application examples of the functions provided in the µ pd78083 subseries: → refer to application note separately provided. Legend data representation weight : high digits on the left and low digits on the right active low representations : ××× (line over the pin and signal names) note : des...

Page 9

Related documents the related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such. Related documents for µ pd78054 subseries document name document no. Japanese english µ pd78083 subseries user’s manual u12176j this manual µ ...

Page 10

Development tool documents (user’s manuals) document name document no. Japanese english ra78k series assembler package operation eeu-809 eeu-1399 language eeu-815 eeu-1404 ra78k series structured assembler preprocessor eeu-817 eeu-1402 ra78k0 assembler package structured assembly language u11789j u1...

Page 11

Documents for embedded software (user’s manual) document name document no. Japanese english 78k/0 series real-time os basics u11537j — installation u11536j — technicals u11538j — os for 78k/0 series mx78k0 basics eeu-5010 — fuzzy knowledge data creation tool eeu-829 eeu-1438 78k/0, 78k/ii, 87ad seri...

Page 12

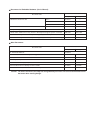

– i – contents chapter 1 outline ..................................................................................................................... 1 1.1 features ............................................................................................................................. 1 1.2 ap...

Page 13

– ii – 3.2.3 special function register (sfr) ......................................................................................... 37 3.3 instruction address addressing ..................................................................................... 40 3.3.1 relative addressing ...............

Page 14

– iii – 6.4 8-bit timer/event counters 5 and 6 operations ............................................................ 90 6.4.1 interval timer operations ...................................................................................................... 90 6.4.2 external event counter operation ....

Page 15

– iv – 12.4 interrupt servicing operations ........................................................................................ 181 12.4.1 non-maskable interrupt request acknowledge operation .................................................... 181 12.4.2 maskable interrupt request acknowledge o...

Page 16

– v – a.5 system-upgrade method from other in-circuit emulators to 78k/0 series in-circuit emulator ............................................................................................................ 240 appendix b embedded software .............................................................

Page 17

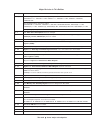

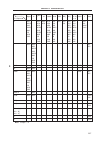

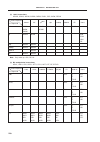

– vi – figure (1/4) fig. No. Title page 2-1 pin input/output circuit of list ............................................................................................ 23 3-1 memory map ( µ pd78081) .................................................................................................. ...

Page 18

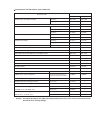

– vii – figure (2/4) fig. No. Title page 6-10 8-bit timer mode control register setting for external event counter operation ............. 93 6-11 external event counter operation timings (with rising edge specification) .................... 93 6-12 8-bit timer mode control register settings for squ...

Page 19

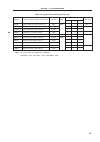

– viii – figure (3/4) fig. No. Title page 11-6 baud rate generator control register format (2/2) ......................................................... 145 11-7 asynchronous serial interface transmit/receive data format .......................................... 157 11-8 asynchronous serial inter...

Page 20

– ix – figure (4/4) fig. No. Title page 15-6 prom read timing ........................................................................................................... 213 a-1 development tool configuration ........................................................................................ 23...

Page 21

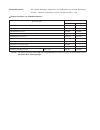

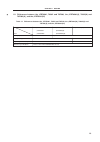

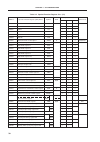

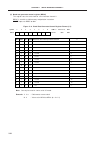

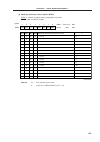

– x – table (1/2) table. No. Title page 1-1 differences between the µ pd78081, 78082 and 78p083, the µ pd78081(a), 78082(a) and 78p083(a), and the µ pd78081(a2) ............................................................................ 13 2-1 type of input/output circuit of each pin .................

Page 22

– xi – table (2/2) table. No. Title page 12-1 interrupt source list ........................................................................................................... 172 12-2 various flags corresponding to interrupt request sources .............................................. 175 12-3 ti...

Page 23

– xii – [memo].

Page 24

1 chapter 1 outline chapter 1 outline 1.1 features on-chip rom and ram note the capacities of internal prom and internal high-speed ram can be changed by means of the memory size switching register (ims). Instruction execution time changeable from high speed (0.4 µ s: in main system clock 5.0 mhz op...

Page 25

2 chapter 1 outline 1.2 applications µ pd78081, 78082, 78p083: airbags, crt displays, keyboards, air conditioners, hot water dispensers, boilers, fan heaters, dashboards, etc. µ pd78081(a), 78082(a), 78p083(a), 78081(a2): automobile electrical control devices, gas detector cutoff devices, various sa...

Page 26

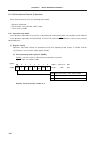

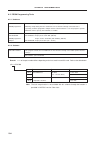

3 chapter 1 outline 1.4 quality grade part number package quality grade µ pd78081cu- ××× 42-pin plastic shrink dip (600 mil) standard µ pd78081gb- ××× -3b4 44-pin plastic qfp (10 × 10 mm) standard µ pd78081gb- ××× -3bs-mtx 44-pin plastic qfp (10 × 10 mm) standard µ pd78082cu- ××× 42-pin plastic shri...

Page 27

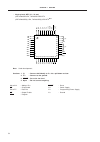

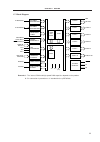

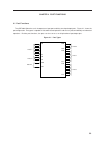

4 chapter 1 outline 1.5 pin configuration (top view) (1) normal operating mode 42-pin plastic shrink dip (600 mil) µ pd78081cu- ××× , 78082cu- ××× , 78p083cu, 78p083cu(a) 42-pin ceramic shrink dip (with window) (600 mil) µ pd78p083du 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 v ss p54 p53...

Page 28

5 chapter 1 outline • 44-pin plastic qfp (10 × 10 mm) µ pd78081gb- ××× -3b4, 78081gb- ××× -3bs-mtx µ pd78082gb- ××× -3b4, 78082gb- ××× -3bs-mtx µ pd78p083gb-3b4, 78p083gb-3bs-mtx µ pd78081gb(a)- ××× -3b4, 78082gb(a)- ××× -3b4 µ pd78p083gb(a)-3b4, 78p083gb(a)-3bs-mtx note µ pd78p081gb(a2)- ××× -3b4 n...

Page 29

6 chapter 1 outline pin identifications ani0 to ani7 : analog input p100, p101 : port 10 asck : asynchronous serial clock pcl : programmable clock av dd : analog power supply reset : reset av ref : analog reference voltage rxd : receive data av ss : analog ground sck2 : serial clock buz : buzzer clo...

Page 30

7 chapter 1 outline (2) prom programming mode • 42-pin plastic shrink dip (600 mil) µ pd78p083cu, 78p083cu(a) • 42-pin ceramic shrink dip (with window) (600 mil) µ pd78p083du cautions 1. (l) : individually connect to v ss via a pull-down resistor. 2. V ss : connect to the ground. 3. Reset : set to t...

Page 31

8 chapter 1 outline note under development cautions 1. (l) : connect individually to v ss via a pull-down resistor. 2. V ss : connect to the ground. 3. Reset : set to the low level. 4. Open : do not connect anything. A0 to a14 : address bus reset : reset ce : chip enable v dd : power supply d0 to d7...

Page 32

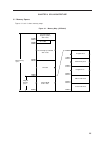

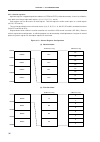

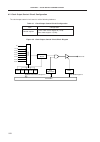

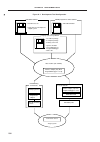

9 chapter 1 outline 1.6 78k/0 series development the following shows the 78k/0 series products development. Subseries names are shown inside frames. Note under planning 100-pin 100-pin 100-pin 100-pin 80-pin 80-pin 80-pin 64-pin 64-pin 64-pin 64-pin 64-pin 64-pin 64-pin 42/44-pin 100-pin 100-pin 80-...

Page 33

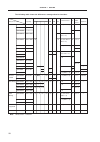

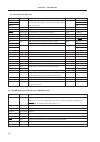

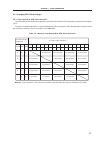

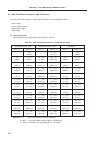

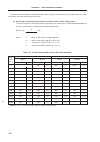

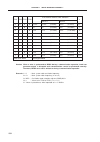

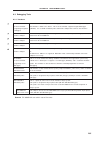

10 chapter 1 outline the following table shows the differences among subseries functions. Function rom timer 8-bit 10-bit 8-bit serial interface i/o external subseries name capacity 8-bit 16-bit watch wdt a/d a/d d/a expansion control µ pd78075b 32k to 40k 4 ch 1 ch 1 ch 1 ch 8 ch — 2 ch 3 ch (uart:...

Page 34

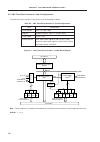

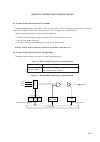

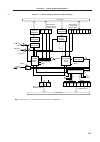

11 chapter 1 outline 1.7 block diagram remarks 1. The internal rom and high-speed ram capacities depend on the product. 2. Pin connection in parentheses is intended for the µ pd78p083. P100/ti5/to5 p101/ti6/to6 si2/r x d/p70 so2/t x d/p71 sck2/asck/p72 ani0/p10- ani7/p17 av dd av ss av ref intp1/p01...

Page 35

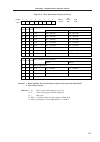

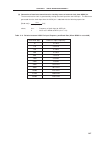

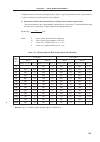

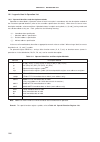

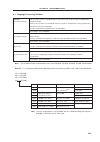

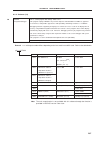

12 chapter 1 outline 1.8 outline of function part number µ pd78081 µ pd78082 µ pd78083 item internal memory rom mask rom prom 8 kbytes 16 kbytes 24 kbytes note high-speed ram 256 bytes 384 bytes 512 bytes note memory space 64 kbytes general register 8 bits × 32 registers (8 bits × 8 registers × 4 ba...

Page 36

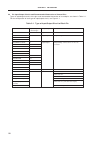

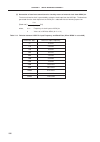

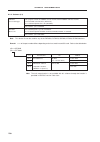

13 chapter 1 outline 1.9 differences between the µ pd78081, 78082 and 78p083, the µ pd78081(a), 78082(a) and 78p083(a), and the µ pd78081(a2) table 1-1 differences between the µ pd78081, 78082 and 78p083, the µ pd78081(a), 78082(a) and 78p083(a), and the µ pd78081(a2) part number µ pd78081 µ pd78081...

Page 37

14 chapter 1 outline [memo].

Page 38

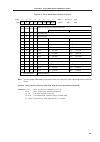

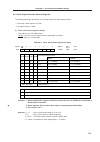

15 chapter 2 pin function chapter 2 pin function 2.1 pin function list 2.1.1 normal operating mode pins (1) port pins note when p10/ani0-p17/ani7 pins are used as the analog inputs for the a/d converter, set the port 1 to the input mode. The on-chip pull-up resistor is automatically disabled. Pin na...

Page 39

16 chapter 2 pin function pin name input/output function after reset alternate function intp1 input external interrupt request input by which the active edge input p01 intp2 (rising edge, falling edge, or both rising and falling edges) p02 intp3 can be specified. P03 si2 input serial interface seria...

Page 40

17 chapter 2 pin function 2.2 description of pin functions 2.2.1 p00 to p03 (port 0) these are 4-bit input/output ports. Besides serving as input/output ports, they function as an external interrupt request input. The following operating modes can be specified bit-wise. (1) port mode p00 functions a...

Page 41

18 chapter 2 pin function 2.2.3 p30 to p37 (port 3) these are 8-bit input/output ports. Beside serving as input/output ports, they function as clock output and buzzer output. The following operating modes can be specified bit-wise. (1) port mode these ports function as 8-bit input/output ports. They...

Page 42

19 chapter 2 pin function 2.2.5 p70 to p72 (port 7) this is a 3-bit input/output port. In addition to its use as an input/output port, it also has serial interface data input/ output and clock input/output functions. The following operating modes can be specified bit-wise. (1) port mode port 7 funct...

Page 43

20 chapter 2 pin function 2.2.7 av ref a/d converter reference voltage input pin. When a/d converter is not used, connect this pin to v ss . 2.2.8 av dd analog power supply pin of a/d converter. Always use the same voltage as that of the v dd pin even when a/d converter is not used. 2.2.9 av ss this...

Page 44

21 chapter 2 pin function 2.2.15 ic (mask rom version only) the ic (internally connected) pin is provided to set the test mode to check the µ pd78083 subseries at delivery. Connect it directly to the v ss with the shortest possible wire in the normal operating mode. When a voltage difference is prod...

Page 45

22 chapter 2 pin function pin name input/output input/output recommended connection for unused pins circuit type p00 2 input connect to v ss . P01/intp1 8-a input/output independently connect to v ss via a resistor. P02/intp2 p03/intp3 p10/ani0-p17/ani7 11 input/output independently connect to v dd ...

Page 46

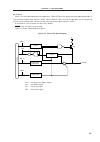

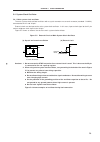

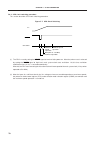

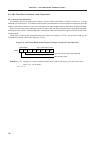

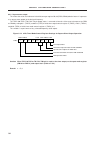

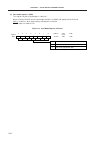

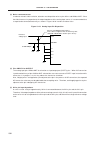

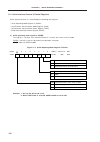

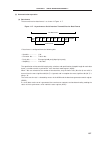

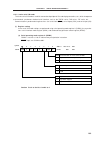

23 chapter 2 pin function figure 2-1. Pin input/output circuit of list in pull-up enable v dd p-ch in/out input enable output disable data v dd p-ch n-ch type 2 type 5-a schmitt-triggered input with hysteresis characteristics type 11 type 8-a pull-up enable v dd p-ch in/out output disable data v dd ...

Page 47

24 chapter 2 pin function [memo].

Page 48

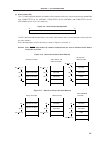

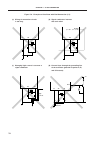

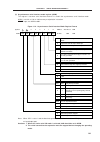

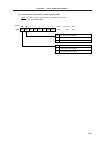

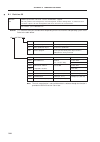

25 chapter 3 cpu architecture chapter 3 cpu architecture 3.1 memory spaces figures 3-1 to 3-3 shows memory maps. Figure 3-1. Memory map ( µ pd78081) data memory space general registers 32 × 8 bits internal rom 8192 × 8 bits callf entry area callt table area vector table area program area program are...

Page 49

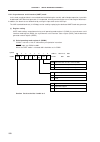

26 chapter 3 cpu architecture figure 3-2. Memory map ( µ pd78082) data memory space general registers 32 × 8 bits internal rom 16384 × 8 bits callf entry area callt table area vector table area program area program area unusable program memory space internal high-speed ram 384 × 8 bits special funct...

Page 50

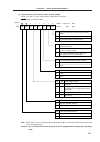

27 chapter 3 cpu architecture figure 3-3. Memory map ( µ pd78p083) data memory space general registers 32 × 8 bits internal prom 24576 × 8 bits callf entry area callt table area vector table area program area program area unusable program memory space internal high-speed ram 512 × 8 bits special fun...

Page 51

28 chapter 3 cpu architecture 3.1.1 internal program memory space the internal program memory is mask rom with a 8192 × 8-bit configuration in the µ pd78081, and a 16384 × 8-bit configuration in the µ pd78082, and prom with a 24576 × 8-bit configuration in the µ pd78p083. The internal program memory...

Page 52

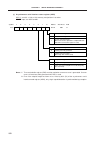

29 chapter 3 cpu architecture 3.1.2 internal data memory space the internal high speed ram configuration is 256 × 8-bit in the µ pd78081, 384 × 8-bit in the µ pd78082 and 512 × 8-bit in the µ pd8p083. In this area, four banks of general registers, each bank consisting of eight 8-bit registers, are a...

Page 53

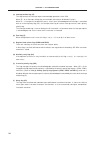

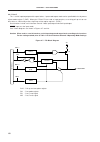

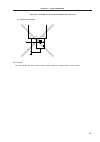

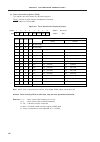

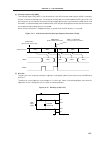

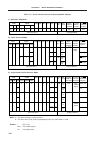

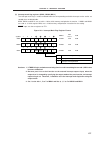

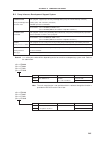

30 chapter 3 cpu architecture figure 3-4. Data memory addressing ( µ pd78081) general registers 32 × 8 bits internal rom 8192 × 8 bits unusable internal high-speed ram 256 × 8 bits special function registers (sfrs) 256 × 8 bits sfr addressing register addressing short direct addressing direct addres...

Page 54

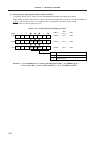

31 chapter 3 cpu architecture figure 3-5. Data memory addressing ( µ pd78082) general registers 32 × 8 bits internal rom 16384 × 8 bits unusable internal high-speed ram 384 × 8 bits special function registers (sfrs) 256 × 8 bits sfr addressing register addressing short direct addressing direct addre...

Page 55

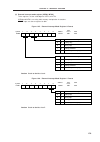

32 chapter 3 cpu architecture figure 3-6. Data memory addressing ( µ pd78p083) general registers 32 × 8 bits internal prom 24576 × 8 bits unusable internal high-speed ram 512 × 8 bits special function registers (sfrs) 256 × 8 bits sfr addressing register addressing short direct addressing direct add...

Page 56

33 chapter 3 cpu architecture 7 0 ie z rbs1 ac rbs0 0 isp cy pc 15 0 3.2 processor registers the µ pd78083 subseries units incorporate the following processor registers. 3.2.1 control registers the control registers control the program sequence, statuses and stack memory. The control registers consi...

Page 57

34 chapter 3 cpu architecture (a) interrupt enable flag (ie) this flag controls the interrupt request acknowledge operations of the cpu. When ie = 0, all interrupts except the non-maskable interrupt are disabled (di status). When ie = 1, interrupts are enabled (ei status). At this time, acknowledgme...

Page 58

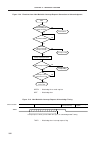

35 chapter 3 cpu architecture reti and retb instruction psw pc15-pc8 pc15-pc8 pc7-pc0 register pair lower sp sp + 2 sp register pair upper ret instruction pop rp instruction sp + 1 pc7-pc0 sp sp + 2 sp sp + 1 sp + 2 sp sp + 1 sp sp + 3 interrupt and brk instruction psw pc15-pc8 pc15-pc8 pc7-pc0 regi...

Page 59

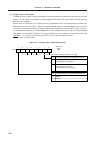

36 chapter 3 cpu architecture bank0 bank1 bank2 bank3 feffh fef8h fee0h hl de bc ax h 15 0 7 0 l d e b c a x 16-bit processing 8-bit processing fef0h fee8h bank0 bank1 bank2 bank3 feffh fef8h fee0h rp3 rp2 rp1 rp0 r7 15 0 7 0 r6 r5 r4 r3 r2 r1 r0 16-bit processing 8-bit processing fef0h fee8h 3.2.2 ...

Page 60

37 chapter 3 cpu architecture 3.2.3 special function register (sfr) unlike a general register, each special-function register has special functions. It is allocated in the ff00h to ffffh area. The special-function register can be manipulated like the general register, with the operation, transfer an...

Page 61

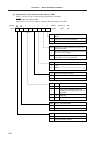

38 chapter 3 cpu architecture address special-function register (sfr) name symbol r/w after reset ff00h port0 p0 r/w √ √ — 00h ff01h port1 p1 √ √ — ff03h port3 p3 √ √ — ff05h port5 p5 √ √ — ff07h port7 p7 √ √ — ff0ah port10 p10 √ √ — ff1fh a/d conversion result register adcr r √ √ — undefined ff20h ...

Page 62

39 chapter 3 cpu architecture address special-function register (sfr) name symbol r/w after reset ffeah priority order specify flag register 1l pr1l r/w √ √ — ffh ffech external interrupt mode register 0 intm0 — √ — 00h ffedh external interrupt mode register 1 intm1 — √ — fff0h memory size switching...

Page 63

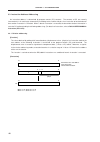

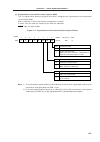

40 chapter 3 cpu architecture 15 0 pc + 15 0 8 7 6 s 15 0 pc α jdisp8 when s = 0, all bits of α are 0. When s = 1, all bits of α are 1. Pc indicates the start address of the instruction after the br instruction. ... 3.3 instruction address addressing an instruction address is determined by program c...

Page 64

41 chapter 3 cpu architecture 3.3.2 immediate addressing [function] immediate data in the instruction word is transferred to the program counter (pc) and branched. This function is carried out when the call !Addr16 or br !Addr16 or callf !Addr11 instruction is executed. The call !Addr16 and br !Addr...

Page 65

42 chapter 3 cpu architecture 3.3.3 table indirect addressing [function] table contents (branch destination address) of the particular location to be addressed by bits 1 to 5 of the immediate data of an operation code are transferred to the program counter (pc) and branched. Before the callt [addr5]...

Page 66

43 chapter 3 cpu architecture 7 0 rp 0 7 a x 15 0 pc 8 7 3.3.4 register addressing [function] register pair (ax) contents to be specified with an instruction word are transferred to the program counter (pc) and branched. This function is carried out when the br ax instruction is executed. [illustrat...

Page 67

44 chapter 3 cpu architecture 3.4 operand address addressing the following various methods are available to specify the register and memory (addressing) which undergo manipulation during instruction execution. 3.4.1 implied addressing [function] the register which functions as an accumulator (a and ...

Page 68

45 chapter 3 cpu architecture 3.4.2 register addressing [function] this addressing accesses a general register as an operand. The general register accessed is specified by the register bank select flags (rbs0 and rbs1) and register specify code (rn or rpn) in an instruction code. Register addressing...

Page 69

46 chapter 3 cpu architecture 3.4.3 direct addressing [function] this addressing directly addresses the memory indicated by the immediate data in an instruction word. [operand format] identifier description addr16 label or 16-bit immediate data [description example] mov a, !0fe00h; when setting !Add...

Page 70

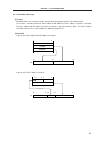

47 chapter 3 cpu architecture 3.4.4 short direct addressing [function] the memory to be manipulated in the fixed space is directly addressed with 8-bit data in an instruction word. The fixed space to which this address is applied is a 256-byte space of addresses fe20h through ff1fh. An internal high...

Page 71

48 chapter 3 cpu architecture 15 0 short direct memory effective address 1 1 1 1 1 1 1 8 7 0 7 op code saddr-offset α [description example] mov 0fe30h, #50h; when setting saddr to fe30h and immediate data to 50h operation code 0 0 0 1 0 0 0 1 op code 0 0 1 1 0 0 0 0 30h (saddr-offset) 0 1 0 1 0 0 0 ...

Page 72

49 chapter 3 cpu architecture 15 0 sfr effective address 1 1 1 1 1 1 1 8 7 0 7 op code sfr-offset 1 3.4.5 special-function register (sfr) addressing [function] the memory-mapped special-function register (sfr) is addressed with 8-bit immediate data in an instruction word. This addressing is applied ...

Page 73

50 chapter 3 cpu architecture 3.4.6 register indirect addressing [function] this addressing addresses the memory with the contents of a register pair specified as an operand. The register pair to be accessed is specified by the register bank select flags (rbs0 and rbs1) and register pair specify cod...

Page 74

51 chapter 3 cpu architecture 3.4.7 based addressing [function] this addressing addresses the memory by adding 8-bit immediate data to the contents of the hl register pair which is used as a base register and by using the result of the addition. The hl register pair to be accessed is in the register...

Page 75

52 chapter 3 cpu architecture 3.4.8 based indexed addressing [function] this addressing addresses the memory by adding the contents of the hl register, which is used as a base register, to the contents of the b or c register specified in the instruction word, and by using the result of the addition....

Page 76

53 chapter 4 port functions chapter 4 port functions 4.1 port functions the µ pd78083 subseries units incorporate an input port and thirty-two input/output ports. Figure 4-1 shows the port configuration. Every port is capable of 1-bit and 8-bit manipulations and can carry out considerably varied con...

Page 77

54 chapter 4 port functions pin name input/output function dual-function pin p00 input port 0 input only — p01 input/output 4-bit input/output port input/output is specifiable bit-wise. When intp1 p02 used as the input port, it is possible to connect intp2 p03 a pull-up resistor by software. Intp3 p...

Page 78

55 chapter 4 port functions 4.2 port configuration a port consists of the following hardware: table 4-2. Port configuration item configuration control register port mode register (pmm: m = 0, 1, 3, 5, 7, 10) pull-up resistor option register (puoh, puol) port total: 33 ports (1 input, 32 inputs/outpu...

Page 79

56 chapter 4 port functions figure 4-2. P00 block diagram figure 4-3. P01 to p03 block diagram puo : pull-up resistor option register pm : port mode register rd : port 0 read signal wr : port 0 write signal p00 rd internal bus p-ch wr pm wr port rd wr puo v dd p01/intp1 p03/intp3 selector puo0 outpu...

Page 80

57 chapter 4 port functions 4.2.2 port 1 port 1 is an 8-bit input/output port with output latch. It can specify the input mode/output mode in 1-bit units with a port mode register 1 (pm1). When p10 to p17 pins are used as input ports, an on-chip pull-up resistor can be used to them in 8-bit units wi...

Page 81

58 chapter 4 port functions 4.2.3 port 3 port 3 is an 8-bit input/output port with output latch. P30 to p37 pins can specify the input mode/output mode in 1-bit units with the port mode register 3 (pm3). When p30 to p37 pins are used as input ports, an on-chip pull-up resistor can be used to them in...

Page 82

59 chapter 4 port functions 4.2.4 port 5 port 5 is an 8-bit input/output port with output latch. P50 to p57 pins can specify the input mode/output mode in 1-bit units with the port mode register 5 (pm5). When p50 to p57 pins are used as input ports, an on-chip pull-up resistor can be used to them in...

Page 83

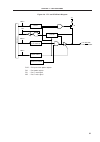

60 chapter 4 port functions 4.2.5 port 7 this is a 3-bit input/output port with output latches. Input mode/output mode can be specified bit-wise by means of port mode register 7 (pm7). When pins p70 to p72 are used as input port pins, an on-chip pull-up resistor can be used as a 3-bit unit by means ...

Page 84

61 chapter 4 port functions figure 4-8. P71 and p72 block diagram puo : pull-up resistor option register pm : port mode register rd : port 7 read signal wr : port 7 write signal p-ch wr pm wr port rd wr puo v dd selector puo7 output latch (p71 and p72) pm71, pm72 internal bus alternate function p71/...

Page 85

62 chapter 4 port functions 4.2.6 port 10 this is an 2-bit input/output port with output latches. Input mode/output mode can be specified bit-wise by means of port mode register 10 (pm10). When pins p100 to p101 are used as input port pins, an on-chip pull-up resistor can be used as an 2-bit unit by...

Page 86

63 chapter 4 port functions 4.3 port function control registers the following two types of registers control the ports. • port mode registers (pm0, pm1, pm3, pm5, pm7, pm10) • pull-up resistor option register (puoh, puol) (1) port mode registers (pm0, pm1, pm3, pm5, pm7, pm10) these registers are us...

Page 87

64 chapter 4 port functions table 4-3. Port mode register and output latch settings when using dual-functions p01 to p03 intp1 to intp3 input 1 × p10 to p17 note ani0 to ani7 input 1 × p35 pcl output 0 0 p36 buz output 0 0 p100 ti5 input 1 × to5 output 0 0 p101 ti6 input 1 × to6 output 0 0 dual-func...

Page 88

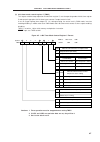

65 chapter 4 port functions figure 4-10. Port mode register format pm0 pm1 1 1 pm03 pm02 pm01 1 7 6 5 4 3 2 1 0 symbol pm3 pm5 ff20h ff21h ff23h ff25h ffh ffh ffh ffh r/w r/w r/w r/w address after reset r/w pm17 pm16 pm15 pm14 pm13 pm12 pm11 pm10 pm37 pm36 pm35 pm34 pm33 pm32 pm31 pm30 pm57 pm56 pm5...

Page 89

66 chapter 4 port functions (2) pull-up resistor option register (puoh, puol) this register is used to set whether to use an internal pull-up resistor at each port or not. A pull-up resistor is internally used at bits which are set to the input mode at a port where on-chip pull-up resistor use has b...

Page 90

67 chapter 4 port functions 4.4 port function operations port operations differ depending on whether the input or output mode is set, as shown below. 4.4.1 writing to input/output port (1) output mode a value is written to the output latch by a transfer instruction, and the output latch contents are...

Page 91

68 chapter 4 port functions [memo].

Page 92

69 chapter 5 clock generator chapter 5 clock generator 5.1 clock generator functions the clock generator generates the clock to be supplied to the cpu and peripheral hardware. The following type of system clock oscillator is available. Main system clock oscillator this circuit oscillates at frequenc...

Page 93

70 chapter 5 clock generator figure 5-1. Block diagram of clock generator main system clock oscillator x2 x1 stop pcc2 pcc1 internal bus standby control circuit 2 f xx 2 2 f xx 2 3 f xx 2 4 f xx prescaler clock to peripheral hardware prescaler oscillation mode selection register f xx cpu clock (f cp...

Page 94

71 chapter 5 clock generator 5.3 clock generator control register the clock generator is controlled by the following two registers: • processor clock control register (pcc) • oscillation mode selection register (osms) (1) processor clock control register (pcc) the pcc sets whether to use cpu clock s...

Page 95

72 chapter 5 clock generator write to osms (mcs 0) f xx max. 2/f x operating at f xx = f x /2 (mcs = 0) operating at f xx = f x /2 (mcs = 0) mcs main system clock scaler control 0 1 scaler used scaler not used 0 0 0 0 osms fff2h 7 6 5 4 3 2 symbol 1 0 mcs 0 0 address after reset r/w 00h w 0 (2) osci...

Page 96

73 chapter 5 clock generator 5.4 system clock oscillator 5.4.1 main system clock oscillator the main system clock oscillator oscillates with a crystal resonator or a ceramic resonator (standard: 5.0 mhz) connected to the x1 and x2 pins. External clocks can be input to the main system clock oscillato...

Page 97

74 chapter 5 clock generator figure 5-6. Examples of oscillator with bad connection (1/2) (a) wiring of connection circuits (b) signal conductors intersect is too long with each other (c) changing high current is too near a (d) current flows through the grounding line signal conductor of the ocsilla...

Page 98

75 chapter 5 clock generator figure 5-6. Examples of oscillator with bad connection (2/2) (c) signals are fetched 5.4.2 scaler the scaler divides the main system clock oscillator output (f xx ) and generates various clocks. Ic x2 x1.

Page 99

76 chapter 5 clock generator 5.5 clock generator operations the clock generator generates the following various types of clocks and controls the cpu operating mode including the standby mode. • main system clock f xx • cpu clock f cpu • clock to peripheral hardware the following clock generator func...

Page 100

77 chapter 5 clock generator 5.6 changing cpu clock settings 5.6.1 time required for cpu clock switchover the cpu clock can be switched over by means of bits 0 to 2 (pcc0 to pcc2) of the processor clock control register (pcc). The actual switchover operation is not performed directly after writing t...

Page 101

78 chapter 5 clock generator 5.6.2 cpu clock switching procedure this section describes cpu clock switching procedure. Figure 5-7. Cpu clock switching (1) the cpu is reset by setting the reset signal to low level after power-on. After that, when reset is released by setting the reset signal to high ...

Page 102

79 chapter 6 8-bit timer/event counters 5 and 6 chapter 6 8-bit timer/event counters 5 and 6 the timers incorporated into the µ pd78083 subseries are outlined below. (1) 8-bit timers/event counters 5 and 6 (tm5 and tm6) this can be used to serve as an interval timer, an external event counter, squar...

Page 103

80 chapter 6 8-bit timer/event counters 5 and 6 6.1 8-bit timer/event counters 5 and 6 functions the 8-bit timer/event counters 5 and 6 (tm5 and tm6) have the following functions. • interval timer • external event counter • square-wave output • pwm output (1) 8-bit interval timer interrupt requests ...

Page 104

81 chapter 6 8-bit timer/event counters 5 and 6 (2) external event counter the number of pulses of an externally input signal can be measured. (3) square-wave output a square wave with any selected frequency can be output. Table 6-3. 8-bit timer/event counters 5 and 6 square-wave output ranges minim...

Page 105

82 chapter 6 8-bit timer/event counters 5 and 6 6.2 8-bit timer/event counters 5 and 6 configurations the 8-bit timer/event counters 5 and 6 consist of the following hardware. Table 6-4. 8-bit timer/event counters 5 and 6 configurations item configuration timer register 8 bits × 2 (tm5, tm6) registe...

Page 106

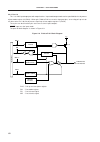

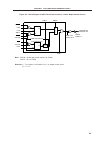

83 chapter 6 8-bit timer/event counters 5 and 6 figure 6-2. Block diagram of 8-bit timer/event counters 5 and 6 output control circuit note pm100 : bit 0 of port mode register 10 (pm10) pm101 : bit 1 of pm10 remarks 1. The section in the broken line is an output control circuit. 2. N = 5, 6 reset lv...

Page 107

84 chapter 6 8-bit timer/event counters 5 and 6 (1) compare registers 50 and 60 (cr50, cr60) these are 8-bit registers to compare the value set to cr50 to the 8-bit timer register 5 (tm5) count value, and the value set to cr60 to the 8-bit timer register 6 (tm6) count value, and, if they match, gene...

Page 108

85 chapter 6 8-bit timer/event counters 5 and 6 figure 6-3. Timer clock select register 5 format note the timer output (pwm output) cannot be used in cases where the clock is being input from an external source. Caution when rewriting tcl5 to other data, stop the timer operation beforehand. Remarks ...

Page 109

86 chapter 6 8-bit timer/event counters 5 and 6 (2) timer clock select register 6 (tcl6) this register sets count clocks of 8-bit timer register 6. Tcl6 is set with an 8-bit memory manipulation instruction. Reset input sets tcl6 to 00h. Figure 6-4. Timer clock select register 6 format note when cloc...

Page 110

87 chapter 6 8-bit timer/event counters 5 and 6 (3) 8-bit timer mode control register 5 (tmc5) this register enables/stops operation of 8-bit timer register 5, sets the operating mode of 8-bit timer register 5 and controls operation of 8-bit timer/event counter 5 output control circuit. It sets r-s ...

Page 111

88 chapter 6 8-bit timer/event counters 5 and 6 (4) 8-bit timer mode control register 6 (tmc6) this register enables/stops operation of 8-bit timer register 6, sets the operating mode of 8-bit timer register 6 and controls operation of 8-bit timer/event counter 6 output control circuit. It sets r-s ...

Page 112

89 chapter 6 8-bit timer/event counters 5 and 6 (5) port mode register 10 (pm10) this register sets port 10 input/output in 1-bit units. When using the p100/ti5/to5 and p101/ti6/to6 pins for timer output, set pm100, pm101, and output latches of p100 and p101 to 0. Pm10 is set with a 1-bit or 8-bit m...

Page 113

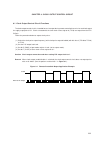

90 chapter 6 8-bit timer/event counters 5 and 6 6.4 8-bit timer/event counters 5 and 6 operations 6.4.1 interval timer operations by setting the 8-bit timer mode control registers 5 and 6 (tmc5 and tmc6) as shown in figure 6-8, it can be operated as an interval timer. The 8-bit timer/event counters ...

Page 114

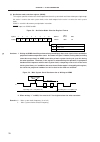

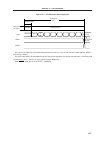

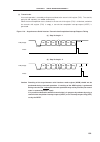

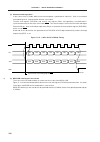

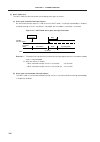

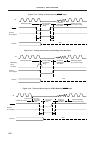

91 chapter 6 8-bit timer/event counters 5 and 6 count clock tmn count value inttmn tcen crn0 ton interval time interval time interval time interrupt request acknowledge interrupt request acknowledge n n n n clear count start clear t 00 01 n 00 01 n 00 01 n figure 6-9. Interval timer operation timing...

Page 115

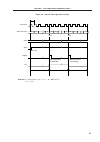

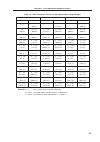

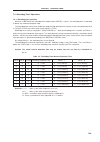

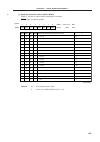

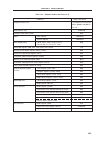

92 chapter 6 8-bit timer/event counters 5 and 6 table 6-5. 8-bit timer/event counters 5 and 6 interval times minimum interval time maximum interval time resolution mcs = 1 mcs = 0 mcs = 1 mcs = 0 mcs = 1 mcs = 0 0 0 0 0 tin input cycle 2 8 × tin input cycle tin input edge cycle 0 0 0 1 tin input cyc...

Page 116

93 chapter 6 8-bit timer/event counters 5 and 6 6.4.2 external event counter operation the external event counter counts the number of external clock pulses to be input to the ti5/pi00/to5 and ti6/ p101/to6 pins with 8-bit timer registers 5 and 6 (tm5 and tm6). Tm5 and tm6 are incremented each time ...

Page 117

94 chapter 6 8-bit timer/event counters 5 and 6 6.4.3 square-wave output this makes the value set in advance in the 8-bit conveyor register 50, 60 (cr50, cr60) to be the interval. It operates as a square wave output at the desired frequency. The to5/p100/ti5 or to6/p101/ti6 pin output status is reve...

Page 118

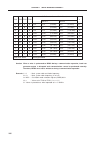

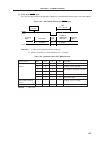

95 chapter 6 8-bit timer/event counters 5 and 6 table 6-6. 8-bit timer/event counters 5 and 6 square-wave output ranges minimum pulse width maximum pulse width resolution mcs = 1 mcs = 0 mcs = 1 mcs = 0 mcs = 1 mcs = 0 — 1/f x — 2 8 × 1/f x — 1/f x (200 ns) (51.2 µ s) (200 ns) 1/f x 2 × 1/f x 2 8 × ...

Page 119

96 chapter 6 8-bit timer/event counters 5 and 6 6.4.4 pwm output operations setting the 8-bit timer mode control registers 5 and 6 (tmc5 and tmc6) as shown in figure 6-13 allows operation as pwm output. Pulses with the duty ratio determined by the values preset in the 8-bit compare registers 50 and ...

Page 120

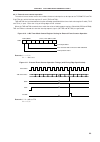

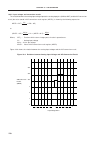

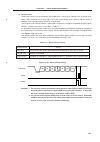

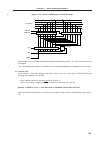

97 chapter 6 8-bit timer/event counters 5 and 6 figure 6-14. Pwm output operation timing (active high setting) remark n = 5, 6 figure 6-15. Pwm output operation timings (crn0 = 00h, active high setting) remark n = 5, 6 count clock tmn count value crn0 tcen inttmn ton 01 02 ff 00 01 02 n n+1 n+2 n+3 ...

Page 121

98 chapter 6 8-bit timer/event counters 5 and 6 figure 6-16. Pwm output operation timings (crn0 = ffh, active high setting) remark n = 5, 6 count clock tmn count value crn0 tcen inttmn ton 01 02 ff 00 01 02 ff 00 01 02 00 ovfn ff ff ff 00 inactive level inactive level active level inactive level act...

Page 122

99 chapter 6 8-bit timer/event counters 5 and 6 figure 6-17. Pwm output operation timings (crn0 changing, active high setting) caution if crn0 is changed during tmn operation, the value changed is not reflected until tmn overflows. Remark n = 5, 6 count clock tmn count value crn0 tcen inttmn ton ovf...

Page 123

100 chapter 6 8-bit timer/event counters 5 and 6 6.5 cautions on 8-bit timer/event counters 5 and 6 (1) timer start errors an error with a maximum of one clock may occur concerning the time required for a match signal to be gener- ated after timer start. This is because 8-bit timer registers 5 and 6...

Page 124

101 chapter 6 8-bit timer/event counters 5 and 6 count pulse cr50, cr60 tm5, tm6 count value x-1 x ffh 00h 01h 02h m n (3) operation after compare register change during timer count operation if the values after the 8-bit compare registers 50 and 60 (cr50 and cr60) are changed are smaller than those...

Page 125

102 chapter 6 8-bit timer/event counters 5 and 6 [memo].

Page 126

103 chapter 7 watchdog timer chapter 7 watchdog timer 7.1 watchdog timer functions the watchdog timer has the following functions. • watchdog timer • interval timer caution select the watchdog timer mode or the interval timer mode with the watchdog timer mode register (wdtm) (the watchdog timer and ...

Page 127

104 chapter 7 watchdog timer (2) interval timer mode interrupt requests are generated at the preset time intervals. Table 7-2. Interval times interval time mcs = 1 cs = 0 2 11 × 1/f xx 2 11 × 1/f x (410 µ s) 2 12 × 1/f x (819 µ s) 2 12 × 1/f xx 2 12 × 1/f x (819 µ s) 2 13 × 1/f x (1.64 ms) 2 13 × 1/...

Page 128

105 chapter 7 watchdog timer prescaler f xx 2 4 f xx 2 5 f xx 2 6 f xx 2 7 f xx 2 8 f xx 2 9 selector watchdog timer mode register internal bus internal bus tcl22 tcl21 tcl20 f xx /2 3 f xx 2 11 timer clock select register 2 3 wdtm4 wdtm3 8-bit counter tmmk4 run tmif4 intwdt maskable interrupt reque...

Page 129

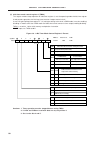

106 chapter 7 watchdog timer 7.3 watchdog timer control registers the following two types of registers are used to control the watchdog timer. • timer clock select register 2 (tcl2) • watchdog timer mode register (wdtm) (1) timer clock select register 2 (tcl2) this register sets the watchdog timer c...

Page 130

107 chapter 7 watchdog timer figure 7-2. Timer clock select register 2 format tcl27 7 tcl26 6 tcl25 0 4 0 3 2 1 0 ff42h address tcl2 symbol tcl22 tcl21 tcl20 5 00h after reset r/w r/w 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 tcl22 tcl21 tcl20 f xx /2 3 f xx /2 4 f xx /2 5 f xx /2 6 f xx /2 7 ...

Page 131

108 chapter 7 watchdog timer rum 7 0 6 0 wdtm4 4 wdtm3 3 2 1 0 fff9h address wdtm symbol 0 0 0 5 00h after reset r/w r/w run 0 1 watchdog timer operation mode selection note 3 count stop counter is cleared and counting starts. Wdtm3 × 0 1 watchdog timer operation mode selection note 1 interval timer...

Page 132

109 chapter 7 watchdog timer 7.4 watchdog timer operations 7.4.1 watchdog timer operation when bit 4 (wdtm4) of the watchdog timer mode register (wdtm) is set to 1, the watchdog timer is operated to detect any inadvertent program loop. The watchdog timer count clock (inadvertent program loop detecti...

Page 133

110 chapter 7 watchdog timer 7.4.2 interval timer operation the watchdog timer operates as an interval timer which generates interrupt requests repeatedly at an interval of the preset count value when bit 4 (wdtm4) of the watchdog timer mode register (wdtm) is set to 0. A count clock (interval time)...

Page 134

111 chapter 8 clock output control circuit cloe pcl/p35 pin output * * chapter 8 clock output control circuit 8.1 clock output control circuit functions the clock output control circuit is intended for carrier output during remote controlled transmission and clock output for supply to peripheral lsi...

Page 135

112 chapter 8 clock output control circuit 8.2 clock output control circuit configuration the clock output control circuit consists of the following hardware. Table 8-1. Clock output control circuit configuration item configuration timer clock select register 0 (tcl0) port mode register 3 (pm3) figu...

Page 136

113 chapter 8 clock output control circuit 8.3 clock output function control registers the following two types of registers are used to control the clock output function. • timer clock select register 0 (tcl0) • port mode register 3 (pm3) (1) timer clock select register 0 (tcl0) this register sets p...

Page 137

114 chapter 8 clock output control circuit pm37 7 pm36 6 pm35 pm34 4 pm33 3 2 1 0 ff23h address pm3 symbol pm32 pm31 pm30 5 ffh after reset r/w r/w pm3n 0 1 p3n pin input/output mode selection (n=0 to 7) output mode (output buffer on) input mode (output buffer off) (2) port mode register 3 (pm3) thi...

Page 138

115 chapter 9 buzzer output control circuit internal bus f xx /2 9 f xx /2 10 f xx /2 11 tcl27 tcl26 tcl25 3 pm36 selector timer clock select register 2 port mode register 3 buz/p36 p36 output latch chapter 9 buzzer output control circuit 9.1 buzzer output control circuit functions the buzzer output...

Page 139

116 chapter 9 buzzer output control circuit 9.3 buzzer output function control registers the following two types of registers are used to control the buzzer output function. • timer clock select register 2 (tcl2) • port mode register 3 (pm3) (1) timer clock select register 2 (tcl2) this register set...

Page 140

117 chapter 9 buzzer output control circuit figure 9-2. Timer clock select register 2 format tcl27 7 tcl26 6 tcl25 0 4 0 3 2 1 0 ff42h address tcl2 symbol tcl22 tcl21 tcl20 5 00h after reset r/w r/w 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 tcl22 tcl21 tcl20 f xx /2 3 f xx /2 4 f xx /2 5 f xx ...

Page 141

118 chapter 9 buzzer output control circuit pm37 7 pm36 6 pm35 pm34 4 pm33 3 2 1 0 ff23h address pm3 symbol pm32 pm31 pm30 5 ffh after reset r/w r/w pm3n 0 1 p3n pin input/output mode selection (n=0 to 7) output mode (output buffer on) input mode (output buffer off) (2) port mode register 3 (pm3) th...

Page 142

119 chapter 10 a/d converter chapter 10 a/d converter 10.1 a/d converter functions the a/d converter converts an analog input into a digital value. It consists of 8 channels (ani0 to ani7) with an 8-bit resolution. The conversion method is based on successive approximation and the conversion result ...

Page 143

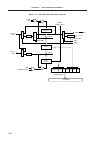

120 chapter 10 a/d converter figure 10-1. A/d converter block diagram notes 1. Selector to select the number of channels to be used for analog input. 2. Selector to select the channel for a/d conversion. 3. External interrupt mode register 1 (intm1) bits 0 and 1. Ani0/p10 ani1/p11 ani2/p12 ani3/p13 ...

Page 144

121 chapter 10 a/d converter (1) successive approximation register (sar) this register compares the analog input voltage value to the voltage tap (compare voltage) value applied from the series resistor string and holds the result from the most significant bit (msb). When held to the least significa...

Page 145

122 chapter 10 a/d converter 10.3 a/d converter control registers the following three types of registers are used to control the a/d converter. • a/d converter mode register (adm) • a/d converter input select register (adis) • external interrupt mode register 1 (intm1) (1) a/d converter mode registe...

Page 146

123 chapter 10 a/d converter figure 10-2. A/d converter mode register format notes 1. Set so that the a/d conversion time is 19.1 µ s or more. 2. Setting prohibited because a/d conversion time is less than 19.1 µ s. Cautions 1. The following sequence is recommended for power consumption reduction of...

Page 147

124 chapter 10 a/d converter (2) a/d converter input select register (adis) this register determines whether the ani0/p10 to ani7/p17 pins should be used for analog input channels or ports. Pins other than those selected as analog input can be used as input/output ports. Adis is set with an 8-bit me...

Page 148

125 chapter 10 a/d converter (3) external interrupt mode register 1 (intm1) this register sets the valid edge for intp3. Intm1 is set with an 8-bit memory manipulation instruction. Reset input sets intm1 to 00h. Figure 10-4. External interrupt mode register 1 format 0 7 0 6 0 0 4 0 3 2 1 0 ffedh add...

Page 149

126 chapter 10 a/d converter 10.4 a/d converter operations 10.4.1 basic operations of a/d converter (1) set the number of analog input channels with a/d converter input select register (adis). (2) from among the analog input channels set with adis, select one channel for a/d conversion with a/d conv...

Page 150

127 chapter 10 a/d converter sar adcr intad a/d converter operation sampling time sampling a /d conversion conversion time undefined 80h c0h or 40h conversion result conversion result figure 10-5. A/d converter basic operation a/d conversion operations are performed continuously until bit 7 (cs) of ...

Page 151

128 chapter 10 a/d converter 10.4.2 input voltage and conversion results the relation between the analog input voltage input to the analog input pins (ani0 to ani7) and the a/d conversion result (the value stored in a/d conversion result register (adcr)) is shown by the following expression. Adcr = ...

Page 152

129 chapter 10 a/d converter adm rewrite cs=1, trg=1 standby state anin intp3 a /d conversion adcr intad anin anin anin anim anim anin anin standby state standby state adm rewrite cs=1, trg=1 anim anim anim 10.4.3 a/d converter operating mode using the a/d converter input select register (adis) and ...

Page 153

130 chapter 10 a/d converter conversion start cs=1, trg=0 a /d conversion adcr intad anin anin anim anin anim anim anin anin adm rewrite cs=1, trg=0 adm rewrite cs=0, trg=0 conversion suspended conversion results are not stored stop (2) a/d conversion operation in software start when bit 6 (trg) and...

Page 154

131 chapter 10 a/d converter 10.5 a/d converter cautions (1) power consumption in standby mode the a/d converter operates on the main system clock. Therefore, its operation stops in stop mode. As a current still flows in the av ref pin at this time, this current must be cut in order to minimize the ...

Page 155

132 chapter 10 a/d converter (3) noise countermeasures in order to maintain 8-bit resolution, attention must be paid to noise on pins av ref and ani0 to ani7. Since the effect increases in proportion to the output impedance of the analog input source, it is recommended that a capacitor be connected ...

Page 156

133 chapter 10 a/d converter a /d conversion adcr intad anin anin anim anim anin anin anim anim adm rewrite (start of anin conversion) adm rewrite (start of anim conversion) adif is set but anim conversion has not ended (6) interrupt request flag (adif) the interrupt request flag (adif) is not clear...

Page 157

134 chapter 10 a/d converter [memo].

Page 158

135 chapter 11 serial interface channel 2 chapter 11 serial interface channel 2 11.1 serial interface channel 2 functions serial interface channel 2 has the following three modes. • operation stop mode • asynchronous serial interface (uart) mode • 3-wire serial i/o mode (1) operation stop mode this ...

Page 159

136 chapter 11 serial interface channel 2 11.2 serial interface channel 2 configuration serial interface channel 2 consists of the following hardware. Table 11-1. Serial interface channel 2 configuration item configuration register transmit shift register (txs) receive shift register (rxs) receive b...

Page 160

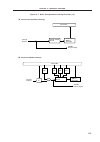

137 chapter 11 serial interface channel 2 internal bus asynchronous serial interface mode register asynchronous serial interface status register receive buffer register (rxb/sio2) direction control circuit receive shift register (rxs) reception control circuit rxd/si2/ p70 txd/so2/ p71 intsr/intcsi2...

Page 161

138 chapter 11 serial interface channel 2 tps3 tps2 tps1 tps0 internal bus mdl3 mdl2 mdl1 mdl0 baud rate generator control register 4 txe csie2 5-bit counter selector selector decoder 1/2 selector transmit clock 1/2 selector receive clock match match mdl0-mdl3 5-bit counter rxe start bit detection s...

Page 162

139 chapter 11 serial interface channel 2 (1) transmit shift register (txs) this register is used to set the transmit data. The data written in txs is transmitted as serial data. If the data length is specified as 7 bits, bits 0 to 6 of the data written in txs are transferred as transmit data. Writi...

Page 163

140 chapter 11 serial interface channel 2 11.3 serial interface channel 2 control registers serial interface channel 2 is controlled by the following four registers. • serial operating mode register 2 (csim2) • asynchronous serial interface mode register (asim) • asynchronous serial interface status...

Page 164

141 chapter 11 serial interface channel 2 6 5 4 3 2 1 0 7 symbol asim txe rxe ps1 ps0 cl sl isrm sck ff70h 00h r/w address after reset r/w sck 0 1 clock selection in asynchronous serial interface mode input clock from off-chip to asck pin dedicated baud rate generator output note isrm 0 1 control of...

Page 165

142 chapter 11 serial interface channel 2 table 11-2. Serial interface channel 2 operating mode settings (1) operation stop mode (2) 3-wire serial i/o mode (3) asynchronous serial interface mode notes 1. Can be used freely as port function. 2. Can be used as p70 (cmos input/output) when only transmi...

Page 166

143 chapter 11 serial interface channel 2 pe 6 5 4 3 2 1 0 7 symbol asis 0 0 0 0 0 fe ove ff71h 00h r address after reset r/w ove 0 1 overrun error flag overrun error not generated overrun error generated note 1 (when next receive operation is completed before data from receive buffer register is re...

Page 167

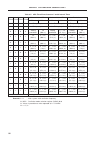

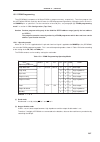

144 chapter 11 serial interface channel 2 baud rate generator input clock selection mdl3 mdl2 mdl1 mdl0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 f sck /16 f sck /17 f sck /18 f sck /19 f sck /20 f sck /21 f sck /2...

Page 168

145 chapter 11 serial interface channel 2 figure 11-6. Baud rate generator control register format (2/2) 5-bit counter source clock selection tps3 tps2 tps1 tps0 n mcs=1 mcs=0 0 0 0 0 f xx /2 10 f xx /2 10 (4.9 khz) f x /2 11 (2.4 khz) 11 0 1 0 1 f xx f x (5.0 mhz) f x /2 (2.5 mhz) 1 0 1 1 0 f xx /2...

Page 169

146 chapter 11 serial interface channel 2 the baud rate transmit/receive clock generated is either a signal scaled from the main system clock, or a signal scaled from the clock input from the asck pin. (a) generation of baud rate transmit/receive clock by means of main system clock the transmit/rece...

Page 170

147 chapter 11 serial interface channel 2 (b) generation of baud rate transmit/receive clock by means of external clock from asck pin the transmit/receive clock is generated by scaling the clock input from the asck pin. The baud rate generated from the clock input from the asck pin is obtained with ...

Page 171

148 chapter 11 serial interface channel 2 11.4 serial interface channel 2 operation serial interface channel 2 has the following three modes. • operation stop mode • asynchronous serial interface (uart) mode • 3-wire serial i/o mode 11.4.1 operation stop mode in the operation stop mode, serial trans...

Page 172

149 chapter 11 serial interface channel 2 sl 6 5 4 3 2 1 0 7 symbol asim txe rxe ps1 ps0 cl isrm sck ff70h 00h r/w address after reset r/w rxe 0 1 receive operation control receive operation stopped receive operation enabled txe 0 1 transmit operation control transmit operation stopped transmit oper...

Page 173

150 chapter 11 serial interface channel 2 6 5 4 3 2 1 0 7 symbol csim2 csie2 0 0 0 0 csim 22 csck 0 csck 0 1 clock selection in 3-wire serial i/o mode input clock from off-chip to sck2 pin dedicated baud rate generator output csim22 0 1 first bit specification msb lsb csie2 0 1 operation control in ...

Page 174

151 chapter 11 serial interface channel 2 note when sck is set to 1 and the baud rate generator output is selected, the asck pin can be used as an input/output port. Caution the serial transmit/receive operation must be stopped before changing the operating mode. (b) asynchronous serial interface mo...

Page 175

152 chapter 11 serial interface channel 2 pe 6 5 4 3 2 1 0 7 symbol asis 0 0 0 0 0 fe ove ff71h 00h r address after reset r/w ove 0 1 overrun error flag overrun error not generated overrun error generated note 1 (when next receive operation is completed before data from receive buffer register is re...

Page 176

153 chapter 11 serial interface channel 2 baud rate generator input clock selection mdl3 mdl2 mdl1 mdl0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 f sck /16 f sck /17 f sck /18 f sck /19 f sck /20 f sck /21 f sck /22 f sck ...

Page 177

154 chapter 11 serial interface channel 2 5-bit counter source clock selection tps3 tps2 tps1 tps0 n mcs=1 mcs=0 0 0 0 0 f xx /2 10 f x /2 10 (4.9 khz) f x /2 11 (2.4 khz) 11 0 1 0 1 f xx f x (5.0 mhz) f x /2 (2.5 mhz) 1 0 1 1 0 f xx /2 f x /2 (2.5 mhz) f x /2 2 (1.25 mhz) 2 0 1 1 1 f xx /2 2 f x /2...

Page 178

155 chapter 11 serial interface channel 2 the baud rate transmit/receive clock generated is either a signal scaled from the main system clock, or a signal scaled from the clock input from the asck pin. (i) generation of baud rate transmit/receive clock by means of main system clock the transmit/rece...

Page 179

156 chapter 11 serial interface channel 2 (ii) generation of baud rate transmit/receive clock by means of external clock from asck pin the transmit/receive clock is generated by scaling the clock input from the asck pin. The baud rate generated from the clock input from the asck pin is obtained with...

Page 180

157 chapter 11 serial interface channel 2 (2) communication operation (a) data format the transmit/receive data format is as shown in figure 11-7. Figure 11-7. Asynchronous serial interface transmit/receive data format 1 data frame is configured from the following bits. • start bits ...................

Page 181

158 chapter 11 serial interface channel 2 (b) parity types and operation the parity bit is used to detect a bit error in the communication data. Normally, the same kind of parity bit is used on the transmitting side and the receiving side. With even parity and odd parity, a one-bit (odd number) erro...

Page 182

159 chapter 11 serial interface channel 2 d1 d2 d6 d7 parity d0 txd (output) intst stop start d1 d2 d6 d7 parity d0 txd (output) intst stop start (c) transmission a transmit operation is started by writing transmit data to the transmit shift register (txs). The start bit, parity bit and stop bit(s) ...

Page 183

160 chapter 11 serial interface channel 2 d1 d2 d6 d7 parity d0 rxd (input) intsr stop start (d) reception when the rxe bit of the asynchronous serial interface mode register (asim) is set (1), a receive operation is enabled and sampling of the rxd pin input is performed. Rxd pin input sampling is p...

Page 184

161 chapter 11 serial interface channel 2 (e) receive errors three kinds of errors can occur during a receive operation: a parity error, framing error, or overrun error. When a data reception results error flag is set in the asynchronous serial interface register (asis), a reception error interrupt ...

Page 185

162 chapter 11 serial interface channel 2 (3) uart mode cautions (a) in cases where bit 7 (txe) of the asynchronous serial interface moderegister (asim) has been cleared and a transmit operation has been terminated during transmission, be sure to set 1 in txe after setting ffh in the transmit shift ...

Page 186

163 chapter 11 serial interface channel 2 11.4.3 3-wire serial i/o mode the 3-wire serial i/o mode is useful for connection of peripheral i/os and display controllers, etc., which incorporate a conventional synchronous clocked serial interface, such as the 75x/xl series, 78k series, 17k series, etc....

Page 187

164 chapter 11 serial interface channel 2 (b) asynchronous serial interface mode register (asim) asim is set with a 1-bit or 8-bit memory manipulation instruction. Reset input sets asim to 00h. When the 3-wire serial i/o mode is selected, 00h should be set in asim. 6 5 4 3 2 1 0 7 symbol asim txe rx...

Page 188

165 chapter 11 serial interface channel 2 baud rate generator input clock selection mdl3 mdl2 mdl1 mdl0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 f sck /16 f sck /17 f sck /18 f sck /19 f sck /20 f sck /21 f sck /2...

Page 189

166 chapter 11 serial interface channel 2 5-bit counter source clock selection tps3 tps2 tps1 tps0 n mcs=1 mcs=0 0 0 0 0 f xx /2 10 f x /2 10 (4.9 khz) f x /2 11 (2.4 khz) 11 0 1 0 1 f xx f x (5.0 mhz) f x /2 (2.5 mhz) 1 0 1 1 0 f xx /2 f x /2 (2.5 mhz) f x /2 2 (1.25 mhz) 2 0 1 1 1 f xx /2 2 f x /2...

Page 190

167 chapter 11 serial interface channel 2 when the internal clock is used as the serial clock in the 3-wire serial i/o mode, set brgc as described below. Brgc setting is not required if an external serial clock is used. (i) when the baud rate generator is not used: select a serial clock frequency wi...

Page 191

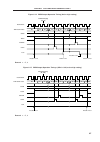

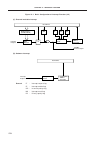

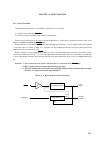

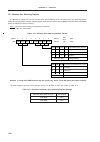

168 chapter 11 serial interface channel 2 si2 sck2 1 2 3 4 5 6 7 8 di7 di6 di5 di4 di3 di2 di1 di0 so2 do7 do6 do5 do4 do3 do2 do1 do0 srif transfer start at the falling edge of sck2 end of transfer (2) communication operation in the 3-wire serial i/o mode, data transmission/reception is performed i...

Page 192

169 chapter 11 serial interface channel 2 figure 11-13. Circuit of switching in transfer bit order start bit switching is realized by switching the bit order for data write to sio2. The sio2 shift order remains unchanged. Thus, switching between msb-first and lsb-first must be performed before writi...

Page 193

170 chapter 11 serial interface channel 2 [memo].

Page 194

171 chapter 12 interrupt function chapter 12 interrupt function 12.1 interrupt function types the following three types of interrupt functions are used. (1) non-maskable interrupt this interrupt is acknowledged unconditionally even in the interrupt disabled status. It does not undergo interrupt prio...

Page 195

172 chapter 12 interrupt function 12.2 interrupt sources and configuration there are a total of 13 interrupts, combining non-maskable interrupts, maskable interrupts and software interrupts (see table 12-1). Table 12-1. Interrupt source list interrupt source name trigger non- — intwdt watchdog timer...

Page 196

173 chapter 12 interrupt function internal bus ie pr isp mk if interrupt request priority control circuit vector table address generator standby release signal internal bus priority control circuit vector table address generator standby release signal interrupt request figure 12-1. Basic configurati...

Page 197

174 chapter 12 interrupt function internal bus priority control circuit vector table address generator interrupt request external interrupt mode register (intm0, intm1) edge detector interrupt request ie pr isp mk if priority control circuit vector table address generator standby release signal inte...

Page 198

175 chapter 12 interrupt function 12.3 interrupt function control registers the following five types of registers are used to control the interrupt functions. • interrupt request flag register (if0l, if0h, if1l) • interrupt mask flag register (mk0l, mk0h, mk1l) • priority specify flag register (pr0l...

Page 199

176 chapter 12 interrupt function cautions 1. Tmif4 flag is r/w enabled only when a watchdog timer is used as an interval timer. If a watchdog timer is used in watchdog timer mode 1, set tmif4 flag to 0. 2. Set 0 to the bits 1, 5 to 7 of if0l and bits 0, 1, 5 to 7 of if0h and if1l. (1) interrupt req...

Page 200

177 chapter 12 interrupt function cautions 1. If tmmk4 flag is read when a watchdog timer is used in watchdog timer mode 1, mk0 value becomes undefined. 2. Because port 0 has a dual function as the external interrupt request input, when the output level is changed by specifying the output mode of th...

Page 201

178 chapter 12 interrupt function cautions 1. If a watchdog timer is used in watchdog timer mode 1, set tmpr4 flag to 1. 2. Set 1 to the bits 1, 5 to 7 of pr0l and bits 0, 1, 5 to 7 of pr0h and pr1l. (3) priority specify flag registers (pr0l, pr0h, and pr1l) the priority specify flag is used to set ...

Page 202

179 chapter 12 interrupt function (4) external interrupt mode register (intm0, intm1) these registers set the valid edge for intp1 to intp3. Intm0 and intm1 are set by 8-bit memory manipulation instructions. Reset input sets these registers to 00h. Figure 12-5. External interrupt mode register 0 for...

Page 203

180 chapter 12 interrupt function (5) program status word (psw) the program status word is a register to hold the instruction execution result and the current status for interrupt request. The ie flag to set maskable interrupt enable/disable and the isp flag to control multiple interrupt processing ...

Page 204

181 chapter 12 interrupt function 12.4 interrupt servicing operations 12.4.1 non-maskable interrupt request acknowledge operation a non-maskable interrupt request is unconditionally acknowledged even if in an interrupt request acknowledge disable state. It does not undergo interrupt priority control...

Page 205

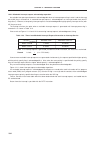

182 chapter 12 interrupt function wdtm4=1 (with watchdog timer mode selected)? Overflow in wdt? Wdtm3=0 (with non-maskable interrupt selected)? Interrupt request generation wdt interrupt servicing? Interrupt control register unaccessed? Interrupt service start interrupt request held pending reset pr...

Page 206

183 chapter 12 interrupt function figure 12-10. Non-maskable interrupt request acknowledge operation (a) if a new non-maskable interrupt request is generated during non-maskable interrupt servicing program execution (b) if two non-maskable interrupt requests are generated during non-maskable interru...

Page 207

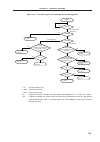

184 chapter 12 interrupt function 12.4.2 maskable interrupt request acknowledge operation a maskable interrupt request becomes acknowledgeable when an interrupt request flag is set to 1 and the interrupt mask (mk) flag is cleared to 0. A vectored interrupt request is acknowledged in an interrupt ena...

Page 208

185 chapter 12 interrupt function figure 12-11. Interrupt request acknowledge processing algorithm start × × if=1? × × mk=0? × × pr=0? Any simultaneously generated ×× pr=0 interrupt requests? Any simultaneously generated high-priority interrupt requests? Ie=1? Isp=1? Vectored interrupt servicing int...

Page 209

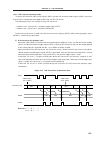

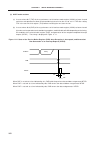

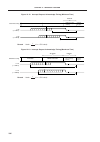

186 chapter 12 interrupt function figure 12-12. Interrupt request acknowledge timing (minimum time) remark 1 clock : (f cpu : cpu clock) figure 12-13. Interrupt request acknowledge timing (maximum time) remark 1 clock : (f cpu : cpu clock) f cpu 1 f cpu 1 instruction instruction psw and pc save, jum...

Page 210

187 chapter 12 interrupt function 12.4.3 software interrupt request acknowledge operation a software interrupt request is acknowledged by brk instruction execution. Software interrupt cannot be disabled. If a software interrupt request is acknowledged, the contents are saved to the stack in the orde...

Page 211

188 chapter 12 interrupt function table 12-4. Interrupt request enabled for multiple interrupt during interrupt servicing maskable interrupt request pr=0 pr=1 ie=1 ie=0 ie=1 ie=0 non-maskable interrupt d d d d d maskable interrupt isp=0 e e d d d isp=1 e e d e d software interrupt e e d e d remarks ...

Page 212

189 chapter 12 interrupt function main processing intxx servicing intyy servicing intxx (pr=0) 1 instruction execution ie=0 intyy (pr=1) ei ie=0 ei reti reti main processing ei intxx (pr=1) intyy (pr=0) ie=0 ei reti intxx servicing intzz (pr=0) ie=0 ei reti intyy servicing ie=0 reti intzz servicing ...

Page 213

190 chapter 12 interrupt function main processing intxx servicing intyy servicing intxx (pr=0) 1 instruction execution ie=0 intyy (pr=0) ie=0 reti reti ei figure 12-14 multiple interrupt example (2/2) example 3. Example of when a multiple interrupt is not generated because interrupts are not enabled...

Page 214

191 chapter 12 interrupt function 12.4.5 interrupt request reserve there are some instructions which, though an interrupt request may be generated while they are being executed, will reserve the acknowledgment of the request until after execution of the next instruction. These instructions (interrup...

Page 215

192 chapter 12 interrupt function the interrupt request reserve timing is shown in figure 12-15. Figure 12-15. Interrupt request hold remarks 1. Instruction n: instruction that holds interrupts requests 2. Instruction m: instructions other than instruction n 3. The operation of ×× if (interrupt requ...

Page 216

193 chapter 13 standby function chapter 13 standby function 13.1 standby function and configuration 13.1.1 standby function the standby function is designed to decrease power consumption of the system. The following two modes are available. (1) halt mode halt instruction execution sets the halt mode...

Page 217

194 chapter 13 standby function address fffah 04h after reset r/w r/w 0 0 0 0 1 selection of oscillation stabilization time when stop mode is released 2 12 /f xx 2 14 /f xx 2 15 /f xx 2 16 /f xx 2 17 /f xx osts2 7 0 symbol osts 6 0 5 0 4 0 3 0 2 osts2 1 osts1 0 osts0 0 0 1 1 0 other than above osts1...

Page 218

195 chapter 13 standby function 13.2 standby function operations 13.2.1 halt mode (1) halt mode set and operating status the halt mode is set by executing the halt instruction. The operating status in the halt mode is described below. Table 13-1. Halt mode operating status item halt mode operating s...

Page 219

196 chapter 13 standby function halt instruction wait standby release signal operating mode clock halt mode wait oscillation operating mode (2) halt mode clear the halt mode can be cleared with the following three types of sources. (a) clear upon unmasked interrupt request an unmasked interrupt requ...

Page 220

197 chapter 13 standby function (c) clear upon reset input as is the case with normal reset operation, a program is executed after branch to the reset vector address. Figure 13-3. Halt mode release by reset input remarks 1. F x : main system clock oscillation frequency 2. Values in parentheses when ...

Page 221

198 chapter 13 standby function 13.2.2 stop mode (1) stop mode set and operating status the stop mode is set by executing the stop instruction. Cautions 1. When the stop mode is set, the x2 pin is internally connected to v dd via a pull-up resistor to minimize the leakage current at the crystal osci...

Page 222

199 chapter 13 standby function stop instruction wait (time set by osts) oscillation stabilization wait status operating mode oscillation operationg mode stop mode oscillation stop oscillation standby release signal clock (2) stop mode release the stop mode can be cleared with the following two type...

Page 223

200 chapter 13 standby function reset signal operating mode clock reset period stop mode oscillation stop oscillation stabilization wait status operating mode oscillation wait (2 17 /f x : 26.2 ms) stop instruction oscillation (b) release by reset input the stop mode is cleared and after the lapse o...

Page 224

201 chapter 14 reset function reset count clock reset control circuit watchdog timer stop over- flow reset signal interrupt function chapter 14 reset function 14.1 reset function the following two operations are available to generate the reset signal. (1) external reset input with reset pin (2) inte...

Page 225

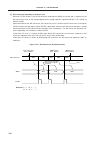

202 chapter 14 reset function reset internal reset signal port pin delay delay hi-z x1 normal operation reset period (oscillation stop) oscillation stabilization time wait normal operation (reset processing) stop status (oscillation stop) stop instruction execution reset internal reset signal port p...

Page 226

203 chapter 14 reset function table 14-1. Hardware status after reset (1/2) hardware status after reset program counter (pc) note1 the contents of reset vector tables (0000h and 0001h) are set. Stack pointer (sp) undefined program status word (psw) 02h data memory undefined note2 general register un...

Page 227

204 chapter 14 reset function table 14-1. Hardware status after reset (2/2) hardware status after reset interrupt request flag register (if0l, if0h, if1l) 00h mask flag register (mk0l, mk0h, mk1l) ffh priority specify flag register (pr0l, pr0h, pr1l) ffh external interrupt mode register (intm0, intm...

Page 228

205 chapter 15 µ pd78p083 chapter 15 µ pd78p083 the µ pd78p083 is a single-chip microcontroller with an on-chip one-time prom or with an on-chip eprom which has program write, erasure and rewrite capability. Differences between the µ pd78p083 and mask rom versions are shown in table 15-1. Table 15-1...

Page 229

206 chapter 15 µ pd78p083 caution if using mask rom versions, do not specify any values in the ims other than when resetting. The ims settings to give the same memory map as mask rom versions are shown in table 15-2. Table 15-2. Examples of memory size switching register settings relevant mask rom v...

Page 230

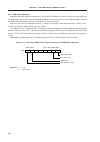

207 chapter 15 µ pd78p083 reset v pp v dd ce oe pgm d0-d7 15.2 prom programming the µ pd78p083 incorporate a 24-kbyte prom as program memory, respectively. To write a program into the µ pd78p083 prom, make the device enter the prom programming mode by setting the levels of the v pp and reset pins as...

Page 231

208 chapter 15 µ pd78p083 (3) standby mode setting ce to h sets the standby mode. In this mode, data output becomes high impedance irrespective of the status of oe. (4) page data latch mode setting ce to h, pgm to h, and oe to l at the start of the page write mode sets the page data latch mode. In t...

Page 232

209 chapter 15 µ pd78p083 15.2.2 prom write procedure figure 15-2. Page program mode flowchart start address = g v dd = 6.5 v, v pp = 12.5 v x = 0 latch address = address + 1 latch address = address + 1 latch address = address + 1 latch x = x + 1 0.1-ms program pulse verify 4 bytes pass address = n?...

Page 233

210 chapter 15 µ pd78p083 figure 15-3. Page program mode timing page data latch page program program verify data input data output a2-a14 a0, a1 d0-d7 v pp v dd v pp v dd +1.5 v dd v dd v ih ce pgm oe v il v ih v il v ih v il.

Page 234

211 chapter 15 µ pd78p083 figure 15-4. Byte program mode flowchart start address = g v dd = 6.5 v, v pp = 12.5 v x = 0 x = x + 1 0.1-ms program pulse verify address = n? V dd = 4.5 to 5.5 v, v pp = v dd all bytes verified? End of write fail fail pass yes all pass no pass defective product no yes x =...

Page 235

212 chapter 15 µ pd78p083 figure 15-5. Byte program mode timing cautions 1. Be sure to apply v dd before applying v pp , and remove it after removing v pp . 2. V pp must not exceed +13.5 v including overshoot voltage. 3. Disconnecting/inserting the device from/to the on-board socket while +12.5 v is...

Page 236

213 chapter 15 µ pd78p083 15.2.3 prom reading procedure prom contents can be read onto the external data bus (d0 to d7) using the following procedure. (1) fix the reset pin low, and supply +5 v to the v pp pin. Unused pins are handled as shown in paragraph, (2) “prom programming mode” in section 1.5...

Page 237

214 chapter 15 µ pd78p083 15.3 erasure procedure ( µ pd78p083du only) with the µ pd78p083du, it is possible to erase ( or set all contents to ffh) the data contents written in the program memory, and rewrite the memory. The data can be erased by exposing the window to light with a wavelength of appr...

Page 238

215 chapter 16 instruction set chapter 16 instruction set this chapter describes each instruction set of the µ pd78083 subseries as list table. For details of its operation and operation code, refer to the separate document “78k/0 series user’s manual—instruction (ieu-1372).”.

Page 239

216 chapter 16 instruction set 16.1 legends used in operation list 16.1.1 operand identifiers and description methods operands are described in “operand” column of each instruction in accordance with the description method of the instruction operand identifier (refer to the assembler specifications ...

Page 240

217 chapter 16 instruction set 16.1.2 description of “operation” column a : a register; 8-bit accumulator x : x register b : b register c : c register d : d register e : e register h : h register l : l register ax : ax register pair; 16-bit accumulator bc : bc register pair de : de register pair hl ...

Page 241

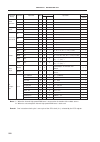

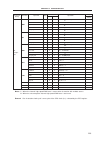

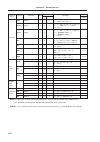

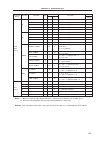

218 chapter 16 instruction set 16.2 operation list clock flag note 1 note 2 z ac cy r, #byte 2 4 – r ← byte saddr, #byte 3 6 7 (saddr) ← byte sfr, #byte 3 – 7 sfr ← byte a, r note 3 1 2 – a ← r r, a note 3 1 2 – r ← a a, saddr 2 4 5 a ← (saddr) saddr, a 2 4 5 (saddr) ← a a, sfr 2 – 5 a ← sfr sfr, a ...

Page 242

219 chapter 16 instruction set clock flag note 1 note 2 z ac cy rp, #word 3 6 – rp ← word saddrp, #word 4 8 10 (saddrp) ← word sfrp, #word 4 – 10 sfrp ← word ax, saddrp 2 6 8 ax ← (saddrp) saddrp, ax 2 6 8 (saddrp) ← ax movw ax, sfrp 2 – 8 ax ← sfrp sfrp, ax 2 – 8 sfrp ← ax ax, rp note 3 1 4 – ax ← ...

Page 243

220 chapter 16 instruction set clock flag note 1 note 2 z ac cy a, #byte 2 4 – a, cy ← a – byte × × × saddr, #byte 3 6 8 (saddr), cy ← (saddr) – byte × × × a, r note 3 2 4 – a, cy ← a – r × × × r, a 2 4 – r, cy ← r – a × × × a, saddr 2 4 5 a, cy ← a – (saddr) × × × a, !Addr16 3 8 9 a, cy ← a – (addr...

Page 244

221 chapter 16 instruction set clock flag note 1 note 2 z ac cy a, #byte 2 4 – a ← a byte × saddr, #byte 3 6 8 (saddr) ← (saddr) byte × a, r note 3 2 4 – a ← a r × r, a 2 4 – r ← r a × a, saddr 2 4 5 a ← a (saddr) × a, !Addr16 3 8 9 a ← a (addr16) × a, [hl] 1 4 5 a ← a (hl) × a, [hl + byte] 2 8 9 a ...

Page 245

222 chapter 16 instruction set clock flag note 1 note 2 z ac cy addw ax, #word 3 6 – ax, cy ← ax + word × × × subw ax, #word 3 6 – ax, cy ← ax – word × × × cmpw ax, #word 3 6 – ax – word × × × mulu x 2 16 – ax ← a × x divuw c 2 25 – ax (quotient), c (remainder) ← ax ÷ c r 1 2 – r ← r + 1 × × saddr 2...

Page 246

223 chapter 16 instruction set clock flag note 1 note 2 z ac cy cy, saddr.Bit 3 6 7 cy ← cy (saddr.Bit) × cy, sfr.Bit 3 – 7 cy ← cy sfr.Bit × and1 cy, a.Bit 2 4 – cy ← cy a.Bit × cy, psw.Bit 3 – 7 cy ← cy psw.Bit × cy, [hl].Bit 2 6 7 cy ← cy (hl).Bit × cy, saddr.Bit 3 6 7 cy ← cy (saddr.Bit) × cy, s...

Page 247

224 chapter 16 instruction set clock flag note 1 note 2 z ac cy (sp – 1) ← (pc + 3) h , (sp – 2) ← (pc + 3) l , pc ← addr16, sp ← sp – 2 (sp – 1) ← (pc + 2) h , (sp – 2) ← (pc + 2) l , callf !Addr11 2 5 – pc 15 – 11 ← 00001, pc 10 – 0 ← addr11, sp ← sp – 2 (sp – 1) ← (pc + 1) h , (sp – 2) ← (pc + 1)...

Page 248

225 chapter 16 instruction set clock flag note 1 note 2 z ac cy saddr.Bit, $addr16 3 8 9 pc ← pc + 3 + jdisp8 if(saddr.Bit) = 1 sfr.Bit, $addr16 4 – 11 pc ← pc + 4 + jdisp8 if sfr.Bit = 1 bt a.Bit, $addr16 3 8 – pc ← pc + 3 + jdisp8 if a.Bit = 1 psw.Bit, $addr16 3 – 9 pc ← pc + 3 + jdisp8 if psw.Bit...

Page 249

226 chapter 16 instruction set 16.3 instructions listed by addressing type (1) 8-bit instructions mov, xch, add, addc, sub, subc, and, or, xor, cmp, mulu, divuw, inc, dec, ror, rol, rorc, rolc, ror4, rol4, push, pop, dbnz.

Page 250

227 chapter 16 instruction set second operand [hl + byte] #byte a r note sfr saddr !Addr16 psw [de] [hl] [hl + b] $addr16 1 none first operand [hl + c] a add mov mov mov mov mov mov mov mov ror addc xch xch xch xch xch xch xch rol sub add add add add add rorc subc addc addc addc addc addc rolc and s...

Page 251

228 chapter 16 instruction set (2) 16-bit instructions movw, xchw, addw, subw, cmpw, push, pop, incw, decw second operand first operand ax addw movw movw movw movw movw subw xchw cmpw rp movw movw note incw decw push pop sfrp movw movw saddrp movw movw !Addr16 movw sp movw movw note only when rp = b...

Page 252

229 chapter 16 instruction set ax !Addr16 !Addr11 [addr5] $addr16 (4) call/instructions/branch instructions call, callf, callt, br, bc, bnc, bz, bnz, bt, bf, btclr, dbnz second operand first operand basic instruction br call callf callt br br bc bnc bz bnz compound bt instruction bf btclr dbnz (5) o...

Page 253

230 chapter 16 instruction set [memo].

Page 254