- DL manuals

- Rabbit

- Microcontrollers

- 2000

- User Manual

Rabbit 2000 User Manual - 7. M

User’s Manual

71

7. M

ISCELLANEOUS

I/O F

UNCTIONS

7.1 Processor Identification

Two read-only registers are provided to allow software to identify the Rabbit microproces-

sor and recognize the features and capabilities of the chip. Five bits in each of these regis-

ters are unique to each version of the chip. One register (GCPU) identifies the CPU, and

the other register (GREV) is reserved for revision identification. The CPU identification

(GCPU) of all revisions of the Rabbit 2000 microprocessor is the same. Rabbit 2000 revi-

sions are differentiated by the value in the GREV register. Refer to Section B.2.2 for more

information.

Summary of 2000

Page 1

Rabbit 2000 ® microprocessor user’s manual 019–0069 • 041018–m ®.

Page 2

Rabbit 2000 microprocessor rabbit semiconductor 2932 spafford street davis, california 95616-6800 usa telephone: (530) 757-8400 fax: (530) 757-8402 www.Rabbitsemiconductor.Com rabbit 2000 microprocessor user’s manual part number 019-0069 • 041018–m • printed in u.S.A. ©1999–2004 rabbit semiconductor...

Page 3: Able

User’s manual t able of c ontents chapter 1. Introduction 1 1.1 features and specifications ..................................................................................................................1 1.2 summary of rabbit advantages ..............................................................

Page 4

Rabbit 2000 microprocessor chapter 4. Rabbit capabilities 41 4.1 precisely timed output pulses .......................................................................................................... 41 4.1.1 pulse width modulation to reduce relay power ...............................................

Page 5

User’s manual chapter 11. Timers 111 11.1 timer a...........................................................................................................................................112 11.1.1 timer a i/o registers ..................................................................................

Page 6

Rabbit 2000 microprocessor chapter 18. Rabbit instructions 175 18.1 load immediate data ..................................................................................................................... 178 18.2 load & store to immediate address.......................................................

Page 7: 1. I

User’s manual 1 1. I ntroduction rabbit semiconductor was formed expressly to design a a better microprocessor for use in small and medium-scale controllers. The first product is the rabbit 2000 microprocessor. The rabbit 2000 designers have had years of experience using z80, z180 and hd64180 microp...

Page 8

2 rabbit 2000 microprocessor • access to i/o devices is accomplished by using memory access instructions with an i/o prefix. Access to i/o devices is thus faster and easier compared to processors with a restricted i/o instruction set. • the hardware design rules are simple. Up to six static memory c...

Page 9

User’s manual 3 • the built-in main clock oscillator uses an external crystal or more usually a ceramic resonator. Typical resonator frequencies are in the range of 1.8 mhz to 29.5 mhz. Since precision timing is available from the separate 32.768 khz oscillator, a low-cost ceramic resonator with ½ p...

Page 10

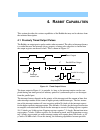

4 rabbit 2000 microprocessor figure 1-1 shows a block diagram of the rabbit. Figure 1-1. Block diagram of the rabbit microprocessor cpu external interface data buffer memory management/ control address buffer memory chip interface parallel port a parallel port b parallel port c parallel port d globa...

Page 11

User’s manual 5 1.2 summary of rabbit advantages • the glueless architecture makes it is easy to design the hardware system. • there are a lot of serial ports and they can communicate very fast. • precision pulse and edge generation is a standard feature. • interrupts can have multiple priorities. •...

Page 12

6 rabbit 2000 microprocessor.

Page 13: 2. R

User’s manual 7 2. R abbit d esign f eatures the rabbit is an evolutionary design. The instruction set and the register layout is that of the z80 and z180. The instruction set has been augmented by a substantial number of new instructions. Some obsolete or redundant z180 instructions have been dropp...

Page 14

8 rabbit 2000 microprocessor 2.1 the rabbit 8-bit processor vs. 16-bit and 32-bit processors the rabbit is an 8-bit processor with an 8-bit external data bus and an 8-bit internal data bus. Because the rabbit makes the most of its external 8-bit bus and because it has a com- pact instruction set, it...

Page 15

User’s manual 9 table 2-1 provides estimates of the operating power for selected clock speeds. 2.2.3 time/date oscillator the 32.768 khz oscillator drives an external 32.768 khz quartz crystal. The 32.768 khz clock is used to drive a battery-backable (there is a separate power pin) internal 48-bit c...

Page 16

10 rabbit 2000 microprocessor 2.2.5 slave port the slave port is designed to allow the rabbit to be a slave to another processor, which could be another rabbit. The port is shared with parallel port a and is a bidirectional data port. The master can read any of three registers selected via two selec...

Page 17

User’s manual 11 counter that can be read but not written. There are two 10-bit match registers and compar- ators. If the match register matches the counter, a pulse is output. Thus the timer can be programmed to output a pulse at a predetermined count in the future. This pulse can be used to clock ...

Page 18

12 rabbit 2000 microprocessor 2.3 design standards the same functionality can be accomplished in many ways using the rabbit. By publish- ing design standards, or standard ways to accomplish common objectives, software and hardware support become easier. 2.3.1 programming port rabbit semiconductor pu...

Page 19: 3. D

User’s manual 13 3. D etails on r abbit m icroprocessor f eatures 3.1 processor registers the rabbit’s registers are nearly identical to those of the z180 or the z80. The figure below shows the register layout. The xpc and ip registers are new. The eir register is the same as the z80 i register, and...

Page 20

14 rabbit 2000 microprocessor the rabbit (and the z80/z180) processor has two accumulators—the a register serves as an 8-bit accumulator for 8-bit operations such as add or and . The 16-bit register hl regis- ter serves as an accumulator for 16-bit operations such as add hl,de , which adds the 16- b...

Page 21

User’s manual 15 3.2 memory mapping except for a handful of special instructions (see section 18.5, “16-bit load and store 20- bit address”), the rabbit instructions directly address a 64k data memory space. This means that the address fields in the instructions are 16 bits long and that the registe...

Page 22

16 rabbit 2000 microprocessor figure 3-3. Example of memory mapping operation the names given to the segments in the figure are evocative of the common uses for each segment. The root segment is mapped to the base of flash memory and contains the star- tup code as well as other code that may happen ...

Page 23

User’s manual 17 the root segment or it may contain data variables. The stack segment is normally 4k long and it holds the system stack. The xpc segment is normally used to execute code that is not stored in the root segment or the data segment. Special instructions support executing code that is vi...

Page 24

18 rabbit 2000 microprocessor 3.2.1 extended code space a crucial element of the rabbit memory mapping scheme is the ability to execute pro- grams containing up to a megabyte of code in an efficient manner. This ability is absent in a pure 16-bit address processor, and it is poorly supported by the ...

Page 25

User’s manual 19 than the xpc segment, can call other code in the root using short jumps and calls. Code in the xpc segment can also call code in the root using short jumps and calls. However, a long call must be used when code in the xpc segment is called. Functions located in the root have an effi...

Page 26

20 rabbit 2000 microprocessor be the software structures associated with a tcp/ip communication protocol connection where the same code accesses the data structures associated with each connection in a pat- tern determined by the traffic on each connection. The advantage of this approach is that nor...

Page 27

User’s manual 21 the xpc segment at the top of the memory can also be used as a data segment by pro- grams that are compiled into root memory. This is handy for small programs that need to access a lot of data. 3.2.3 practical memory considerations the simplest rabbit configurations have one flash m...

Page 28

22 rabbit 2000 microprocessor 3.3 instruction set outline “load immediate data to a register” on page 23 “load or store data from or to a constant address” on page 23 “load or store data using an index register” on page 24 “register to register move” on page 25 “register exchanges” on page 25 “push ...

Page 29

User’s manual 23 • input/output instructions are now accomplished by normal memory access instructions prefixed by an op code byte to indicate access to an i/o space. There are two i/o spaces, internal peripherals and external i/o devices. Some z80 and z180 instructions have been deleted and are not...

Page 30

24 rabbit 2000 microprocessor 3.3.3 load or store data using an index register an index register is a 16-bit register, usually ix, iy, sp or hl, that is used for the address of a byte or word to be fetched from or stored to memory. Sometimes an 8-bit offset is added to the address either as a signed...

Page 31

User’s manual 25 3.3.4 register to register move any of the 8-bit registers, a, b, c, d, e, h, and l, can be moved to any other 8-bit regis- ter, for example: ld a,c ld d,b ld e,l the alternate 8-bit registers can be a destination, for example: ld a',c ld d',b these instructions are unique to the ra...

Page 32

26 rabbit 2000 microprocessor 3.3.6 push and pop instructions there are instructions to push and pop the 16-bit registers af, hl, dc, bc, ix, and iy. The registers af', hl', de', and bc' can be popped. Popping the alternate registers is exclusive to the rabbit, and is not allowed on the z80 / z180. ...

Page 33

User’s manual 27 the bool instruction is a special instruction designed to help test the hl register. Bool sets hl to the value 1 if hl is non zero, otherwise, if hl is zero its value is not changed. The flags are set according to the result. Bool can also operate on ix and iy. Bool hl ; set hl to 1...

Page 34

28 rabbit 2000 microprocessor the sbc instruction can also be used to perform a sign extension. ; extend sign of l to hl ld a,l rla ; sign to carry sbc a,a ; a is all 1’s if sign negative ld h,a ; sign extended the multiply instruction performs a signed multiply that generates a 32-bit signed result...

Page 35

User’s manual 29 3.3.8 input/output instructions the rabbit uses an entirely different scheme for accessing input/output devices. Any memory access instruction may be prefixed by one of two prefixes, one for internal i/o space and one for external i/o space. When so prefixed, the memory instruction ...

Page 36

30 rabbit 2000 microprocessor the bug may be easily avoided by placing a nop between the i/o instruction and a follow- ing instruction from the above list. Rabbit users are unlikely to encounter this problem because the sequence of instructions that exhibit the bug is never generated by the dynamic ...

Page 37

User’s manual 31 3.4 how to do it in assembly language—tips and tricks 3.4.1 zero hl in 4 clocks bool hl ; 2 clocks, clears carry, hl is 1 or 0 rr hl ; 2 clocks, 4 total - get rid of possible 1 this sequence requires four clocks compared to six clocks for ld hl,0 . 3.4.2 exchanges not directly imple...

Page 38

32 rabbit 2000 microprocessor 3.4.4 comparisons of integers unsigned integers may be compared by testing the zero and carry flags after a subtract operation. The zero flag is set if the numbers are equal. With the sbc instruction the carry cleared is set if the number subtracted is less than or equa...

Page 39

User’s manual 33 some simplifications are possible if one of the unsigned numbers being compared is a constant. Note that the carry has a reverse sense from sbc . In the following examples, the pseudo-code in the form ld de,(65535-b) does not indicate a load of de with the address pointed to by 6553...

Page 40

34 rabbit 2000 microprocessor a>b (!S & !V & !Z) v (s & v) a a==b a>=b a another method of doing signed compare is to first map the signed integers onto unsigned integers by inverting bit 15. This is shown in figure 3-7 on page 34. Once the mapping has been performed by inverting bit 15 on both numb...

Page 41

User’s manual 35 3.5 interrupt structure when an interrupt occurs on the rabbit, the return address is pushed on the stack, and con- trol is transferred to the address of the interrupt service routine. The address of the inter- rupt service routine has two parts: the upper byte of the address comes ...

Page 42

36 rabbit 2000 microprocessor the same priority, this introduces interrupt latency while the next routine is waiting for the previous routine to allow more interrupts to take place. If a number of devices have inter- rupt service routines, and all interrupts are of the same priority, then pending in...

Page 43

User’s manual 37 3.5.2 multiple external interrupting devices the rabbit has two distinct external interrupt request lines. If there are more than two external causes of interrupts, then these lines must be shared between multiple devices. The interrupt line is edge sensitive, meaning that it reques...

Page 44

38 rabbit 2000 microprocessor the privileged instructions to manipulate the ip register are listed below. Ipset 0 ; shift ip left and set priority 00 in bits 1,0 ipset 1 ipset 2 ipset 3 ipres ; rotate ip right 2 bits, restoring previous priority reti ; pops ip from stack and then pops return address...

Page 45

User’s manual 39 3.5.6 computed long calls and jumps the instruction to set the xpc is privileged to so that a computed long call or jump can be made. This would be done by the following sequence. Ld xpc,a jp (hl) in this case, a has the new xpc, and hl has the new pc. This code should normally be e...

Page 46

40 rabbit 2000 microprocessor.

Page 47: 4. R

User’s manual 41 4. R abbit c apabilities this section describes the various capabilities of the rabbit that may not be obvious from the technical description. 4.1 precisely timed output pulses the rabbit can output precise pulses under software control. The effect of interrupt latency is avoided be...

Page 48

42 rabbit 2000 microprocessor pulse width modulated output—the minimum pulse width is 10 µs. If the repetition rate is 10 ms, then a new pulse with 1000 different widths can be generated at the rate of 100 times per second. Asynchronous communications serial output—asynchronous output data can be ge...

Page 49

User’s manual 43 4.1.1 pulse width modulation to reduce relay power typically relays need far less current to hold them closed than is needed to initially close them. For example, if the driver is switched to a 75% duty cycle using pulse width modu- lation after the initial period when the relay arm...

Page 50

44 rabbit 2000 microprocessor push af ;10 push hl ld hl,(ptr) ;11 ld a,(hl) ;5 ioi ld (port),a ; 13 output data inc hl ld a,0x0f ;4 and l ; see if hl at end of cycle jr z,step2 ld (ptr),hl pop hl pop af reti step2: ld a,(beginptr) ld l,a ld (ptr),hl ;13 pop hl ;7 pop af reti ; 103 clocks total 4.2 o...

Page 51

User’s manual 45 4.3 cold boot most microprocessors start executing at a fixed address, often address zero, after a reset or power-on condition. The rabbit has two mode pins (smode0, smode1—see figure 5- 1). The logic state of these two pins determines the startup procedure after a reset. If both pi...

Page 52

46 rabbit 2000 microprocessor 4.4 the slave port the slave port allows a rabbit to act as a slave to another processor, which can also be a rabbit. The slave has to have only a processor chip, a ram chip, and clock and reset sig- nals that can be supplied by the master. The master can cold boot and ...

Page 53

User’s manual 47 of the three registers seen by each side for each direction of communication, the first reg- ister, slave register zero, has a special function because an interrupt can only be generated by a write to this register, which then causes an interrupt to take place on the other side of t...

Page 54

48 rabbit 2000 microprocessor.

Page 55: 5. P

User’s manual 49 5. P in a ssignments and f unctions 5.1 package schematic and pinout figure 5-1. Package outline and pin assignments pb 6 p b 7, /s l a v e a ttn p a 0, sd 0 pb 5 , sa1 pb 4 , sa0 pb 3 , / s r d pb 2 , / s wr pa 1 , s d 1 pb 1 , c l ka pb 0 , c l kb vdd p a 2, sd 2 xt a l b 2 xt a l...

Page 56

50 rabbit 2000 microprocessor 5.2 package mechanical dimensions figure 5-2 shows the mechanical dimensions of the rabbit pqfp package. Figure 5-2. Mechanical dimensions rabbit pqfp package figure 5-3 shows the pc board land pattern for the rabbit 100-pin pqfp. This land pat- tern is rlp 711a, the re...

Page 57

User’s manual 51 figure 5-3. Pc board land pattern for rabbit 100-pin pqfp 15.29 mm (min.) 18.71 mm (max.) 12.35 mm 17.0 mm 0.3450.44 mm 0.65 mm 21.29 mm (min.) 24.71 mm (max.) 1 30 31 50 51 80 81 100 18.85 mm 23.0 mm 1.71 mm j t : 0.270.53 mm toe fillet j h : 0.220.55 mm heel fillet j s : 00.12...

Page 58

52 rabbit 2000 microprocessor 5.3 rabbit pin descriptions table 5-1 lists all the pins on the device, along with their direction, function, and pin num- ber on the package. Table 5-1. Rabbit pin descriptions pin group pin name direction function pin numbers hardware clk output peripheral clock outpu...

Page 59

User’s manual 53 status smode1 smode0 input startup mode select (smode1 = pin 35, smode0 = pin 36) to determine bootstrap procedure. (smode1 = 0, smode0 = 0) start executing at address zero. (0,1) cold boot from slave port. (1,0) cold boot from clocked serial port a. (1,1) cold boot from asynchronou...

Page 60

54 rabbit 2000 microprocessor i/o read strobe /iord output i/o read strobe. Driven low on an external i/o read bus cycle. May be used to drive glue logic concerned with i/o expansion, such as the direction pin on a bidirectional bus buffer. See also programmable strobes in port e. 32 i/o write strob...

Page 61

User’s manual 55 i/o port d pd0–pd7 input/ output/ output open drain i/o port d. Each bit may be individually selected to be an input or output. Each output may be selected to be high-low drive or open drain. Outputs are buffered by timer-synchronizable registers for precision edge control. Pd6 can ...

Page 62

56 rabbit 2000 microprocessor power vbat +3.0 v (battery backup), +3.3 v or +5.0 v 42 vdd +3.3 v or +5.0 v 3, 28, 53, 78, 92 vss ground 2, 27, 39, 52, 77, 89 serial ports clka input/ output clock for serial port a when operating in synchronous mode. Alternate assignment for pb1. 94 clkb input/ outpu...

Page 63

User’s manual 57 i/o strobes /i0,/i1, /i2, /i3, /i4, /i5, /i6, /i7 outputs i/o strobes. Each strobe uses 1/8th of the i/o space or 8k addresses. Each strobe can be programmed as: chip select, read, write, combined read or write. These are alternate pin assignment for parallel port e, bits 0–7. Each ...

Page 64

58 rabbit 2000 microprocessor 5.4 bus timing the external bus has essentially the same timing for memory cycles or i/o cycles. A memory cycle begins with the chip select and the address lines. One clock later, the out- put enable is asserted for a read. The output data and the write enable are asser...

Page 65

User’s manual 59 5.5 description of pins with alternate functions table 5-2. Pins with alternate functions pin name output function input function other function status (38) 1. Low on first op code fetch. 2. Low on interrupt acknowledge programmable output port high/low smode1 (35) (smode0, smode1) ...

Page 66

60 rabbit 2000 microprocessor pb1 (94) clka (serial port a clocked mode clock, bidirectional). Clka pb0 (93) clkb (bidirectional). Clkb pc7 (51) rxa pc6 (54) txa pc5 (55) rxb pc4 (56) txb pc3 (57) rxc pc2 (58) txc pc1 (59) rxd pc0 (60) txd pd7 (43) arxa pd6 (44) atxa pd5 (45) arxb pd4 (46) atxb pd3 ...

Page 67

User’s manual 61 5.6 dc characteristics note: stresses beyond those listed in table 5-3 may cause permanent damage. The rat- ings are stress ratings only, and functional operation of the rabbit 2000 chip at these or any other conditions beyond those indicated in this section is not implied. Exposure...

Page 68

62 rabbit 2000 microprocessor 5.6.1 5.0 volts table 5-4 outlines the dc characteristics for the rabbit at 5.0 v over the recommended operating temperature range from t a = –40°c to +85°c, v dd = 4.5 v to 5.5 v. Table 5-4. 5.0 volt dc characteristics symbol parameter test conditions min typ max units...

Page 69

User’s manual 63 5.6.2 3.3 volts table 5-5 outlines the dc characteristics for the rabbit at 3.3 v over the recommended operating temperature range from t a = –40°c to +85°c, v dd = 2.7 v to 3.6 v. Table 5-5. 3.3 volt dc characteristics symbol parameter test conditions min typ max unit s i ih input ...

Page 70

64 rabbit 2000 microprocessor 5.7 i/o buffer sourcing and sinking limit unless otherwise specified, the rabbit i/o buffers are capable of sourcing and sinking 8 ma of current per pin at full ac switching speed. Full ac switching assumes 22.11 mhz cpu clock and capacitive loading on address and data ...

Page 71: 6. R

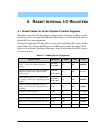

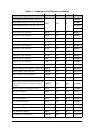

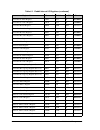

User’s manual 65 6. R abbit i nternal i/o r egisters 6.1 default values for all the peripheral control registers the default values for all of the peripheral control registers are shown in table 6-1. Addi- tional i/o registers were added in the rabbit 2000 revisions as listed in the table. Refer to ...

Page 72

66 rabbit 2000 microprocessor rabbit 2000 global revision register (rev a–c) grev 0x2f r 0xx00000 rabbit 2000a global revision register (rev a–c) 0xx00001 rabbit 2000b global revision register (rev a–c) 0xx00010 rabbit 2000c global revision register (rev a–c) 0xx00011 i/o bank 0 control register ib0...

Page 73

User’s manual 67 port d data direction register pdddr 0x67 w 00000000 port d bit 0 register pdb0r 0x68 w xxxxxxxx port d bit 1 register pdb1r 0x69 w xxxxxxxx port d bit 2 register pdb2r 0x6a w xxxxxxxx port d bit 3 register pdb3r 0x6b w xxxxxxxx port d bit 4 register pdb4r 0x6c w xxxxxxxx port d bit...

Page 74

68 rabbit 2000 microprocessor serial port a status register sasr 0xc3 r 0xx00000 serial port a control register sacr 0xc4 w xx000000 serial port b data register sbdr 0xd0 r/w xxxxxxxx serial port b address register sbar 0xd1 w xxxxxxxx serial port b status register sbsr 0xd3 r 0xx00000 serial port b...

Page 75

User’s manual 69 timer b control/status register tbcsr 0xb0 r/w xxxxx000 timer b control register tbcr 0xb1 w xxxx0000 timer b msb 1 register tbm1r 0xb2 w xxxxxxxx timer b lsb 1 register tbl1r 0xb3 w xxxxxxxx timer b msb 2 register tbm2r 0xb4 w xxxxxxxx timer b lsb 2 register tbl2r 0xb5 w xxxxxxxx t...

Page 76

70 rabbit 2000 microprocessor.

Page 77: 7. M

User’s manual 71 7. M iscellaneous i/o f unctions 7.1 processor identification two read-only registers are provided to allow software to identify the rabbit microproces- sor and recognize the features and capabilities of the chip. Five bits in each of these regis- ters are unique to each version of ...

Page 78

72 rabbit 2000 microprocessor 7.2 rabbit oscillators and clocks there are two crystal oscillators built into the rabbit. The main oscillator accepts crystals up to a frequency of 29.4912 mhz (first overtone crystals only). The clock oscillator requires a 32.768 khz crystal, which is powered by vbat,...

Page 79

User’s manual 73 table 7-1. Global control/status register (i/o adr = 0x00) bit(s) value description 7:6 00 no reset or watchdog timer timeout since the last read. (read only) 01 the watchdog timer timed out. These bits are cleared by a read of this register. 10 this bit combination is not possible....

Page 80

74 rabbit 2000 microprocessor 7.3 clock doubler the clock doubler is provided to allow a lower frequency crystal to be used for the main oscillator and to provide an added range of clock frequency adjustability. The clock dou- bler is controlled via the global clock double register as shown in table...

Page 81

User’s manual 75 when the clock doubler is used and there is no subsequent division of the clock, the output clock will be asymmetric, as shown in figure 7-2. Figure 7-2. Effect of clock doubler the doubled clock-low time is subject to wide (50%) variation since it depends on process parameters, tem...

Page 82

76 rabbit 2000 microprocessor the doubled clock is created by xor’ing the delayed and inverted clock with itself. If the original clock does not have a 50-50 duty cycle, then alternate clocks will have a slightly different length. Since the duty cycle of the built-in oscillator can be as asymmetric ...

Page 83

User’s manual 77 7.5 output pins clk, status, /wdtout, /bufen certain output pins can have alternate assignments as specified in table 7-4. Table 7-4. Global output control register (gocr = 0x0e) bit(s) value description 7:6 00 clk pin is driven with peripheral clock. 01 clk pin is driven with perip...

Page 84

78 rabbit 2000 microprocessor 7.6 time/date clock (real-time clock) the time/date clock (rtc) is a 48-bit (ripple) counter that is driven by the 32.768 khz oscillator. The rtc is a modified ripple counter composed of six separate 8-bit counters. The carries are fed into all six 8-bit counters at the...

Page 85

User’s manual 79 table 7-6. Real-time clock rtcxr data registers bit(s) value description 7:0 read the current value of the 48-bit rtc holding register is returned. Write writing to the rtc0r transfers the current count of the rtc to six holding registers while the rtc continues counting. Table 7-7....

Page 86

80 rabbit 2000 microprocessor 7.7 watchdog timer the watchdog timer is a 17-bit counter. In normal operation it is driven by the 32.768 khz clock. When the watchdog timer reaches any of several values corresponding to a delay of from 0.25 to 2 seconds, it “times out.” when it times out, it emits a 1...

Page 87

User’s manual 81 the code to do this may also hit the watchdog with a 0.25-second period to speed up the reset. Such watchdog code must be written so that it is highly unlikely that a crash will incorporate the code and continue to hit the watchdog in an endless loop. The following suggestions will ...

Page 88

82 rabbit 2000 microprocessor 7.8 system reset the rabbit has a master reset input (/reset), which initializes everything in the device except for the rtc. This reset is delayed until the completion of any write cycles in progress to prevent any potential corruption of memory. If no write cycles are...

Page 89

User’s manual 83 table 7-10. Rabbit 2000 reset sequence and state of i/o pins pin name direction /reset low * recognized by cpu post-reset † /reset input low or high high clk output high operational xtala1 input not affected not affected xtala2 output not affected not affected xtalb1 input not affec...

Page 90

84 rabbit 2000 microprocessor 7.9 rabbit interrupt structure an interrupt causes a call to be executed, pushing the pc on the stack and starting to exe- cute code at the interrupt vector address. The interrupt vector addresses have a fixed lower byte value for all interrupts. The upper byte is adjus...

Page 91

User’s manual 85 the interrupts differ from most z80 or z180 interrupts in that the 256-byte tables pointed to eir and iir contain the actual instructions beginning the interrupt routines rather than a 16-bit pointer to the routine. The interrupt vectors are spaced 16 bytes apart so that the entire ...

Page 92

86 rabbit 2000 microprocessor 7.9.1 external interrupts there are two external interrupts. Because of a problem in the original rabbit design, only one of these interrupts is available for general use. The problem was corrected in revisions a–c of the rabbit 2000. (refer to appendix b for further in...

Page 93

User’s manual 87 7.9.2 interrupt vectors: int0 - eir,0x00/int1 - eir,0x08 when it is desired to expand the number of interrupts for additional peripheral devices, the user should use the interrupt routine to dispatch interrupts to other virtual interrupt rou- tines. Each additional interrupting devi...

Page 94

88 rabbit 2000 microprocessor 7.10 bootstrap operation the device provides the option of bootstrap from any of three sources: from the slave port, from serial port a in clocked serial mode, or from serial port a in asynchronous mode. This is controlled by the state of the smode pins after reset. Boo...

Page 95

User’s manual 89 serial port a is selected for bootstrap operation as a clocked serial port when smode = 10. In this case bit 7 of parallel port c is used for the serial data and bit 1 of parallel port b is used for the serial clock. Note that the serial clock must be externally supplied for boot- s...

Page 96

90 rabbit 2000 microprocessor.

Page 97: 8. M

User’s manual 91 8. M emory m apping and i nterface see section 3.2, “memory mapping,” for a discussion of the rabbit memory mapping. Figure 8-1 shows an overview of the rabbit memory mapping. The task of the memory mapping unit is to accept 16-bit addresses and translate them to 20-bit addresses. T...

Page 98

92 rabbit 2000 microprocessor figure 8-2. Memory segments the memory management unit accepts a 16-bit address from the processor and translates it into a 20-bit address. The procedure to do this works as follows. 1. It is determined which segment the 16-bit address belongs to by inspecting the upper...

Page 99

User’s manual 93 8.2 memory interface unit the 20-bit memory addresses generated by the memory-mapping unit feed into the mem- ory interface unit. The memory interface unit has a separate write-only control register (see table 8-3) for each 256k quadrant of the 1m physical memory. This control regis...

Page 100

94 rabbit 2000 microprocessor 8.3 memory control unit registers the memory bank control registers manage the physical memory space for the rabbit 2000. There are four memory banks, where each bank is selected by the two most signifi- cant bits of the 20-bit physical memory address. Each memory bank ...

Page 101

User’s manual 95 8.3.2 mmu instruction/data register 8.3.2.1 instruction and data space support support for instruction and data space (i and d space) support was added in revisions a–c by optionally inverting address lines a16 and/or a19 when the processor accesses d space, but not inverting those ...

Page 102

96 rabbit 2000 microprocessor 8.4 allocation of extended code and data the dynamic c compiler compiles code to root code space or to extended code space. Root code starts in low memory and compiles upward. Figure 8-3. Example of memory mapping and memory usage allocation of extended code starts abov...

Page 103

User’s manual 97 8.5 how compiler compiles to memory the compiler actually generates code for root code and constants and extended code and extended constants. It allocates space for data variables, but does not generate data bits to be stored in memory. In any but the smallest programs, most of the...

Page 104

98 rabbit 2000 microprocessor figure 8-4. Compilation of code segments in extended memory memory view in 8k window each segment e000 ffff e000 ffff 4k pages.

Page 105: 9. P

User’s manual 99 9. P arallel p orts the rabbit has five 8-bit parallel ports designated a, b, c, d and e. The pins used for the parallel ports are also shared with numerous other functions as shown in table 5-2. The important properties of the ports are summarized below. • port a—shared with the sl...

Page 106

100 rabbit 2000 microprocessor 9.1 parallel port a parallel port a has a single read/write register. This register should not be used if the slave port is enabled. The slave port control register is used to control whether parallel port a is an output or an input. To make the port an input, store 0x...

Page 107

User’s manual 101 9.2 parallel port b parallel port b, shown in table 9-4, has six inputs and two outputs when used exclusively as a parallel port. When the slave port is enabled, parallel port lines pb2–pb7 are assigned to various slave port functions. However, it is still possible to read pb0–pb5 ...

Page 108

102 rabbit 2000 microprocessor 9.3 parallel port c parallel port c, shown in table 9-6, has four inputs and four outputs. The even-numbered ports, pc0, pc2, pc4, and pc6, are outputs. The odd-numbered ports, pc1, pc3, pc5, and pc7, are inputs. When the data register is read, bits 1,3,5,7 return the ...

Page 109

User’s manual 103 9.4 parallel port d parallel port d, shown in figure 9-1, has eight pins that can programmed individually to be inputs and outputs. When programmed as outputs, the pins can be individually selected to be open-drain outputs or standard outputs. Port d pins can be addressed by bit if...

Page 110

104 rabbit 2000 microprocessor • pdcr—parallel port d control register. This register is used to control the clocking of the upper and lower nibble of the final output register of the port. On reset, bits 0, 1, 4, and 5 are reset to zero. Figure 9-1. Parallel port d block diagram pd7 pd4 i/o data pe...

Page 111

User’s manual 105 table 9-8. Parallel port d registers bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 pddr (r/w) adr = 0x060 pd7 pd6 pd5 pd4 pd3 pd2 pd1 pd0 pddcr (w) adr = 0x066 out = open drain out = open drain out = open drain out = open drain out = open drain out = open drain out = open drain o...

Page 112

106 rabbit 2000 microprocessor 9.5 parallel port e parallel port e, shown in figure 9-2, has eight i/o pins that can be individually pro- grammed as inputs or outputs. Port e has a higher drive than most of the other ports. Pe7 is used as the slave port chip select when the slave port is enabled. Ea...

Page 113

User’s manual 107 the following registers are described in table 9-11 and in table 9-12. • pedr—port e data register. Reads value at pins. Writes to port e preload register. • peddr—port e data direction register. Set to "1" to make corresponding pin an out- put. This register is zeroed on reset. • ...

Page 114

108 rabbit 2000 microprocessor table 9-11. Parallel port e registers bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 pedr (r/w) adr = 0x070 pe7 pe6 pe5 pe4 pe3 pe2 pe1 pe0 pefr (w) adr = 0x075 alt /i7 alt /i6 alt /i5 alt /i4 alt /i3 alt /i2 alt /i1 alt /i0 peddr (w) adr = 0x077 dir = out dir = out d...

Page 115: 10. I/o B

User’s manual 109 10. I/o b ank c ontrol r egisters the pins of port e can be set individually to be i/o strobes. Each of the eight possible i/o strobes has a control register that controls the nature of the strobe and the number of wait states that will be inserted in the i/o bus cycle. Writes can ...

Page 116

110 rabbit 2000 microprocessor compared to memory read/write cycles, which are each 2 or 3 clock cycles long respectively, external i/o read/write cycles are always at least three clock cycles long. The eight i/o bank control registers determine the number of i/o wait states applied to an external i...

Page 117: 11. T

User’s manual 111 11. T imers there are two timers—timer a and timer b. Timer a is intended mainly for generating the baud clock for the serial ports, a periodic clock for clocking parallel ports d and e, or for generating periodic interrupts. Timer b can be used for the same functions, but it can- ...

Page 118

112 rabbit 2000 microprocessor 11.1 timer a timer a consists of five separate countdown timers—a1 and a4–a7—as shown in figure 11-1. Timers a1 and a4–a7 are 8-bit countdown registers as shown in figure 11-2. The reload register can contain any number in the range from 0 to 255. The counter divides b...

Page 119

User’s manual 113 place since the last read of the status register. When the status register is read, these bits are cleared. No bit will be lost. Either it will be read by the status register read or it will be set after the status register read is complete. If a bit is on and the corresponding int...

Page 120

114 rabbit 2000 microprocessor the control register (tacr) is laid out as shown in table 11-3. The time constant register for each timer is simply an 8-bit data register holding a number between 0 and 255. The time constant registers are write only. 11.1.2 practical use of timer a timer a is disable...

Page 121

User’s manual 115 11.2 timer b figure 11-1 shows a block diagram of timer b. The main clock for timer b is pclk /2. Bit 0 of the tbcsr register controls the main clock for timer b. The timer b counter can be driven directly by pclk /2, pclk /16 [( pclk /2)/8], or by the output of timer a1. The first...

Page 122

116 rabbit 2000 microprocessor the timer b i/o registers are listed in table 11-4. The control/status register for timer b (tbcsr) is laid out as shown in table 11-5. The control register for timer b (tbcr) is laid out as shown in table 11-6. The msb x registers for timer b (tbm1r/tbm2r) are laid ou...

Page 123

User’s manual 117 11.2.1 using timer b normally the prescaler is set to divide pclk /2 by a number that provides a counting rate appropriate to the problem. For example, if the clock is 22.1184 mhz, then pclk /2 is 11.0592 mhz. A timer b clock rate of 11.0592 mhz will cause a complete cycle of the 1...

Page 124

118 rabbit 2000 microprocessor timer b can be used for various purposes. The 10-bit counter can be read to record the time at which an event takes place. If the event creates an interrupt, the timer can be read in the interrupt routine. The known time of execution of the interrupt routine can be sub...

Page 125: 12. R

User’s manual 119 12. R abbit s erial p orts two features related to asynchronous and clocked serial communication were added to the rabbit 2000 serial port hardware in revisions a–c to improve and simplify asynchronous serial and clocked serial communication. See section b.2.3 for more information....

Page 126

120 rabbit 2000 microprocessor 12.1 serial port register layout figure 12-2 shows a functional block diagram of a serial port. Each serial port has a data register, a control register and a status register. Writing to the data register starts transmis- sion. If the write is performed to an alternate...

Page 127

User’s manual 121 table 12-1 lists the serial port registers. Table 12-2 describes the serial port status registers. Writing to the status register clears the transmit interrupt request ff, but has no other effect. Bit 7—receiver ready. This bit is set when a byte is transferred from the receiver sh...

Page 128

122 rabbit 2000 microprocessor table 12-3 describes the serial port control registers. Bits 7,6—in asynchronous mode, always store zero in these bits. For ports a and b, if the clocked serial mode is enabled, store the code here to start an operation, either receive or send. If the clock is internal...

Page 129

User’s manual 123 12.2 serial port interrupt a common interrupt vector is used for the receive and transmit interrupts. There is a sepa- rate interrupt request flip-flop for the receiver and transmitter. If either of these flip-flops is set, a serial port interrupt is requested. The flip-flops are s...

Page 130

124 rabbit 2000 microprocessor 12.3 transmit serial data timing on transmit, if the interrupts are enabled, an interrupt is requested when the transmit regis- ter becomes empty and, in addition, an interrupt occurs when the shift register and trans- mit register both become empty, that is, when the ...

Page 131

User’s manual 125 12.5 clocked serial ports see section b.2.3 for more information for more information about a new feature added to revisions a–c to better support full-duplex communication. Ports a and b can operate in clocked mode. The data line and clock line are driven as shown in figure 12-4. ...

Page 132

126 rabbit 2000 microprocessor table 12-4 lists the synchronous serial port signals. To enable the clocked serial mode, a code must be in bits (3,2) of the control register, enabling the clocked serial mode with either an internal clock or an external clock. The transition between the external and t...

Page 133

User’s manual 127 made to the shift register, a new byte can be loaded into the transmit register and a new send code can be stored. To receive a byte in external clock mode, the user must set the receive code for the first byte and then store the receive code for the next byte after each byte is re...

Page 134

128 rabbit 2000 microprocessor 12.6 clocked serial timing 12.6.1 clocked serial timing with internal clock for synchronous serial communication, the serial clock can be either generated by the rabbit or by an external device. The timing diagram in figure 12-5 below can be applied to both full-duplex...

Page 135

User’s manual 129 figure 12-7 shows the timing relationship among perclk , the external serial clock, and data receive. Note that rxa is sampled by the rising edge of perclk . Figure 12-7. Synchronous serial data receive timing with external clock when clocking the rabbit externally, the maximum ser...

Page 136

130 rabbit 2000 microprocessor an exception to be aware of when a serial port has to operate at an extremely high speed. At 115,200 bps, the highest speed of a pc serial port, the interrupts must be serviced in 10 baud times, or 86 µs, in order not to lose the received characters. If all four serial...

Page 137

User’s manual 131 12.7.1 controlling an rs-485 driver and receiver rs-485 uses a half-duplex method of communication. One station enables its driver and sends a message. After the message is complete, the station disables the driver and listens to the line for a reply. The driver must be enabled bef...

Page 138

132 rabbit 2000 microprocessor 12.7.5 extra stop bits, sending parity, 9th bit communication schemes some systems may require two stop bits. In some cases, it may be necessary to send a par- ity bit. Certain systems, such as some 8051-based multidrop communications systems, use a 9th data bit to mar...

Page 139

User’s manual 133 12.7.5.2 parity, extra stop bits with 8 data bit characters in order to receive parity with 8 data bits, a check is made on each character for a 9th bit low. The 9th bit, or parity bit, is low if bit 6 of the serial port status register is set to a "1" after the character is receiv...

Page 140

134 rabbit 2000 microprocessor applications such as modbus require controlling gaps between characters. Thus, it would be inadvisable to attempt modbus with parity at a high data rate. Other ways to add a 1-baud delay are listed below: • use another serial port as a timer. Disable the interrupts on ...

Page 141

User’s manual 135 address of the slave, then the “wake up” mode is turned off so that the remaining charac- ters in the frame can be read. This scheme reduces the overhead associated with messages directed to other slaves, but it does not really help with the worst-case load. In most cases, the wors...

Page 142

136 rabbit 2000 microprocessor.

Page 143: 13. R

User’s manual 137 13. R abbit s lave p ort when a rabbit microprocessor is configured as a slave, parallel port a and certain other data lines are used as communication lines between the slave and the master . The slave unit is a rabbit configured as a slave. The master can be another rabbit or any ...

Page 144

138 rabbit 2000 microprocessor the slave port has three data registers for each direction of communication. Three regis- ters, spd0r, spd1r, and spd2r, can be written by the master and read by the slave. Three different registers, also named spd0r, spd1r, and spd2r, can be written by the slave and r...

Page 145: Slave Port Read Cycle

User’s manual 139 the registers appear to be internal i/o registers to the slave. To the master, at least for a rabbit master, the registers appear to be external i/o registers. The figure below shows the sequence of events when the master reads/writes the slave port registers. Figure 13-2. Slave po...

Page 146

140 rabbit 2000 microprocessor the following table explains the parameters used in figure 13-2. The two spd0r registers have special functionality not shared by the other data registers. If the master writes to spd0r, an inbound interrupt flip-flop is set. If slave port interrupts are enabled, the s...

Page 147

User’s manual 141 figure 13-3. Slave port handshaking and interrupts figure 13-4 shows a sample connection of two slave rabbits to a master rabbit. The mas- ter drives the slave reset line for both slaves and provides the main processor clock from its own clock. There is no requirement that the mast...

Page 148

142 rabbit 2000 microprocessor figure 13-4. Typical connection slave rabbit to master rabbit the slave port lines are shown in figure 13-1. The function of these lines is described below. • sd0–sd7—these are bidirectional data lines, and are generally connected to the data bus of the master processo...

Page 149

User’s manual 143 • /slaveattn—this line is set low (asserted) if the slave writes to the spd0r register. This line is set high if the master writes anything to the slave status register. This line is usually connected to cause the master to be interrupted when it goes low. The data lines of the sla...

Page 150

144 rabbit 2000 microprocessor if the user for some reason wants to depart from the suggested protocols and poll a register while waiting for the other side to write something to the register, the user should be aware that all the bits might not change at the exact same time when the result changes,...

Page 151

User’s manual 145 table 13-3 describes the slave port status register. The status register has 6 bits that are set if the particular register is full. That means that the register has been written by the processor that can write to it but it has not been read by the processor that can read it. The b...

Page 152

146 rabbit 2000 microprocessor 13.3.2 master-slave messaging protocol in this protocol the master sends messages to the slave and receives an acknowledgement message. The protocol can be polled or interrupt driven. Generally, the master sends a message that has a message type code, perhaps a byte co...

Page 153

User’s manual 147 as a simple example, suppose that the slave is to be used as a four-port uart. It has the capability to send or receive characters on any of its four serial ports. Leaving aside the question of setup for parameters, such as the baud rate, we could define a protocol as fol- lows. Sp...

Page 154

148 rabbit 2000 microprocessor.

Page 155: 14. R

User’s manual 149 14. R abbit 2000 c locks the rabbit 2000 has two built-in oscillators. The 32.768 khz clock oscillator is needed for the battery-backable clock, the watchdog timer, and the cold-boot function. The main oscillator provides the run-time clock for the microprocessor. Figure 14-1 shows...

Page 156

150 rabbit 2000 microprocessor 14.1 low-power design the power consumption is proportional to the clock frequency and to the square of the operating voltage. Thus, operating at 3.3 v instead of 5 v will reduce the power consump- tion by a factor of 10.9/25, or 43% of the power required at 5 v. The c...

Page 157: 15. Ac T

User’s manual 151 15. Ac t iming s pecifications the rabbit 2000 processor may be operated at voltages between 2.5 v and 5.5 v, and at temperatures from –40°c to +85°c with use possible use over the range -55°c to +120°c. Most users will operate the rabbit at either 5.0 v or 3.3 v. The most computat...

Page 158

152 rabbit 2000 microprocessor the industrial clock speed values in table 15-1 (at a maximum temperature of 85°c) are improved by 7% over commercial ratings at 70°c (which are extended to -40°c here). The effect of temperature alone is a clock speed that is approximately 1.2% lower for each 5°c temp...

Page 159

User’s manual 153 figure 15-1. Rabbit 2000 typical maximum operating frequency versus temperature at 5 v and 3.3 v figure 15-2. Rabbit 2000 typical maximum operating frequency versus voltage at 25°c 20 25 30 35 40 45 50 55 -50 -30 -10 10 30 50 70 90 110 te mperature (°c) maxi mu m f req u e n cy ( m...

Page 160

154 rabbit 2000 microprocessor 15.1 memory access and i/o read/write times the memory access time requirements are listed in table 15-2. It is important that wait states should not be used for any memory that holds code that is being executed. Memory wait states are only intended for use with data a...

Page 161

User’s manual 155 table 15-2. Memory access time requirements (v±5%, t -40°c to +70°c) clock speed (mhz) period (ns) wait states memory access time @5 v 20 pf load (ns) memory access time @5 v 70 pf load (ns) maximum pc- compatible baud rate (bps) 29.4912 34 0 59 52 921,600 27.6480 36.2 0 64 57 57,6...

Page 162

156 rabbit 2000 microprocessor figure 15-3, figure 15-4, and figure 15-5 illustrate the memory and i/o read and write cycles. The rabbit operates at 2 clocks per bus cycle plus any wait states that might be specified. The following memory read time delays were measured. The measurements were taken a...

Page 163

User’s manual 157 figure 15-3. Memory read and write cycles notice that the data times are different, depending on whether data are being read or writ- ten. T hold for data read specifies how long the data must remain valid following the rising edge of t1 when the clock cycle repeats. T dhzv for dat...

Page 164

158 rabbit 2000 microprocessor the following i/o read time delays were measured. The measurements were taken at the 50% points under the following conditions. • t = -40°c to 85°c, v = 5.0 v ±10% • internal clock to nonloaded clk pin delay ≤ 1 ns @ 85°c/4.5 v the following i/o write time delays were ...

Page 165

User’s manual 159 i/o bus cycles have an automatic wait state and thus require 3 clocks plus any extra wait states specified. Figure 15-4. I/o read and write cycles no extra wait states tadr tadr external i/o read (no extra wait states) thold valid clk a[15:0] d[7:0] valid tsetup thold external i/o ...

Page 166

160 rabbit 2000 microprocessor figure 15-5 shows the effect of adding an extra wait state to the memory read/write cycles. The effects are similar for the i/o bus read/write cycles. Figure 15-5. Memory read and write with wait states tadr tadr memory read (one wait state) /we thold clk a[19:0] d[7:0...

Page 167

User’s manual 161 table 15-7 provides typical memory and external i/o parameters measured at 3.3 v. Table 15-7. Memory and external i/o read/write parameters at 3.3 v parameter description value re ad pa ra m e te rs t adr time from cpu clock rising edge to address valid max. 10 ns @ 20 pf 19 ns @ 7...

Page 168

162 rabbit 2000 microprocessor 15.2 current consumption typical current is proportional to both clock frequency and voltage. The main oscillator requires approximately 6 ma at 5 v and 2 ma at 3 v independent of frequency. The basic current consumption for the processor exclusive of the oscillator at...

Page 169

User’s manual 163 the 32.768 khz clock oscillator and the associated real-time clock consume approxi- mately 23 µa at 3 v. (at 2.25 v, when backed by a battery, the current consumption is approximately 11 µa.) the (typical) current consumed when the main power is off, and only the 32.768 khz oscilla...

Page 170

164 rabbit 2000 microprocessor.

Page 171: 16. R

User’s manual 165 16. R abbit bios and v irtual d river when a program is compiled by dynamic c for a rabbit target, the virtual driver is auto- matically incorporated into the program. Virtual driver is the name given to some initial- ization routines and a group of services performed by the period...

Page 172

166 rabbit 2000 microprocessor 16.1.2 bios assumptions the bios makes certain assumptions concerning the physical configuration of the proces- sor. Processors are expected to have ram connected to /cs1, /we1, and /oe1. Flash is expected to be connected to /cs0, /we0, and /oe0. (see the rabbit 2000 d...

Page 173

User’s manual 167 gram consistency checking or because a part of the program that should be executing peri- odically is not executing and the watchdog times out. The virtual driver’s periodic interrupt hits the hardware watchdog timer with a 2 second time-out. If the periodic interrupt stops working...

Page 174

168 rabbit 2000 microprocessor.

Page 175: 17. O

User’s manual 169 17. O ther r abbit s oftware 17.1 power management support the power consumption and speed of operation can be throttled up and down with rough synchronism. This is done by changing the clock speed or the clock doubler. The range of control is quite wide: the speed can vary by a fa...

Page 176

170 rabbit 2000 microprocessor 17.2 reading and writing i/o registers the rabbit has two i/o spaces: internal i/o registers and external i/o registers. 17.2.1 using assembly language the fastest way to read and write i/o registers in dynamic c is to use a short segment of assembly language inserted ...

Page 177

User’s manual 171 17.3 shadow registers many of the registers of the rabbit’s internal i/o devices are write-only. This saves gates on the chip, making possible greater capability at lower cost. Write-only registers are eas- ier to use if a memory location, called a shadow register, is associated wi...

Page 178

172 rabbit 2000 microprocessor ld hl,pdddrshadow ; point to shadow register ld de,pdddr ; set de to point to i/o reg set 5,(hl) ; set bit 5 of shadow register ; use ldd instruction for atomic transfer ioi ldd ; (io de) in this case, the ldd instruction when used with an i/o prefix provides a conveni...

Page 179

User’s manual 173 two library functions are provided to read and write the real-time clock: unsigned long int read_rtc(void) ; // read bits 15-46 rtc void write_rtc(unsigned long int time) ; // write bits 15-46 // note: bits 0-14 and bit 47 are zeroed however, it is not intended that the real-time c...

Page 180

174 rabbit 2000 microprocessor.

Page 181: 18. R

User’s manual 175 18. R abbit i nstructions summary all bugs related to instructions have been fixed in revisions a–c of the rabbit 2000 chip. See appendix b for more information. Detailed information on instructions in provided in this chapter. “load immediate data” on page 178 “8-bit indexed load ...

Page 182

176 rabbit 2000 microprocessor spreadsheet conventions altd (“a” column) symbol key flag description f altd selects alternate flags fr altd selects alternate flags and register r altd selects alternate register s altd operation is a special case ioi and ioe (“i” column) symbol key flag description b...

Page 183

User’s manual 177 symbols rabbit z180 meaning b b bit select: 000 = bit 0, 001 = bit 1, 010 = bit 2, 011 = bit 3, 100 = bit 4, 101 = bit 5, 110 = bit 6, 111 = bit 7 cc cc condition code select: 00 = nz, 01 = z, 10 = nc, 11 = c d d 7-bit (signed) displacement. Expressed in two’s complement. Dd ww wor...

Page 184

178 rabbit 2000 microprocessor 18.1 load immediate data instruction clk a i s z v c operation ld ix,mn 8 - - - - ix = mn ld iy,mn 8 - - - - iy = mn ld dd,mn 6 r - - - - dd = mn ld r,n 4 r - - - - r = n 18.2 load & store to immediate address instruction clk a i s z v c operation ld (mn),a 10 d - - - ...

Page 185

User’s manual 179 18.5 16-bit load and store 20-bit address instruction clk a i s z v c operation ldp (hl),hl 12 - - - - (hl) = l; (hl+1) = h. (adr[19:16] = a[3:0]) ldp (ix),hl 12 - - - - (ix) = l; (ix+1) = h. (adr[19:16] = a[3:0]) ldp (iy),hl 12 - - - - (iy) = l; (iy+1) = h. (adr[19:16] = a[3:0]) l...

Page 186

180 rabbit 2000 microprocessor 18.7 exchange instructions instruction clk a i s z v c operation ex (sp),hl 15 r - - - - h (sp+1); l (sp) ex (sp),ix 15 - - - - ixh (sp+1); ixl (sp) ex (sp),iy 15 - - - - iyh (sp+1); iyl (sp) ex af,af' 2 - - - - af af' ex de',hl 2 s - - - - if (!Altd) then de' hl else ...

Page 187

User’s manual 181 add iy,yy 4 f - - - * iy = iy + yy -- yy=bc, de, iy, sp add sp,d 4 f - - - * sp = sp + d -- d=0 to 255 and hl,de 2 fr * * l 0 hl = hl & de and ix,de 4 f * * l 0 ix = ix & de and iy,de 4 f * * l 0 iy = iy & de bool hl 2 fr * * 0 0 if (hl != 0) hl = 1, set flags to match hl bool ix 4...

Page 189

User’s manual 183 18.13 8-bit fast a register operations instruction clk a i s z v c operation cpl 2 r - - - - a = ~a neg 4 fr * * v * a = 0 - a rla 2 fr - - - * {cy,a} = {a,cy} rlca 2 fr - - - * a = {a[6,0],a[7]}; cy = a[7] rra 2 fr - - - * {a,cy} = {cy,a} rrca 2 fr - - - * a = {a[0],a[7,1]}; cy = ...

Page 190

184 rabbit 2000 microprocessor sla r 4 fr * * l * r = {r[6,0],0}; cy = r[7] sra (hl) 10 f b * * l * (hl) = {(hl)[7],(hl)[7,1]}; cy = (hl)[0] sra (ix+d) 13 f b * * l * (ix+d) = {(ix+d)[7], (ix+d)[7,1]}; cy = (ix+d)[0] sra (iy+d) 13 f b * * l * (iy+d) = {(iy+d)[7], (iy+d)[7,1]}; cy = (iy+d)[0] sra r 4...

Page 191

User’s manual 185 18.17 control instructions - jumps and calls instruction clk a i s z v c operation call mn 12 - - - - (sp-1) = pch; (sp-2) = pcl; pc = mn; sp = sp-2 djnz j 5 r - - - - b = b-1; if {b != 0} pc = pc + j jp (hl) 4 - - - - pc = hl jp (ix) 6 - - - - pc = ix jp (iy) 6 - - - - pc = iy jp ...

Page 192

186 rabbit 2000 microprocessor 18.19 privileged instructions the privileged instructions are described in this section. Privilege means that an interrupt cannot take place between the privileged instruction and the following instruction. The three instructions below are privileged. Ld sp,hl ; load t...

Page 193: 19. D

User’s manual 187 19. D ifferences r abbit vs . Z80/z180 i nstructions the rabbit is highly code compatible with the z80 and z180, and it is easy to port non i/o dependent code. The main areas of incompatibility are instructions that are concerned with i/o or particular hardware implementations. The...

Page 194

188 rabbit 2000 microprocessor the following instructions use different register names. Ld a,eir ld eir,a ; was r register ld iir,a ld a,iir ; was i register the following z80/z180 instructions have been dropped and are not supported. Alterna- tive rabbit instructions are provided. Z80/z180 instruct...

Page 195: 20. I

User’s manual 189 20. I nstructions in a lphabetical o rder w ith b inary e ncoding spreadsheet conventions altd (“a” column) symbol key flag description f altd selects alternate flags fr altd selects alternate flags and register r altd selects alternate register s altd operation is a special case i...

Page 196

190 rabbit 2000 microprocessor symbols rabbit z180 meaning b b bit select: 000 = bit 0, 001 = bit 1, 010 = bit 2, 011 = bit 3, 100 = bit 4, 101 = bit 5, 110 = bit 6, 111 = bit 7 cc cc condition code select: 00 = nz, 01 = z, 10 = nc, 11 = c d d 7-bit (signed) displacement. Expressed in two’s compleme...

Page 197

User’s manual 191 instruction byte 1 byte 2 byte 3 byte 4 clk a i s z v c adc a,(hl) 10001110 5 fr s * * v * adc a,(ix+d) 11011101 10001110 ----d--- 9 fr s * * v * adc a,(iy+d) 11111101 10001110 ----d--- 9 fr s * * v * adc a,n 11001110 ----n--- 4 fr * * v * adc a,r 10001-r- 2 fr * * v * adc hl,ss 11...

Page 198

192 rabbit 2000 microprocessor ex af,af' 00001000 2 - - - - ex de,hl 11101011 2 s - - - - ex de',hl 11100011 2 s - - - - ex de,hl' 01110110 11100011 4 s - - - - ex de',hl' 01110110 11100011 4 s - - - - exx 11011001 2 - - - - inc (hl) 00110100 8 f b * * v - inc (ix+d) 11011101 00110100 ----d--- 12 f ...

Page 199

User’s manual 193 ld a,(bc) 00001010 6 r s - - - - ld a,(de) 00011010 6 r s - - - - ld a,(mn) 00111010 ----n--- ----m--- 9 r s - - - - ld a,eir 11101101 01010111 4 fr * * - - ld a,iir 11101101 01011111 4 fr * * - - ld a,xpc 11101101 01110111 4 r - - - - ld dd,(mn) 11101101 01dd1011 ----n--- ----m---...

Page 200

194 rabbit 2000 microprocessor ldp hl,(hl) 11101101 01101100 10 - - - - ldp hl,(ix) 11011101 01101100 10 - - - - ldp hl,(iy) 11111101 01101100 10 - - - - ldp hl,(mn) 11101101 01101101 ----n--- ----m--- 13 - - - - ldp ix,(mn) 11011101 01101101 ----n--- ----m--- 13 - - - - ldp iy,(mn) 11111101 0110110...

Page 201

User’s manual 195 rr r 11001011 00011-r- 4 fr * * l * rra 00011111 2 fr - - - * rrc (hl) 11001011 00001110 10 f b * * l * rrc (ix+d) 11011101 11001011 ----d--- 00001110 13 f b * * l * rrc (iy+d) 11111101 11001011 ----d--- 00001110 13 f b * * l * rrc r 11001011 00001-r- 4 fr * * l * rrca 00001111 2 f...

Page 202

196 rabbit 2000 microprocessor.

Page 203: Ppendix

User’s manual 197 a ppendix a. A.1 the rabbit programming port the programming port provides a standard physical and electrical interface between a rabbit-based system and the dynamic c programming platform. A special interface cable and converter connects a pc serial port to the programming port. T...

Page 204

198 rabbit 2000 microprocessor a.2 use of the programming port as a diagnostic/setup port the programming port, which is already in place, can serve as a convenient communica- tions port for field setup, diagnosis or other occasional communication need (for example, as a diagnostic port). There are ...

Page 205

User’s manual 199 chronous signal suitable for the pc. Since the target controls the clock for both send and receive, the data transmission proceeds at a rate controlled by the target board under development. This scheme does not allow for an interrupt, and it is not desirable to use up an external ...

Page 206

200 rabbit 2000 microprocessor.

Page 207: Ppendix

User’s manual 201 a ppendix b. B.1 rabbit 2000 revisions since its release, the rabbit 2000 microprocessor has gone through a number of revisions. The revisions reflect bug fixes, improvements, and the introduction of new features. All rabbit 2000 revisions are pin-compatible and transparently repla...

Page 208

202 rabbit 2000 microprocessor 3. Second revision (rabbit 2000b) —identified by iq4t on the package. This version began shipping in samples and very low volume to select customers having problems with emi in april, 2002. This part was phased out and will be replaced by the rabbit 2000c for volume or...

Page 209

User’s manual 203 b.2 discussion of fixes and improvements table b-1 lists bug fixes, improvements, and additions for the various revisions of the rabbit 2000. Table b-1. Summary of rabbit 2000 fixes and improvements description rabbit 2000 (iq2t) rabbit 2000a (iq3t) rabbit 2000b (iq4t) rabbit 2000c...

Page 210

204 rabbit 2000 microprocessor b.2.1 rabbit internal i/o registers table b-2 summarizes the reset state of the new i/o registers added in the rabbit 2000 revisions. Table b-2. Reset state of rabbit 2000x i/o registers register name present in rev. Mnemonic i/o address r/w reset global clock modulato...

Page 211

User’s manual 205 b.2.2 revision-level id register two read-only registers are provided to allow software to identify the rabbit microproces- sor and recognize the features and capabilities of the chip. Five bits in each of these regis- ters are unique to each version of the chip. One register ident...

Page 212

206 rabbit 2000 microprocessor table b-5. Global revision register global revision register (grev) (address = 0x2f) bit(s) value description 7 0 program fetch as a function of the smode pins. (read only) 1 ignore the smode pins program fetch function. 6:5 read these bits report the state of the smod...

Page 213

User’s manual 207 b.2.3 serial port changes two features were added to the rabbit 2000 serial port hardware in revisions a–c to improve and simplify asynchronous serial and clocked serial communication. Asynchronous serial port in the asynchronous transmission mode, serial data are transmitted in th...

Page 214

208 rabbit 2000 microprocessor synchronous serial port to initiate basic sending or receiving in the clocked serial mode, a command must be issued by writing to bits (7,6) of the control register for each byte sent or received. There is one command is to send a byte, and a different command to recei...

Page 215

User’s manual 209 b.2.4 improved battery-backup circuit improvements were made in revisions a–c to reduce the internal power consumption of the rtc circuit. In addition, external circuitry was designed to further reduce power con- sumption by the overall oscillator circuit in board-level products ba...

Page 216

210 rabbit 2000 microprocessor the gate input and allow the oscillator to operate at a lower voltage. This oscillator will start at about 1.2 v and operate down to about 0.75 v. The 47 k Ω resistor limits the short- circuit current when the cmos gate is switching, and thus limits the overall current...

Page 217

User’s manual 211 b.2.5 added support for instruction/data split this option is available on revisions a–c. Code generated for the rabbit 2000a will run on the rabbit 2000b or 2000c, but not vice versa. The separate i & d space allows the root segment and the data segment, normally the first 52k of ...

Page 218

212 rabbit 2000 microprocessor the mmidr register shown in table b-9 is used to enable and configure separate i & d space support in addition to the /cs1 enable option used to improve the access time of battery-backable sram. Note: bits [7:5] and [3:0] were always written with zero in the original r...

Page 219

User’s manual 213 b.2.6 write inhibit (/we0) after reset this feature, available in revisions a–c, modified the reset state of the mb0cr register to inhibit /we0. Inhibiting writes after reset prevents the processor from inadvertently writ- ing to an unprogrammed flash memory that doesn’t have the s...

Page 220

214 rabbit 2000 microprocessor b.2.10 ddcb/fdcb instruction page and wait state bug fixes four-byte instructions starting with dd-cb or fd-cb didn't work when attempted with wait states. The fetch of the byte immediately following the instruction did not have the correct num- ber of wait states inse...

Page 221

User’s manual 215 b.2.12 clock spectrum spreader module this is a feature introduced on the rabbit 3000 and migrated to revisions b and c of the rabbit 2000. The clock spectrum spreader and early memory output enable are turned on by default for the rabbit 2000c in dynamic c version 7.32 and higher....

Page 222

216 rabbit 2000 microprocessor when the spectrum spreader is engaged, the frequency is modulated, and individual clock cycles may be shortened or lengthened by an amount that depends on whether the clock doubler is engaged and whether the spectrum spreader is set to the normal or strong set- ting. T...

Page 223

User’s manual 217 unless the station is very weak, in which case the interference will be seen as noise distrib- uted over the screen. A more important change in timing is that the memory access time will be shortened. The shortening with the clock doubler enabled and zero wait states is a maximum o...

Page 224

218 rabbit 2000 microprocessor b.2.13 early memory output-enable feature the early i/o enable feature was added to the rabbit 2000c revision to relax the tight tim- ing requirements for memory access when using the clock spectrum spreader. The early i/o option extends the output enable time for the ...

Page 225: Otice

User’s manual 219 n otice to u sers rabbit semiconductor products are not authorized for use as critical components in life-support devices or systems unless a specific written agreement regarding such intended use is entered into between the customer and rabbit semiconductor prior to use. Life-supp...

Page 227: Ndex

User’s manual 221 i ndex a assembly language instructions ...... 31, 32, 33, 34 reading/writing to i/o regis- ters .............................. 170 b battery-backup circuit ......... 209 bootstrap operation ............... 88 c chip selects .......................... 213 clocks ......................

Page 228

222 rabbit 2000 microprocessor o open-drain outputs .................44 operating frequency vs. Tempera- ture ..............................153 operating frequency vs. Volt- age ...............................153 operating power estimates .......9 oscillator ..............................149 main os...

Page 229

User’s manual 223 clocked serial ports (ports a– b) ................................ 125 clocked serial timing ....... 128 controlling rs-485 driver and receiver ....................... 131 data and parity bits .......... 119 data framing/modbus ...... 135 extra stop bits, parity ....... 132 generat...

Page 230

224 rabbit 2000 microprocessor.