- DL manuals

- RadiSys

- Computer Hardware

- ATCA-4616

- Reference

RadiSys ATCA-4616 Reference

Summary of ATCA-4616

Page 1

Reference compute processing module atca-4616 atca-4618 atca-4648 march 2012 007-03446-0000

Page 2

Revision history version date description -0000 march 2012 first edition. © 2012 by radisys corporation. All rights reserved. Radisys is a registered trademark of radisys corporation. Advancedtca, atca, and picmg are registered trademarks of pci industrial computer manufacturers group. All other tra...

Page 3: Table of Contents

3 table of contents preface ................................................................................................................................................ 7 about this manual...............................................................................................................

Page 4: Table of Contents

4 table of contents intel c600 series platform controller hub (pch) .................................................................................29 ipmi controller........................................................................................................................................

Page 5: Table of Contents

5 table of contents chapter 5: troubleshooting and repair......................................................................................... 69 introduction.............................................................................................................................................

Page 6: Table of Contents

6 table of contents appendix b: ipmi commands and managed sensors .................................................................. 86 ipmi command interfaces..........................................................................................................................86 ipmi commands......

Page 7: Preface

7 preface about this manual this manual describes the atca‐46xx, a compute processing module (cpm), which is fully compliant with advancedtca ® (atca ® ). The cpm is designed to be incorporated into high availability (ha) systems such as the radisys platforms sys‐6006 and sys‐6010. Use this manual a...

Page 8: Preface

Preface 8 • software reference information. The software guide for management processors and general computing processors describes software concepts and serves as a reference for procedural and usage information. When referenced in this manual, the simplified name of software guide will be used. • ...

Page 9: Preface

Preface 9 ieee std 802.3‐2002 telecommunications and information exchange between systems — local and metropolitan area networks — specific requirements, part 3: carrier sense multiple access with collision detection (csma/cd) access method and physical layer specifications, ieee computer society, m...

Page 10: Preface

Preface 10 electrostatic discharge w arning ! This product contains static‐sensitive components and should be handled with care. Failure to employ adequate anti‐static measures can cause irreparable damage to components. Electrostatic discharge (esd) damage can result in partial or complete device f...

Page 11: Chapter

1 chapter 11 product overview introduction the atca‐46xx compute processing module (cpm) is a high‐end, general‐purpose computing module that provides multi‐core processing power and multiple data‐storage options within a single advanced telecommunications computing architecture (atca) slot. The rem...

Page 12: Product Overview

1 product overview 12 supported external interfaces the atca‐46xx cpm supports both internal and external interfaces. Internal interfaces include the buses and communication protocols that are fully contained within the cpm blade or are included within the front panel, backplane, or rtm external int...

Page 13: Product Overview

1 product overview 13 specification compliance the atca‐46xx cpm complies with the following specifications: • pci industrial computers manufacturers group (picmg) 3.0 r2.0 ecn0002 advanced telecommunications computing architecture (atca) specification • picmg 3.1 r2.0 ethernet over atca (options 1 ...

Page 14: Product Overview

1 product overview 14 product options the atca‐46xx cpm has the following product options: • a4616‐cpu‐base ‐ the basic low‐power cpm with 10g fabric interface, dual intel xeon six core processors, and no installed memory. • a4618‐cpu‐base ‐ the basic high‐power cpm with 10g fabric interface, dual i...

Page 15: Chapter

2 chapter 15 hardware description introduction the atca‐46xx compute processing module (cpm) uses a number of hardware components to implement the functions required of an atca node. The major hardware components in the atca‐46xx cpm are as follow: • dual e5‐2400 family processors mounted in fclga13...

Page 16: Hardware Description

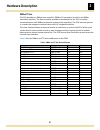

2 hardware description 16 functional block diagram figure 1 is a functional block diagram that indicates major hardware components of the cpm. Figure 1. Atca-46xx functional block diagram x8 (gen 3) 1000base-t to base interface 40g-kr4,10g-kr, 10g-kx4,1000base-kx to fabric interface serial to rtm us...

Page 17: Hardware Description

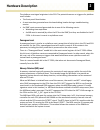

2 hardware description 17 atca-46xx front panel components the following sections use text, figures, and lists to identify the physical features of the cpm. Figure 2 shows the cpm front panel and calls out the major features. Figure 2. Front panel components thumbscrew ejector latch hdd led oos led ...

Page 18: Hardware Description

2 hardware description 18 front panel connectors there are connectors for four separate interfaces on the front panel. Plugging into the connectors is straightforward, but the underlying interfaces need some explanation. The serial (com) rj45 connector is an rs232 serial interface with the pinout li...

Page 19: Hardware Description

2 hardware description 19 front panel leds the front panel leds can be separated into two major groups; the edge leds along the left (bottom) edge of the front panel and the base/fabric channel status leds. Table 2 describes the status and activity leds along the left (bottom) edge of the front pane...

Page 20: Hardware Description

2 hardware description 20 table 3 lists the meanings assigned to the light color/activity of each base/fabric led. Note: the fabric channel leds can be either green or amber when linked or indicating activity at 10 gbps. This is because in one configuration 10 gbps is the low range output from the c...

Page 21: Hardware Description

2 hardware description 21 rear panel connectors the cpm supports e‐key control by describing its backplane interfaces to the shelf manager. Alignment keys the cpm implements the k1 and k2 alignment blocks at the top of zone 2 and zone 3, as required by the picmg 3.0 specification. The zone 2 alignme...

Page 22: Hardware Description

2 hardware description 22 zone 3 connectors the cpm includes the standard zone 3 backplane interface to provide connectivity to an optional rtm, such as the atca‐5400. This interface consists of two connectors: j30 for common and maintenance signals, and j31 for serdes (serialization/deserialization...

Page 23: Hardware Description

2 hardware description 23 atca-46xx board components during normal operation the cpm board components are covered by the cpm cooling shroud sheet metal (side panel). This sheet metal must be removed to see and gain access to removable board components, jumper blocks, or headers. Figure 4 shows the c...

Page 24: Hardware Description

2 hardware description 24 heatsinks the cpu heatsinks are called out in figure 4 . In addition to the cpu heatsinks, the intel c600 series pch, and the mellanox cx3 10/40 gbe controller each have individual heatsinks. The cpm incorporates a large heatsink covering each processor plus the additional ...

Page 25: Hardware Description

2 hardware description 25 intel® xeon® e5-2400 family processor the cpm uses two intel® xeon e5‐2400 family multi‐core, 64‐bit processors built using a 32‐ nm process. The e5‐2400 processor includes a 3‐channel memory controller, quickpath interconnect, and integrated i/o for pci express support. Th...

Page 26: Hardware Description

2 hardware description 26 integrated memory controller (imc) the integrated memory controller incorporated into each e5‐2400 family processor supports three channels of ddr3, each channel with 64 data bits and 8 ecc bits. The cpm supports up to six registered vlp rdimms per socket (two per channel) ...

Page 27: Hardware Description

2 hardware description 27 quickpath interconnect (qpi) the quickpath interconnect (qpi) provides a point‐to‐point contact between the e5‐2400 family processors. The qpi interface is 20 lanes wide under full operation and is the communication path between the cpus. Data of any width is converted to p...

Page 28: Hardware Description

2 hardware description 28 dimm memory this memory is directly addressed by the internal memory controller of each e5‐2400 family processor. Due to the board height limitations posed by the atca picmg specifications, only very low profile (vlp) dual in‐line memory module (dimm) modules are supported ...

Page 29: Hardware Description

2 hardware description 29 intel c600 series platform controller hub (pch) the intel c600 series platform controller hub (pch) provides a connection point between various i/o components and the e5‐2400 family xeon processors used on the cpm. The pch provides controllers for the following interfaces: ...

Page 30: Hardware Description

2 hardware description 30 serial ata (sata) the pch includes two sata host controllers that provide six sata 3.0 ports. These ports support data transfer rates of 3.0 gb/s. The cpm connects two sata ports (0 and 1) for use with the optional 1.8 inch micro sata ssd drives that can be installed in an ...

Page 31: Hardware Description

2 hardware description 31 smbus/i 2 c bus the pch provides an smbus host controller (smbus 2.0 compliant) as well as an smbus secondary interface. The host controller provides a mechanism for the cpu to initiate communications with smbus peripherals (master/slave interface). The pch also can operate...

Page 32: Hardware Description

2 hardware description 32 figure 5 shows the smbus/i 2 c bus mapping and lists important device addresses on the cpm. Figure 5. Atca-46xx smbus/i 2 c bus mapping and addressing ddr1_smbus ddr23_smbus spd a0: 0xa8 a1: 0xaa temp sensor a0: 0x38 a1: 0x3a spd b0: 0xa0 b1: 0xa2 c0: 0xa8 c1: 0xaa temp sen...

Page 33: Hardware Description

2 hardware description 33 management engine (me) the cpm management engine (me) uses node manager 2.0 firmware to perform power monitoring & alert, power limiting policies, thermal monitoring & alert, and power reduction tasks during boot. As described in serial peripheral interface (spi) on page 30...

Page 34: Hardware Description

2 hardware description 34 cpu complex (cc) fpga the cc fpga module performs a number of significant monitoring and interface functions on the cpm. Many of these functions are indicated in figure 1 on page 16. The following sections provide more details on the cc fpga functions. Power management and ...

Page 35: Hardware Description

2 hardware description 35 cc fpga rtm-link the rtm‐link relays the state of various control and status signals from a compatible programmable device on an rtm. The following signals are sent to the rtm for ethernet led control: • front ethernet port 0 status green • front ethernet port 0 status yell...

Page 36: Hardware Description

2 hardware description 36 ipmi fpga the intelligent platform management interface (ipmi) field programmable gate array (fpga) provides the specialized interfaces and glue logic needed between the h8 ipmc and rest of the cpm. The ipmc and the ipmi fpga provide watchdog timers to help prevent the cpm ...

Page 37: Hardware Description

2 hardware description 37 the cx3 has iscsi and pxe boot support enabled in the spi flash firmware. Iscsi and pxe cannot be enabled at the same time; the desired function must be selected in the bios setup menu. Clock synthesizer subsystem cpm uses two major components, a ck420bq and a db1900z to ge...

Page 38: Hardware Description

2 hardware description 38 the platform reset signal originates in the pch. The potential sources or triggers of a platform reset include: • the front panel reset button • a reset assertion generated over the board debug header during a troubleshooting session • an ipmc reset command generated due to...

Page 39: Hardware Description

2 hardware description 39 table 9 lists the potential sources/triggers for the mr‐reset. Though similar, these sources are slightly different from those for a platform or powergood reset. Watchdog timers the cpm uses a number of watchdog timers to prevent the board from entering an unrecoverable sta...

Page 40: Hardware Description

2 hardware description 40 ipmc watchdog timer (watchdog 2) the ipmc fpga includes a hardware watchdog timer, watchdog 2. This watchdog is enabled by default and will start running as soon as +3_3v_sus power is present and the fpga has loaded its internal flash image into its internal sram. The defau...

Page 41: Hardware Description

2 hardware description 41 figure 6. Atca-46xx power subsystem +3_3v_sus 10a fuse 10a fuse 10a fuse 10a fuse 0.1a fuse 0.1a fuse h/s led temp sensors -48v to 12v brick -48v 12v pim -48v a -48v b vrtn a vrtn b -48v +3_3v_sus +5v_sus early a early b atca zone 1 (p10) -48v a -48v b vrtn a vrtn b early a...

Page 42: Hardware Description

2 hardware description 42 power input module (pim) a power input module (pim) between the input fuses and main power brick (‐48v to 12v supply) provides input power conditioning and the following additional features: • current handling up to 300w • inrush current limit protection • integrated filter...

Page 43: Hardware Description

2 hardware description 43 • public key signature, encryption, and decryption to enable secure storage of data and digital secrets • storage of hashes (unique numbers calculated from pre‐runtime configuration information) that enable verifiable attestation of the machine configuration when booted • a...

Page 44: Hardware Description

2 hardware description 44 eusb embedded flash module (optional) the cpm supports up to two embedded usb (eusb) nand flash modules. The modules are usb 2.0 compliant and currently provide sizes from 1gb to 32gb of slc nand flash. The eusb modules have read speed support of up to 35mb/s and write spee...

Page 45: Chapter

3 chapter 45 software/firmware description introduction the cpm has the following software and firmware associated with it: • the system bios • the ipmi firmware • software/firmware update support software • operating system support software the following sections provide more information. System bi...

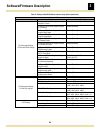

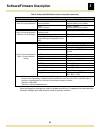

Page 46

3 software/firmware description 46 table 10. Bios setup menu hierarchy . Table 11 lists the radisys default settings for the main menu of the cpm bios setup. Top-level menu information items and sub-menus main, table 11 on page 46 • bios information • system language • memory information • access le...

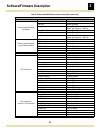

Page 47

3 software/firmware description 47 table 12 lists the radisys default settings for the advanced menu of the cpm bios setup. Table 12. Radisys default bios advanced menu setup options advanced menu submenu setup item values [default] top level: advanced menu front/rear ethernet [eeprom setting] front...

Page 48

3 software/firmware description 48 pci subsystem settings: pci express gen2 settings pci express gen2 device register settings completion timeout [default] shorter longer disabled pci express gen2 device register settings ari forwarding enabled [disabled] pci express gen2 device register settings at...

Page 49

3 software/firmware description 49 trusted computing settings: configuration security device support enabled [disabled] tpm state enabled [disabled] pending operation [none] enable take ownership disable take ownership tpm clear security device support enabled [disabled] tcm state enabled [disabled]...

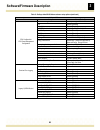

Page 50

3 software/firmware description 50 cpu configuration: cpu power management configuration power technology [disable] energy efficient custom eist enabled [disabled] turbo mode enabled [disabled] p-state coordination [hw_all] sw_all sw_any cpu c3 report enabled [disabled] cpu c6 report enabled [disabl...

Page 51

3 software/firmware description 51 sata configuration sata port[0 1] [dynamic update] sata mode disabled ide mode [achi mode] raid mode serial-ata controller 0 disabled enhanced [compatible] serial-ata controller 1 [disabled] enhanced aggressive link power management enabled [disabled] port [0 1 2 3...

Page 52

3 software/firmware description 52 some configuration settings can result in hardware conflicts. It is important to understand the hardware configuration and resource needs to prevent conflicts. Serial port console redirection com0: console redirection [enabled] disabled [dynamic update] if port is ...

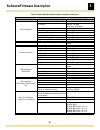

Page 53

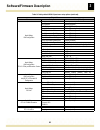

3 software/firmware description 53 table 13 lists the radisys default settings for the chipset menu of the cpm bios setup.. Table 13. Radisys default bios chipset menu setup options chipset menu submenu setup item values [default] north bridge, memory configuration total memory [dynamic update] curr...

Page 54

3 software/firmware description 54 north bridge, ioh configuration intel(r) i/oat enabled [disabled] dca support [enabled] disabled vga priority onboard / [offboard*] targetvga cpu 0 [dynamic update] gen3 equalization wa's enabled [disabled] gen3 equalization fail wa enabled [disabled] gen3 equaliza...

Page 55

3 software/firmware description 55 south bridge sb chipset configuration pch compatibility rid enabled [disabled] smbus controller [enabled] disabled periodic smi [enabled] disabled wake on lan from s5 [enabled] disabled slp_s4 assertion stretch enable [enabled] disabled slp_s4 assertion width 1-2 s...

Page 56

3 software/firmware description 56 table 14 lists the radisys default settings for the ipmi menu of the cpm bios setup.. Table 14. Radisys default bios ipmi menu setup options ipmi menu submenu setup item values [default] top level: ipmi menu bmc self test status [dynamic update] post watchdog [enab...

Page 57

3 software/firmware description 57 table 15 lists the radisys default settings for the remaining (security, boot, and exit menus) of the cpm bios setup.. Table 15. Radisys default bios security, boot, and exit menu setup options security, boot, and exit menus submenu setup item values [default] secu...

Page 58: Ras Support

3 software/firmware description 58 ras support the cpm uses reliability, availability and serviceability (ras) features to support enhanced boot reliability and reduce system downtime. The following features promote ras support: • bios protection and redundancy • memory error handling • pcie error h...

Page 59

3 software/firmware description 59 at runtime, the cpu triggers a system management interrupt (smi) when memory errors reach a preset threshold. If the runtime error logging is enabled. Then smi determines the cause, clears the error status, and reports the memory error to ipmc. Memory errors can be...

Page 60

3 software/firmware description 60 post error handling the power on self test (post) carried out by bios after startup examines the functionality of the modules present on the system. It reports any errors to ipmc in the form of platform event messages. The bios continues the boot process as long as...

Page 61: Ipmc Functions

3 software/firmware description 61 bios recovery refer to the firmware and software update instructions for the full bios image upload procedure. If the cpm bios fails boot due to flash corruption of both the primary and secondary boot flash images, the user can recover the flash bios image using a ...

Page 62: Operating System Support

3 software/firmware description 62 all upgrades can be performed from the cpm’s local cpu: • through a serial console that is directly connected to the cpm or rtm serial port. • through a remote serial console as described in serial‐over‐lan on page 65. • by a remote login to the cpm over ethernet. ...

Page 63: Chapter

4 chapter 63 operation and maintenance introduction this chapter presents the following operation and maintenance topics: • hot swap process • ipmi over lan • serial over lan • firmware and software upgrades. Hot swap of the cpm the cpm is hot swap capable and meets the hot swap requirements defined...

Page 64: Operation and Maintenance

4 operation and maintenance 64 2. Be prepared to fill in values for these variables: ipmi-over-lan basic configuration steps from the linux prompt: 1. Set the ip address for a base interface channel: rsys‐ipmitool ‐i lan ‐h ‐a none ‐t lan set ipaddr the ‐i option specifies the ipmi interface to use ...

Page 65: Operation and Maintenance

4 operation and maintenance 65 rsys‐ipmitool ‐i lan ‐h ‐a none ‐t > channel setaccess 01 ipmi=on link=on privilege=4 3. Repeat step 2 to set access to the other channel. Ipmi-over-lan troubleshooting steps 1. View the current settings for a channel: rsys‐ipmitool ‐i ‐h ‐a none ‐t lan print 2. Verify...

Page 66: Operation and Maintenance

4 operation and maintenance 66 establishing a sol session prerequisite: this procedure assumes that the required setup for ipmi‐over‐lan has been done once for this cpm. For details, see configuring ipmi‐over‐lan access on page 63. One-time sol configuration steps the following two steps configure t...

Page 67: Operation and Maintenance

4 operation and maintenance 67 sol session open steps to open a sol session from a remote computer: 1. Activate the sol console window: rsys‐ipmitool ‐i ‐h ‐a none ‐c 0 sol activate the sol session is established. 2. Perform an action (such as pressing enter) from the sol console window. The sol con...

Page 68: Operation and Maintenance

4 operation and maintenance 68 overview of firmware updates table 16 summarizes the cpm’s programmable devices and the content that can be updated. All updates can be performed from the cpm’s local cpu: • through a serial console that is directly connected to the cpm or rtm serial port. • through a ...

Page 69: Chapter

5 chapter 69 troubleshooting and repair introduction the procedures presented or referenced in this chapter detail removal and replacement of cpm field replaceable units (frus) and provide troubleshooting procedures that can be used to discover fru’s that need to be repaired or replaced. The followi...

Page 70: Troubleshooting and Repair

5 troubleshooting and repair 70 some of the multirecord area records used are: • carrier information record • carrier activation and current management record • board point‐to‐point connectivity record • carrier point‐to‐point connectivity record • carrier clock point‐to‐point connectivity record cp...

Page 71: Troubleshooting and Repair

5 troubleshooting and repair 71 cpm replacement procedures removing the cpm the following steps explain the hot‐swap procedure for replacing the cpm: 1. Read electrostatic discharge on page 10 and make sure you are adequately grounded before handling any of the modules. 2. Before replacing the cpm, ...

Page 72: Troubleshooting and Repair

5 troubleshooting and repair 72 removing the cpm board cover the cpm cooling shroud consists of the main board cover. The entire cover is attached to the board with a number of flat phillips head screws. Perform the following steps to remove the cpm main board cover: 1. Power down the cpm or activat...

Page 73: Troubleshooting and Repair

5 troubleshooting and repair 73 memory module replacement procedures note: while the atca‐46xx cpm can operate using a wide range of dimm memory combinations, at least one dimm module should be installed in each cpu dimm bank to ensure there are not boot initialization errors. Adding or replacing me...

Page 74: Troubleshooting and Repair

5 troubleshooting and repair 74 figure 9. Dimm insertion/removal 3. Hold the dimm by the edges and remove it. 4. Remove the other dimms in the same manner. To replace the dimm with a new card, follow the steps under installing dimms . 5. Screw the main board cover back into place. 6. Power up the cp...

Page 75: Troubleshooting and Repair

5 troubleshooting and repair 75 • the dimm is incorrectly installed • the dimm is faulty • the dimm installation violates the memory population rules a dimm that is not detected or enabled properly can be identified through the bios setup menu ( chipset > cpu socket 0/1 dimm information ). Mxm modul...

Page 76: Troubleshooting and Repair

5 troubleshooting and repair 76 4. Press the mxm module into the mxm connector until it is fully seated. 5. Align the mxm mounting holes with the board standoffs (nearer the cpm front panel) and secure the module with one (dssd module) or two (mxm video module) screws. 6. Reinstall the cpm cover (se...

Page 77: Troubleshooting and Repair

5 troubleshooting and repair 77 installing an eusb module perform the following steps: 1. Remove the cpm from its slot (see removing the cpm on page 71). 2. Remove the cpm cover (see removing the cpm board cover on page 72). 3. Align the first the eusb module (between the j20 and j23 connectors at t...

Page 78: Troubleshooting and Repair

5 troubleshooting and repair 78 symptoms and recommended actions table 18 lists possible troubleshooting scenarios. Look through the listed symptoms to see if any apply to your situation and follow the recommended actions for the applicable symptoms. When an action reveals the cause of the problem, ...

Page 79: Troubleshooting and Repair

5 troubleshooting and repair 79 sensor alarm troubleshooting table 38 on page 96 lists the ipmi managed sensors for the cpm. The table also provides sensor descriptions and threshold values, discrete values, or reported states that might cause the ipmc to generate an alarm or perform some other acti...

Page 80: Appendix

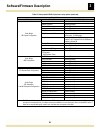

A appendix 80 specifications the radisys atca‐46xx cpm complies with or meets the standards and specifications presented in the following sections. Standards and interfaces table 19 lists the standards and interfaces that apply to the cpm. Table 19. Cpm standards and interfaces standards/interfaces ...

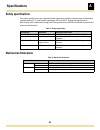

Page 81: Specifications

A specifications 81 environmental specifications radisys does not provide environmental certification testing because any meaningful emissions agency certification must include the entire system. Thus, the cpm is designed and tested to pass the environmental specifications noted below, but it is not...

Page 82: Specifications

A specifications 82 safety specifications the safety specifications are measured under laboratory ambient temperature and humidity (approximately 55c and humidity between 30% and 50%). Testing was performed in partnership with a nationally recognized testing laboratory (nrtl) accredited to provide...

Page 83: Specifications

A specifications 83 electromagnetic compatibility (emc) the esd, emc, and immunity specifications are measured with ambient temperature between 20c and 30c and relative humidity between 30% and 50%. Table 23. Electromagnetic compatibility (emc) characteristic state standard and criteria emission...

Page 84: Specifications

A specifications 84 network equipment building standard (nebs) the cpm is designed to meet the nebs requirements listed in additional compliance in addition to the standards cited that the atca‐46xx has been designed to meet, the cpm also complies with the following requirements and standards: • ets...

Page 85: Specifications

A specifications 85 mean time between failures (mtbf) the board mtbf is designed to meet or exceed 150,000 hours @ +35c per telcordia sr332 issue 2, method 1, case 3. The calculation results in table 25 were generated using the references and assumptions listed. This specification and its associated...

Page 86: Appendix

B appendix 86 ipmi commands and managed sensors ipmi command interfaces the following interfaces use ipmi command support: • i 2 c bus connections with the following links: • i 2 c bus 0 ‐ ipmb0‐a • i 2 c bus 1 ‐ ipmb0‐b • i 2 c bus 2 ‐ access to ipmc fpga, cc fpga, and rtc circuitry • i 2 c bus 3‐ ...

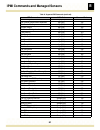

Page 87

B ipmi commands and managed sensors 87 send message app (06h) 34h get channel authentication capabilities app (06h) 38h get session challenge app (06h) 39h activate session app (06h) 3ah set session privilege level app (06h) 3bh close session app (06h) 3ch get session info app (06h) 3dh get authcode...

Page 88

B ipmi commands and managed sensors 88 add sel entry storage (0ah) 44h partial add sel entry storage (0ah) 45h clear sel storage (0ah) 47h get sel time storage (0ah) 48h set sel time storage (0ah) 49h set lan configuration parameters transport (0ch) 01h get lan configuration parameters transport (0c...

Page 89: Oem Command Descriptions

B ipmi commands and managed sensors 89 oem command descriptions special commands are available to facilitate cpm‐specific functionality. The following sections describe the cpm oem commands. Restore factory defaults command this command restores the factory default configuration and threshold parame...

Page 90

B ipmi commands and managed sensors 90 get control state command (for debug only) this command returns the current state of a control pin. Table 29 is the command description of the get control state command. Disable cfd command this command indicates to the ipmc that the cfd watchdog timer needs to...

Page 91

B ipmi commands and managed sensors 91 switch active boot flash command this command sets the current boot flash and can cause a cold reset to the x86 processor complex portion of the board if the appropriate bits in the command data are set. The command can also set the primary boot flash, which is...

Page 92

B ipmi commands and managed sensors 92 rtm reset button command this command instructs the h8 ipmi firmware to perform a cold reset. Table 34 is the command description of the get active boot flash command. Table 34. Rtm reset button oem command data type byte data field data field 1 radisys iana pe...

Page 93

B ipmi commands and managed sensors 93 set payload status command this command informs the h8 ipmi firmware the current payload processor status. The ipmi firmware may use the reported information to initiate its internal processes which are dependent on resources controllable by the onboard x86 pro...

Page 94

B ipmi commands and managed sensors 94 get payload status (for debug only) command this command returns the h8 ipmi firmware acknowledgement of the payload processor status. The bios/os may use this command to check if the ipmi firmware has finished the internal processes for the onboard x86 process...

Page 95: Managed Sensors

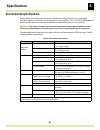

B ipmi commands and managed sensors 95 managed sensors on the cpm, the ipmc sensors monitor voltages, temperatures, control signals, and status events. For functional information, refer to ipmi controller on page 33. The sensors are described in table 38 . Types of sensors the cpm implements the fol...

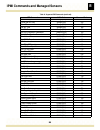

Page 96: Ipmi Sensors

B ipmi commands and managed sensors 96 ipmi sensors the cpm supports a variety of sensors, each with entries in the sensor data records (sdr). Table 38 lists the ipmi sensors supported by the cpm. Table 38. Atca-46xx ipmi managed sensors sensor # name type reading type normal reading notes 0 atca fr...

Page 97

B ipmi commands and managed sensors 97 13 enet link 1 slot or connector digital 0 or 1 0 = e1_link* not asserted 1 = e1_link* asserted 14 enet link 2 slot or connector digital 0 or 1 0 = e2_link* not asserted 1 = e2_link* asserted 15 enet link 3 slot or connector digital 0 or 1 0 = e3_link* not asse...

Page 98

B ipmi commands and managed sensors 98 33 +12v voltage threshold 12.00 lnr = 0.00 lc = 10.8 lnc = 11.4 unc = 12.6 uc = 13.2 unr = 13.8 34 +5v voltage threshold 5.00 lnr = 0.00 lc = 4.5 lnc = 4.75 unc = 5.25 uc = 5.49 unr = 5.74 35 +5v standby voltage threshold 5.00 lnr = 0.00 lc = 4.5 lnc = 4.75 unc...

Page 99

B ipmi commands and managed sensors 99 40 +1.5v pch voltage threshold 1.50 lnr = 0.00 lc = 1.35 lnc = 1.43 unc = 1.58 uc = 1.65 unr = 1.73 41 +1.2v voltage threshold 1.20 lnr = 0.00 lc = 1.08 lnc = 1.14 unc = 1.26 uc = 1.32 unr = 1.38 42 +1.1v voltage threshold 1.10 lnr = 0.00 lc = 0.99 lnc = 1.05 u...

Page 100

B ipmi commands and managed sensors 100 47 +vddq1 voltage threshold 1.50 lnr = 0.51 lc = 1.4 lnc = 1.46 unc = 1.56 uc = 1.61 unr = 1.66 48 +vtt0 voltage threshold 1.05 (snb)/1.0(i vb) lnr = 0.50 lc = 0.96 lnc = 1.00 unc = 1.10 uc = 1.12 unr = 1.16 49 +vtt1 voltage threshold 1.05 (snb)/1.0(i vb) lnr ...

Page 101

B ipmi commands and managed sensors 101 54 +vccpll0 voltage threshold 1.8(snb)/1. 7(ivb) lnr = 0.00 lc = 1.68 lnc = 1.74 unc = 1.89 uc = 1.95 unr = 1.99 55 +vccpll1 voltage threshold 1.8(snb)/1. 7(ivb) lnr = 0.00 lc = 1.68 lnc = 1.74 unc = 1.89 uc = 1.95 unr = 1.99 56 +vsa0 voltage threshold 0.85 ln...

Page 102

B ipmi commands and managed sensors 102 61 +lvtt ddr0 voltage threshold 0.675 (lvdimm) lnr = 0.50 lc = 0.63 lnc = 0.65 unc = 0.70 uc = 0.73 unr = 0.75 62 +lvtt ddr1 voltage threshold 0.675 (lvdimm) lnr = 0.50 lc = 0.63 lnc = 0.65 unc = 0.70 uc = 0.73 unr = 0.75 63 inlet temp 1 temperature threshold ...

Page 103

B ipmi commands and managed sensors 103 68 cpu0 core dts temperature threshold 25 lnr = n/a lc = n/a lnc = n/a unc = -20 uc = -13 unr = -1 69 cpu1 core dts temperature threshold 25 lnr = n/a lc = n/a lnc = n/a unc = -20 uc = -13 unr = -1 event-only sensors 90 memory memory sensor- specific n/a offse...

Page 104

B ipmi commands and managed sensors 104 92 processor processor sensor- specific n/a offset description 03h = frb2/ hang in post failure (used hang is believed to be due or related to a processor failure. Use system firmware progress sensor for other bios hangs.) 93 system firmware progress system fi...

Page 105

B ipmi commands and managed sensors 105 93 (cont.) system firmware progress (cont.) 02h = system firmware progress event data 2: 00h - unspecified. 01h - memory initialization. 02h - hard-disk initialization 03h - secondary processor(s) initialization 04h - user authentication 05h - user-initiated s...

Page 106

B ipmi commands and managed sensors 106 94 boot error boot error sensor- specific n/a offset description 00h = boot record corruption eventdata1: 0xa0 - boot record corruption eventdata2: 0x00 - currently executing application image does not match non-volatile storage designation eventdata3: 0x00 - ...

Page 107

B ipmi commands and managed sensors 107 99 failover oem failover sensor- specific n/a offset description 00h = oem failover (only applicable if redundancy is available.) eventdata1: 0 eventdata2: 0 & eventdata3: 4' failover start eventdata2: 1 & eventdata3: ff' failover complete 100 hpi event oem hp...

Page 108: Appendix

C appendix 108 pinouts and mapping the atca‐46xx cpm pinout listings apply to front panel connectors and the zone 1 and 2 backplane connectors. The onboard header pinouts apply to user‐accessible areas of the cpm board. Front panel connectors the following sections describe the pinouts for the front...

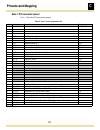

Page 109: Pinouts and Mapping

C pinouts and mapping 109 dual ethernet connectors table 41 lists the pinout for each of the front panel rj45 ethernet gbe connectors. Note that power, ground, and the led control signals are fed from the pcb and are not accessible at the connector pins. Refer to table 1 on page 18 for detailed info...

Page 110: Pinouts and Mapping

C pinouts and mapping 110 backplane interfaces backplane connectivity summary this section describes the backplane interface connectivity. Table 43 lists the backplane connectors and summarizes their usage. Table 43. Backplane connectivity summary connector channel port board usage picmg definition ...

Page 111: Pinouts and Mapping

C pinouts and mapping 111 zone 1 p10 connector pinout table 44 lists the p10 connector pinout. Table 44. Zone 1 contact assignments, p10 contact designation description mating sequence 1 reserved reserved not applicable 2 reserved reserved not applicable 3 reserved reserved not applicable 4 reserved...

Page 112: Pinouts and Mapping

C pinouts and mapping 112 zone 2 j20 connector pinout table 45 lists the j20 connector pinout. Zone 2 j23 connector pinout table 46 lists the j23 connector pinout. Table 45. Backplane connector j20 signals row interface designation ab cd ef gh 1 clks clk1a+ clk1a– clk1b+ clk1b– clk2a+ clk2a– clk2b+ ...

Page 113: Pinouts and Mapping

C pinouts and mapping 113 rtm interface pinout zone 3 j30 connector pinout table 47 lists the zone 3 j30 connector pinout. Zone 3 j31 connector pinout table 48 lists the zone 3 j31 connector pinout. Table 47. Rtm connector j30 signals row ab cd ef gh 1 +12v_rtm +12v_rtm +12v_rtm +3.3v_ipmc rtm_prsnt...

Page 114: Pinouts and Mapping

C pinouts and mapping 114 onboard switches, headers, and connectors onboard switches there are two switches on the cpm, both on the front panel, as follow: • the reset switch • the hot swap eject switch the recessed reset push button (sw1) is located in the lower half of the front panel, just above ...

Page 115: Pinouts and Mapping

C pinouts and mapping 115 5‐6 bios force recovery the bios force recovery routine will execute on every boot when this jumper is installed. 7‐8 eusb flash write protect the write protect input to installed eusb devices is asserted when this jumper is in place. 9‐10 disable unr shutdown prevents the ...

Page 116: Pinouts and Mapping

C pinouts and mapping 116 mxm connector the onboard mxm connector is used by two types of mobile pci express module (mxm) devices; a supported type a mxm 3.0 video module or the radisys dual solid state drive (dssd) mxm module. Both types of supported modules derive all input, output, and power reso...

Page 117: Pinouts and Mapping

C pinouts and mapping 117 the dssd mxm module uses available power and other signals on the mxm connector that do not interfere with any video modules that might also supported on the connector. 71 gnd 72 pe3_cpu0_tx_dn 215 gnd 216 gnd 73 pe3_cpu0_rx_c_dn 74 pe3_cpu0_tx_dp 217 nc 218 nc 75 pe3_cpu0_...

Page 118: Pinouts and Mapping

C pinouts and mapping 118 dual micro sas connector a dual stacked micro‐sas connector is included on the sdds mxm module to support the installation of two 1.8" micro sata ssd drives. Table 51 lists the pinout for the dual micro sas connectors. Table 51. Dual micro sas connector pinout lower pins si...

Page 119: Pinouts and Mapping

C pinouts and mapping 119 eusb connector there are two embedded universal serial bus (eusb) connectors located between the j20 and j23 backplane connectors at the back edge of the cpm. These connectors can accept one or two dual stackable eusb flash modules. Table 52 lists the pinout for each of the...