- DL manuals

- Xilinx

- Microphone system

- HDMI 1.4

- Product Manual

Xilinx HDMI 1.4 Product Manual

Summary of HDMI 1.4

Page 1

Hdmi 1.4/2.0 transmitter subsystem v3.0 logicore ip product guide vivado design suite pg235 october 4, 2017.

Page 2

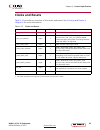

Hdmi 1.4/2.0 tx subsystem 2 pg235 october 4, 2017 www.Xilinx.Com table of contents ip facts chapter 1: overview applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 unsupported features. . . . . . ....

Page 3

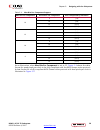

Hdmi 1.4/2.0 tx subsystem 3 pg235 october 4, 2017 www.Xilinx.Com appendix b: debugging finding help on xilinx.Com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 debug tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 4: Introduction

Hdmi 1.4/2.0 tx subsystem 4 pg235 october 4, 2017 www.Xilinx.Com product specification introduction the hdmi 1.4/2.0 transmitter subsystem is a hierarchical ip that bundles a collection of hdmi® tx ip sub-cores and outputs them as a single ip. It is an out-of-the-box ready-to-use hdmi 1.4/2.0 transm...

Page 5: Applications

Hdmi 1.4/2.0 tx subsystem 5 pg235 october 4, 2017 www.Xilinx.Com chapter 1 overview the hdmi 1.4/2.0 transmitter subsystem is a feature-rich soft ip incorporating all the necessary logic to properly interface with phy layers and provide hdmi® encoding functionality. The subsystem is a hierarchical i...

Page 6: License Checkers

Hdmi 1.4/2.0 tx subsystem 6 pg235 october 4, 2017 www.Xilinx.Com chapter 1: overview licensing and ordering information license checkers if the ip requires a license key, the key must be verified. The vivado® design tools have several license checkpoints for gating licensed ip through the flow. If t...

Page 7: Introduction

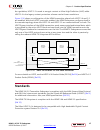

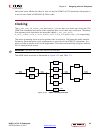

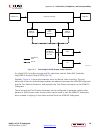

Hdmi 1.4/2.0 tx subsystem 7 pg235 october 4, 2017 www.Xilinx.Com chapter 2 product specification this chapter includes a description of the subsystem and details about the performance and resource utilization. Introduction because the hdmi 1.4/2.0 transmitter subsystem is hierarchically packaged, yo...

Page 8

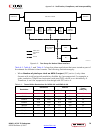

Hdmi 1.4/2.0 tx subsystem 8 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification the hdmi tx subsystem has a built-in capability to optionally support both hdcp 1.4 and hdcp 2.2 encryption. Figure 2-2 shows the internal structure of the hdmi tx subsystem when axi4-stream video inter...

Page 9

Hdmi 1.4/2.0 tx subsystem 9 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification the data width of the video interface is configured in the vivado ide by setting the number of pixels per clock on video interface and the max bits per component parameters. The audio interface is a 32-...

Page 10: Display Data Channel (Ddc)

Hdmi 1.4/2.0 tx subsystem 10 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification and jitter. When hdmi tx subsystem is used in dvi mode, the acr inputs are ignored. You can decide to leave them open or connect them to some fix values (for example, connecting acr_cts , acr_n , and a...

Page 11: Infoframes

Hdmi 1.4/2.0 tx subsystem 11 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification infoframes there are two basic infoframes expected in any hdmi system, which are auxiliary video information (avi) infoframe and audio infoframe. Both are handled by the hdmi tx subsystem drivers. The ...

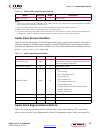

Page 12

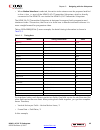

Hdmi 1.4/2.0 tx subsystem 12 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification notes: 1. Ecc is calculated in hdmi 1.4/2.0 transmitter subsystem core. Therefore, must construct hb0…hb2, and pb0, pb1…pb26, pb27 according to hdmi specs in the software. 2. When calculating the check...

Page 13

Hdmi 1.4/2.0 tx subsystem 13 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification for those packet types not highlighted, a generic api function is available in hdmi tx subsystem driver to support it from user application. You must prepare the complete packet (including calculating ...

Page 14

Hdmi 1.4/2.0 tx subsystem 14 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification limitations only limited fields are supported in current implementation. The supported fields are highlighted in yellow with respective to the packet type. General control packet: pixel packing phase a...

Page 15

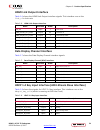

Hdmi 1.4/2.0 tx subsystem 15 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification avi infoframe color space and vic information are retrieved from video stream and sent through avi infoframe. Other fields are not updated and remain as zero always. X-ref target - figure 2-8 send feed...

Page 16: Hdcp

Hdmi 1.4/2.0 tx subsystem 16 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification audio infoframe only number of channels are set for audio infoframe and it is hard-coded to 2 in the hdmi tx subsystem driver. Other fields are not updated and remain as zero always. Hdcp as part of th...

Page 17: Standards

Hdmi 1.4/2.0 tx subsystem 17 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification as a guideline, hdcp 2.2 is used to encrypt content at ultra-high definition (uhd) while hdcp 1.4 is the legacy content protection scheme used at lower resolutions. Figure 2-10 shows a configuration of...

Page 18: Maximum Frequencies

Hdmi 1.4/2.0 tx subsystem 18 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification the xilinx hdcp 2.2 is compliant with the hdcp 2.2 specification entitled high-bandwidth digital content protection, mapping hdcp to hdmi, revision 2.2, issued by digital content protection (dcp) llc [...

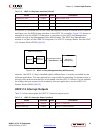

Page 19: Port Descriptions

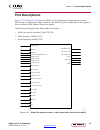

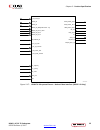

Hdmi 1.4/2.0 tx subsystem 19 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification port descriptions figure 2-11 to figure 2-14 show the hdmi 1.4/2.0 transmitter subsystem ports when axi4-stream is selected as video interface. The video_in port is expanded in the figure to show the d...

Page 20

Hdmi 1.4/2.0 tx subsystem 20 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification x-ref target - figure 2-12 figure 2 ‐ 12: hdmi tx subsystem pinout – axi4-stream video interface (hdcp 1.4 only) 6b$;,b&38b,1 $8',2b,1 9,'(2b,1 6%b67$786b,1 vbd[lbfsxbdfon vbd[lbfsxbduhvhwq vbd[lvbdxgl...

Page 21

Hdmi 1.4/2.0 tx subsystem 21 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification x-ref target - figure 2-13 figure 2 ‐ 13: hdmi tx subsystem pinout – axi4-stream video interface (hdcp 2.2 only) 6b$;,b&38b,1 $8',2b,1 9,'(2b,1 6%b67$786b,1 vbd[lbfsxbdfon vbd[lbfsxbduhvhwq vbd[lvbdxgl...

Page 22

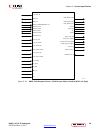

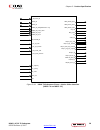

Hdmi 1.4/2.0 tx subsystem 22 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification figure 2-15 to figure 2-18 show the hdmi 1.4/2.0 transmitter subsystem ports when native video is selected as video interface. The video_in port is expanded in the figure to show the detail native vide...

Page 23

Hdmi 1.4/2.0 tx subsystem 23 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification x-ref target - figure 2-15 figure 2 ‐ 15: hdmi tx subsystem pinout – native video interface (no hdcp) s_axi_cpu_in audio_in video_in sb_status_in s_axi_cpu_aclk s_axi_cpu_aresetn s_axis_audio_aclk s_ax...

Page 24

Hdmi 1.4/2.0 tx subsystem 24 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification x-ref target - figure 2-16 figure 2 ‐ 16: hdmi tx subsystem pinout – native video interface (hdcp 1.4 only) 6b$;,b&38b,1 $8',2b,1 9,'(2b,1 6%b67$786b,1 vbd[lbfsxbdfon vbd[lbfsxbduhvhwq vbd[lvbdxglrbdfo...

Page 25

Hdmi 1.4/2.0 tx subsystem 25 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification x-ref target - figure 2-17 figure 2 ‐ 17: hdmi tx subsystem pinout – native video interface (hdcp 2.2 only) s_axi_cpu_in audio_in video_in sb_status_in s_axi_cpu_aclk s_axi_cpu_aresetn s_axis_audio_acl...

Page 26

Hdmi 1.4/2.0 tx subsystem 26 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification x-ref target - figure 2-18 figure 2 ‐ 18: hdmi tx subsystem pinout – native video interface (hdcp 1.4 and hdcp 2.2) s_axi_cpu_in audio_in video_in sb_status_in s_axi_cpu_aclk s_axi_cpu_aresetn s_axi_au...

Page 27: Cpu Interface

Hdmi 1.4/2.0 tx subsystem 27 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification cpu interface table 2-1 shows the axi4-lite control interface signals. This interface is an axi4-lite interface and runs at the s_axi_cpu_aclk clock rate. Control of the subsystem is only supported thr...

Page 28: Video Input Stream Interface

Hdmi 1.4/2.0 tx subsystem 28 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification video input stream interface this hdmi 1.4/2.0 transmitter subsystem is supporting two types of video input stream interfaces, which eventually is mapped to hdmi 1.4/2.0 transmitter subsystem video_in ...

Page 29: Audio Input Stream Interface

Hdmi 1.4/2.0 tx subsystem 29 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification audio input stream interface table 2-4 shows the signals for axi4-stream audio input streaming interfaces. The audio interface transports 24-bits audio samples in the iec 60958 format. A maximum of eig...

Page 30

Hdmi 1.4/2.0 tx subsystem 30 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification bits wide. The valid signal is driven high when the cts and n parameters are stable. For more information, see chapter 7 of the hdmi 1.4 specification [ref 12] . On the rising edge of the valid signal,...

Page 31: Hdmi Link Output Interface

Hdmi 1.4/2.0 tx subsystem 31 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification hdmi link output interface table 2-6 shows the hdmi link output interface signals. This interface runs at the link_clk clock rate. Data display channel interface table 2-7 shows the data display channe...

Page 32: Hdcp 2.2 Interrupt Outputs

Hdmi 1.4/2.0 tx subsystem 32 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification for the hdcp 1.4 transmitter, an hdcp key management module is needed, which is able to send keys over the axi4-stream interface to the hdcp 1.4 controller. Figure 2-19 shows an example of how the hdmi...

Page 33

Hdmi 1.4/2.0 tx subsystem 33 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification miscellaneous signals with axi4-stream video interface table 2-10 shows the miscellaneous signals with axi4-stream video interface selected. 1. The hot plug detect (hpd) signal is driven by an hdmi sin...

Page 34

Hdmi 1.4/2.0 tx subsystem 34 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification 1. The hot plug detect (hpd) signal is driven by an hdmi sink and asserted when the hdmi cable is connected to notify the hdmi source of the presence of an hdmi sink. In most cases, the hdmi sink is si...

Page 35: Clocks And Resets

Hdmi 1.4/2.0 tx subsystem 35 pg235 october 4, 2017 www.Xilinx.Com chapter 2: product specification clocks and resets table 2-12 provides an overview of the clocks and resets. See clocking and resets in chapter 3 for more information. Table 2 ‐ 12: clocks and resets name direction width description s...

Page 36: General Design Guidelines

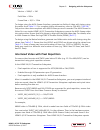

Hdmi 1.4/2.0 tx subsystem 36 pg235 october 4, 2017 www.Xilinx.Com chapter 3 designing with the subsystem this chapter includes guidelines and additional information to facilitate designing with the subsystem. General design guidelines the subsystem connects to other hardware components to construct ...

Page 37: Video Input Stream Interface

Hdmi 1.4/2.0 tx subsystem 37 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem example, if you intend to send out 8 channel audio, then you must set audio channel number to 8 in hdmi 1.4/2.0 transmitter subsystem driver. Then, the corresponding audio data must be prepared ...

Page 38

Hdmi 1.4/2.0 tx subsystem 38 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem when the parameter, max bits per component , is set to 12, video formats with actual bits per component larger than 12 is truncated to the max bits per component. The remaining least significant...

Page 39

Hdmi 1.4/2.0 tx subsystem 39 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem as an illustration, when max bits per component is set to 12, figure 3-4 shows the data format for quad pixels per clock to be fully compliant with the axi4-stream video protocol. A data format ...

Page 40

Hdmi 1.4/2.0 tx subsystem 40 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem the video interface can also transport quad and dual pixels in the yuv420 color space. However the current data format is not complaint with the axi4-stream video protocol. Figure 3-6 and figure...

Page 41

Hdmi 1.4/2.0 tx subsystem 41 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem similarly, for yuv 4:2:0 deep color (10, 12, or 16 bits), the data representation is the same as shown in figure 3-6 and figure 3-7 . The only difference is that each component carries more bits...

Page 42: Interlaced Video

Hdmi 1.4/2.0 tx subsystem 42 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem therefore, a remapping feature is added to hdmi 1.4/2.0 transmitter subsystem to convert hdmi native video into axi4-stream video. Note: for rgb/yuv444/yuv422 formats, video data is directly map...

Page 43

Hdmi 1.4/2.0 tx subsystem 43 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem • when native interface is selected, the native video stream must be prepared and fed to the video_in port of the hdmi 1.4/2.0 transmitter subsystem, which is directly connected to the hdmi tx c...

Page 44

Hdmi 1.4/2.0 tx subsystem 44 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem vactive = 1080/2 = 540 field rate = 50hz frame rate = 50/2 = 25hz to design using the axi4-stream interface, generate two fields of video with timing using the values from table 3-2 . For comple...

Page 45: Clocking

Hdmi 1.4/2.0 tx subsystem 45 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem each pixel twice. When the video is sent out by the hdmi 1.4/2.0 transmitter subsystem, it is sent as two fields of 1440x240 @ 30hz video. Clocking the s_axi_cpu_in , video_out , and audio_out c...

Page 46

Hdmi 1.4/2.0 tx subsystem 46 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem for example, 1080p60, 12bpc, and 2ppc are used to show how all the clocks are derived. Table 3 ‐ 3: clocking hdmi clocking clock function freq/rate example (1) tmds clock source synchronous cloc...

Page 47

Hdmi 1.4/2.0 tx subsystem 47 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem pixel clock represents the total number of pixels need to be sent every second. Therefore, pixel clock = htotal × vtotal × frame rate =2200 x 1125 x 60 =148,500,000 = 148.5mhz link clock = (data...

Page 48: Resets

Hdmi 1.4/2.0 tx subsystem 48 pg235 october 4, 2017 www.Xilinx.Com chapter 3: designing with the subsystem ° when axi4-stream is selected, the video stream is sent to hdmi tx subsystem through video interface in axi4-stream format running at axis_video_aclk. The axi4-stream is then processed and conv...

Page 49

Hdmi 1.4/2.0 tx subsystem 49 pg235 october 4, 2017 www.Xilinx.Com chapter 4 design flow steps this chapter describes customizing and generating the subsystem, constraining the subsystem, and the simulation, synthesis and implementation steps that are specific to this ip subsystem. More detailed info...

Page 50: Top Level Tab

Hdmi 1.4/2.0 tx subsystem 50 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps 3. Click on the ip name and press the enter key on your keyboard or double click on the ip name. 4. Double-click the selected ip block or select the customize block command from the right-click menu. For d...

Page 51

Hdmi 1.4/2.0 tx subsystem 51 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps include hdcp 2.2 encryption : this option enables hdcp 2.2 encryption. Max bits per component : this option selects the maximum bits per component. The allowable options are, 8, 10, 12 or 16 bits. This par...

Page 52: Video Bridge Tab

Hdmi 1.4/2.0 tx subsystem 52 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps video bridge tab the video bridge tab is shown in figure 4-2 . The parameters on the video bridge tab are as follows: hysteresis level : allowable range: 0—1023. Defines the “cushion” level of the frame bu...

Page 53: Example Design Tab

Hdmi 1.4/2.0 tx subsystem 53 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps example design tab the example design tab is shown in figure 4-3 . Design topology : allows you to choose the topology of example design to be generated. The allowable options are pass-through and tx only....

Page 54

Hdmi 1.4/2.0 tx subsystem 54 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps video phy controller setting section : allows the configuration of the transmitter pll type and receiver pll type to the video phy controller prior generating the example design. It also allows user to sel...

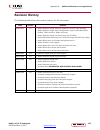

Page 55: User Parameters

Hdmi 1.4/2.0 tx subsystem 55 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps user parameters table 4-1 shows the relationship between the fields in the vivado ide and the user parameters (which can be viewed in the tcl console). Table 4 ‐ 1: vivado ide parameter to user parameter r...

Page 56: Output Generation

Hdmi 1.4/2.0 tx subsystem 56 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps output generation for details, see the vivado design suite user guide: designing with ip (ug896) [ref 16] . Fifo depth c_addr_width 1024 32 32 1024 1024 2048 2048 4096 4096 8192 8192 example design design ...

Page 57: Constraining The Subsystem

Hdmi 1.4/2.0 tx subsystem 57 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps constraining the subsystem this section contains information about constraining the subsystem in the vivado design suite. Required constraints there are clock frequency constraints for the s_axi_cpu_aclk ,...

Page 58: Clock Frequencies

Hdmi 1.4/2.0 tx subsystem 58 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps clock frequencies the axi4-lite cpu clock must run at 100 mhz. See clocking in chapter 3 for more information. Clock management this section is not applicable for this ip subsystem. Clock placement this se...

Page 59: Simulation

Hdmi 1.4/2.0 tx subsystem 59 pg235 october 4, 2017 www.Xilinx.Com chapter 4: design flow steps simulation simulation of the subsystem is not supported. Synthesis and implementation for details about synthesis and implementation, see the vivado design suite user guide: designing with ip (ug896) [ref ...

Page 60: Summary

Hdmi 1.4/2.0 tx subsystem 60 pg235 october 4, 2017 www.Xilinx.Com chapter 5 example design this chapter contains step-by-step instructions for generating an hdmi example design from the hdmi 1.4/2.0 transmitter subsystem by using vivado® flow. Summary hdmi 1.4/2.0 transmitter subsystem allows users ...

Page 61: Hardware

Hdmi 1.4/2.0 tx subsystem 61 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design this chapter covers the design considerations of a high-definition multimedia interface (hdmi™) 2.0 implementation using the performance features of these xilinx® logicore™ ips: • hdmi 1.4/2.0 with hdcp 1.4/2...

Page 62

Hdmi 1.4/2.0 tx subsystem 62 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design the vphy controller core has been configured for the hdmi application that allows transmission and reception (optional) of hdmi video/audio to and from the hdmi 2.0 daughter card or on-board hdmi 2.0 circuitr...

Page 63

Hdmi 1.4/2.0 tx subsystem 63 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design in pass-through mode, the vphy controller core recovers the high-speed serial video stream, converts it to parallel data streams, forwards it to the hdmi_rx_ss core, which extracts the video and audio streams...

Page 64

Hdmi 1.4/2.0 tx subsystem 64 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design through a customized audio generation block. The two axi streams eventually reach the hdmi_tx_ss core, which converts the axi video and audio streams back to an hdmi stream before being transmitted by the vph...

Page 65: Example Design Specifics

Hdmi 1.4/2.0 tx subsystem 65 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design example design specifics in addition to the video phy controller, hdmi transmitter subsystem and hdmi receiver subsystem core, the complete example design includes the following cores: • microblaze or zynq or...

Page 66: Running The Example Design

Hdmi 1.4/2.0 tx subsystem 66 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design • aud_pat_gen (custom ip) • hdmi_acr_ctrl (custom ip) running the example design 1. Open the vivado design suite and create a new project. 2. In the pop-up window, press next until you get to the page to sele...

Page 67

Hdmi 1.4/2.0 tx subsystem 67 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design ° you can rename the ip component name, which is used as example design project name. 6. Configure hdmi 1.4/2.0 transmitter subsystem, then click ok . X-ref target - figure 5-8 send feedback.

Page 68

Hdmi 1.4/2.0 tx subsystem 68 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design the generate output products dialog box appears. 7. Click on generate . A. You may optionally click skip if you just want to generate the example design. 8. Right click on the hdmi 1.4/2.0 transmitter subsyst...

Page 69

Hdmi 1.4/2.0 tx subsystem 69 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design 10. Export hardware to prepare for sdk example design flow ( file->export->export hardware ). 11. Click ok . (use the default export location for the example design.) 12. Launch sdk ( file->launch sdk ). 13. ...

Page 70: Hdcp Key Utility

Hdmi 1.4/2.0 tx subsystem 70 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design refer to table 5-1 to select the respective application. The example application is built successfully. The .Elf is ready to use. Hdcp key utility an optional hdcp_key_utility application software is availabl...

Page 71

Hdmi 1.4/2.0 tx subsystem 71 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design 1. Import example from sdk and choose hdcp_key_utility. 2. Open hdcp_key_utility.C from the sdk project. 3. The arrays hdcp22lc128, hdcp22key, hdcp14key1, and hdcp14key2 hold the hdcp keys and are empty. Fill...

Page 72

Hdmi 1.4/2.0 tx subsystem 72 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design note: the facsimile keys given in hdcp 1.4 spec are already in little-endian format, so byte swap is not needed when using them for test purpose. The final result should be a 328 byte hdcp 1.4 keyset. Formatt...

Page 73

Hdmi 1.4/2.0 tx subsystem 73 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design xsdb% target -set 3 7. Download the software .Elf to the fpga. Xsdb% dow ./v_hdmi_tx_ss_0_ex.Sdk/_xhdmi_example_1/ debug/_xhdmi_example_1.Elf 8. Run the software. Xsdb% stop xsdb% rst xsdb% con 9. Exit the xs...

Page 74

Hdmi 1.4/2.0 tx subsystem 74 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design 3. Open a terminal window (115200, 8, n, 1) and set the com port to the one communicating with the kcu105 board system controller. 4. After the uart terminal is connected, power cycle the kcu105 board to refr...

Page 75

Hdmi 1.4/2.0 tx subsystem 75 pg235 october 4, 2017 www.Xilinx.Com chapter 5: example design choose low in example design (according to board design). • hdcp 1.4/2.2 is enabled by default in example design application software. Removed uart option to enable hdcp 1.4 or hdcp 2.2. • auto switching has ...

Page 76: Interoperability

Hdmi 1.4/2.0 tx subsystem 76 pg235 october 4, 2017 www.Xilinx.Com appendix a verification, compliance, and interoperability interoperability interoperability tests for the hdmi 1.4/2.0 transmitter subsystem have been conducted with the following hardware setup. Hardware testing the hdmi 1.4/2.0 tran...

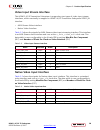

Page 77: Video Resolutions

Hdmi 1.4/2.0 tx subsystem 77 pg235 october 4, 2017 www.Xilinx.Com appendix a: verification, compliance, and interoperability • samsung uhdtv (ue40hu6900s) • murideo video analyser / six-a • dell p2415q • philips 288p6ljeb • lg 27mu67 video resolutions figure a-1 shows the hardware setup for axi4-str...

Page 78

Hdmi 1.4/2.0 tx subsystem 78 pg235 october 4, 2017 www.Xilinx.Com appendix a: verification, compliance, and interoperability for video phy controller settings and pll selections, see the video phy controller logicore ip product guide (pg230) [ref 24] . Similarly, figure a-2 shows the hardware setup ...

Page 79

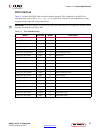

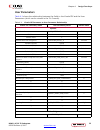

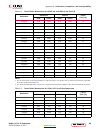

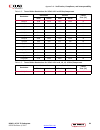

Hdmi 1.4/2.0 tx subsystem 79 pg235 october 4, 2017 www.Xilinx.Com appendix a: verification, compliance, and interoperability table a-1 , table a-2 , and table a-3 show the video resolutions that were tested as part of the release for different video formats. The following limitations apply: • when n...

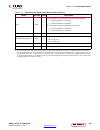

Page 80

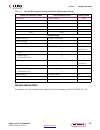

Hdmi 1.4/2.0 tx subsystem 80 pg235 october 4, 2017 www.Xilinx.Com appendix a: verification, compliance, and interoperability 1080p24 2750 1920 1125 1080 24 1080p25 2640 1920 1125 1080 25 1080p30 2200 1920 1125 1080 30 1080p50 2640 1920 1125 1080 50 1080p60 2200 1920 1125 1080 60 1080p120 2200 1920 1...

Page 81

Hdmi 1.4/2.0 tx subsystem 81 pg235 october 4, 2017 www.Xilinx.Com appendix a: verification, compliance, and interoperability 1080p25 2640 1920 1125 1080 25 1080p30 2200 1920 1125 1080 30 1080p50 2640 1920 1125 1080 50 1080p60 2200 1920 1125 1080 60 2160p24 5500 3840 2250 2160 24 2160p25 5280 3840 22...

Page 82: Finding Help On Xilinx.Com

Hdmi 1.4/2.0 tx subsystem 82 pg235 october 4, 2017 www.Xilinx.Com appendix b debugging this appendix includes details about resources available on the xilinx support website and debugging tools. Tip: if the ip generation halts with an error, there might be a license issue. See license checkers in ch...

Page 83: Technical Support

Hdmi 1.4/2.0 tx subsystem 83 pg235 october 4, 2017 www.Xilinx.Com appendix b: debugging • product name • tool message(s) • summary of the issue encountered a filter search is available after results are returned to further target the results. Master answer record for the hdmi 1.4/2.0 transmitter sub...

Page 84: Reference Boards

Hdmi 1.4/2.0 tx subsystem 84 pg235 october 4, 2017 www.Xilinx.Com appendix b: debugging reference boards various xilinx development boards support the hdmi 1.4/2.0 transmitter subsystem. These boards can be used to prototype designs and establish that the subsystem can communicate with the system. •...

Page 85: Interface Debug

Hdmi 1.4/2.0 tx subsystem 85 pg235 october 4, 2017 www.Xilinx.Com appendix b: debugging interface debug axi4-lite interfaces read from a register that does not have all 0s as a default to verify that the interface is functional. Output s_axi_arready asserts when the read address is valid, and output...

Page 86: Axi4-Stream Interfaces

Hdmi 1.4/2.0 tx subsystem 86 pg235 october 4, 2017 www.Xilinx.Com appendix b: debugging • the interface is enabled, and s_axi_aclken is active-high (if used). • the main subsystem clocks are toggling and that the enables are also asserted. • add axi4 lite interface to ila, and analysis data captured...

Page 87

Hdmi 1.4/2.0 tx subsystem 87 pg235 october 4, 2017 www.Xilinx.Com appendix b: debugging in the case of more than 2 channels, every 2 channels are considered as a single aes3 audio block. For example, using 8 audio channels, one audio block consists of 192*8 audio samples. For the first 8 samples of ...

Page 88: Device Drivers

Hdmi 1.4/2.0 tx subsystem 88 pg235 october 4, 2017 www.Xilinx.Com appendix c application software development device drivers the hdmi 1.4/2.0 transmitter subsystem driver abstracts the included supporting elements and provides you with an api for control. The api can be easily integrated into your a...

Page 89

Hdmi 1.4/2.0 tx subsystem 89 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development the hdmi 1.4/2.0 transmitter subsystem is a mac subsystem which works with a video phy controller (phy) to create a video connectivity system. The hdmi 1.4/2.0 transmitter subsystem is tigh...

Page 90: Usage

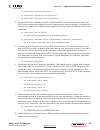

Hdmi 1.4/2.0 tx subsystem 90 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development usage the hdmi 1.4/2.0 transmitter subsystem provides a set of api functions for application code to use. On top of that, when hdmi 1.4/2.0 transmitter subsystem hardware interrupts are gen...

Page 91

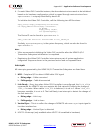

Hdmi 1.4/2.0 tx subsystem 91 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development application integration figure c-4 shows an example code on how an hdmi 1.4/2.0 transmitter subsystem can be used in your application. X-ref target - figure c-3 figure c ‐ 3: tx flow start ...

Page 92

Hdmi 1.4/2.0 tx subsystem 92 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development to integrate and use the hdmi 1.4/2.0 transmitter subsystem driver in your application, the following steps must be followed: 1. Include the subsystem header file xv_hdmitxss.H that defines...

Page 93

Hdmi 1.4/2.0 tx subsystem 93 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development to initialize the subsystem, call the following two api functions: xv_hdmitxss_config* xv_hdmitxss_lookupconfig(u32 deviceid); int xv_hdmitxss_cfginitialize(xv_hdmitxss *instanceptr, xv_hdm...

Page 94

Hdmi 1.4/2.0 tx subsystem 94 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development ° xv_hdmitxss_hdcpintrhandler ° xv_hdmitxss_hdcptimerintrhandler ° xv_hdmitxss_hdcp22timerintrhandler 4. Set the hdcp user callback functions. These callback functions are used to hook into...

Page 95

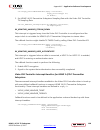

Hdmi 1.4/2.0 tx subsystem 95 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development ° xv_hdmitxss_hdcpisauthenticated ° xv_hdmitxss_hdcpisinprogress 9. When authentication is successful, the application is allowed to enable encryption. The enablement of encryption can happ...

Page 96

Hdmi 1.4/2.0 tx subsystem 96 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development to integrate and use the video phy controller for hdmi 1.4/2.0 transmitter subsystem in the application code, the following steps must be followed: 1. Include the subsystem header file xvph...

Page 97

Hdmi 1.4/2.0 tx subsystem 97 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development 4. For each video phy controller instance, the above data structure needs to be initialized based on its hardware configuration, which is passed through meta-structure from xparameters.H un...

Page 98

Hdmi 1.4/2.0 tx subsystem 98 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development 5. Hdcp 1.4 timer interrupt (only available when hdcp 1.4 is enabled in hardware) 6. Hdcp 2.2 timer interrupt (only available when hdcp 2.2 is enabled in hardware) application callback func...

Page 99

Hdmi 1.4/2.0 tx subsystem 99 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development xv_hdmitxss_handler_connect this interrupt is triggered every time when an hdmi tx cable connection or disconnection (hpd level transition) occurs. The callback function needs to perform th...

Page 100

Hdmi 1.4/2.0 tx subsystem 100 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development void xvphy_clkout1obuftdsenable(xvphy *instanceptr, xvphy_directiontype dir, u8 enable); 3. Set hdmi 1.4/2.0 transmitter subsystem sampling rate with the video phy controller tx sampling r...

Page 101

Hdmi 1.4/2.0 tx subsystem 101 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development xvphy_hdmi_handler_txinit this interrupt is triggered every time the video phy controller detects an hdmi tx reference clock changes. The callback function needs to initialize a reference ...

Page 102

Hdmi 1.4/2.0 tx subsystem 102 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development use case 4: send video stream 1. Disable the video phy controller tdms clock for hdmi 1.4/2.0 transmitter subsystem through api: xvphy_clkout1obuftdsenable(xvphy *instanceptr, xvphy_direct...

Page 103

Hdmi 1.4/2.0 tx subsystem 103 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development ° callback function registered to xvphy_hdmi_handler_txinit interrupt type is called. 7. Video phy controller hdmi tx ready interrupt is received. ° callback function registered to xvphy_h...

Page 104

Hdmi 1.4/2.0 tx subsystem 104 pg235 october 4, 2017 www.Xilinx.Com appendix c: application software development xhdmiaudgen_setpattern(&audiogen, 8, xaud_pat_mute); to update the audio channel allocation. Information can be found in table 20 in ced-861-d, under audio infoframe data byte 4. In the ap...

Page 105: Xilinx Resources

Hdmi 1.4/2.0 tx subsystem 105 pg235 october 4, 2017 www.Xilinx.Com appendix d additional resources and legal notices xilinx resources for support resources such as answers, documentation, downloads, and forums, see xilinx support . Documentation navigator and design hubs xilinx documentation navigat...

Page 106: References

Hdmi 1.4/2.0 tx subsystem 106 pg235 october 4, 2017 www.Xilinx.Com appendix d: additional resources and legal notices references these documents provide supplemental material useful with this product guide: 1. Xilinx vivado axi reference guide ( ug1037 ) 2. Kintex ultrascale fpgas data sheet: dc and...

Page 107: Revision History

Hdmi 1.4/2.0 tx subsystem 107 pg235 october 4, 2017 www.Xilinx.Com appendix d: additional resources and legal notices revision history the following table shows the revision history for this document. Date version revision 10/04/2017 3.0 • added example design topology supports (tx-only, pass-throug...

Page 108

Hdmi 1.4/2.0 tx subsystem 108 pg235 october 4, 2017 www.Xilinx.Com appendix d: additional resources and legal notices please read: important legal notices the information disclosed to you hereunder (the “materials”) is provided solely for the selection and use of xilinx products. To the maximum exte...