- DL manuals

- Xilinx

- Motherboard

- Kintex UltraScale KCU1500

- User manual

Xilinx Kintex UltraScale KCU1500 User manual

Summary of Kintex UltraScale KCU1500

Page 1

Sdaccel platform reference design user guide kintex ultrascale kcu1500 acceleration development board ug1234 (v2017.1) june 20, 2017.

Page 2: Revision History

Kintex ultrascale kcu1500 acceleration development board 2 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com revision history the following table shows the revision history for this document. Date version revision 06/20/2017 2017.1 updated to a new board platform. Title changed from ku115 to kcu1500. Re...

Page 3

Kintex ultrascale kcu1500 acceleration development board 3 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com table of contents revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 chapter 1: overview in...

Page 4

Kintex ultrascale kcu1500 acceleration development board 4 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6: install, bring-up, and use introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 ins...

Page 5: Introduction

Kintex ultrascale kcu1500 acceleration development board 5 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 1 overview introduction this document describes the platform reference design for the kintex® ultrascale™ kcu1500 acceleration development board, which when implemented in the vivado ® de...

Page 6: Platform Features

Kintex ultrascale kcu1500 acceleration development board 6 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 1: overview platform features the features of the kintex ultrascale kcu1500 acceleration development board and the xilinx acceleration kcu1500 4ddr expanded partial configuration platform...

Page 7

Kintex ultrascale kcu1500 acceleration development board 7 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 1: overview these individual steps and the scripts to run them are described in the instructions, and available from this link: reference design files , from which you can download the re...

Page 8: Introduction

Kintex ultrascale kcu1500 acceleration development board 8 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 2 platform characteristics introduction the xilinx® acceleration kcu1500 4ddr expanded partial reconfiguration platform is a high-performance acceleration platform for the sdaccel™ enviro...

Page 9

Kintex ultrascale kcu1500 acceleration development board 9 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 2: platform characteristics correspondingly, figure 2-2 shows the vivado ® device view of the implemented platform, where utilized and floorplanned static base region logic is highlighted...

Page 10

Kintex ultrascale kcu1500 acceleration development board 10 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 2: platform characteristics use with the sdaccel environment when implemented and used to produce a dsa, the hardware platform is suitable for use with the sdaccel environment and softwa...

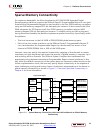

Page 11: Sparse Memory Connectivity

Kintex ultrascale kcu1500 acceleration development board 11 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 2: platform characteristics sparse memory connectivity for maximum bandwidth, the xilinx acceleration kcu1500 4ddr expanded partial reconfiguration platform connects the sdaccel opencl p...

Page 12: Support

Kintex ultrascale kcu1500 acceleration development board 12 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 2: platform characteristics stacked silicon interconnect (ssi) technology support the kintex ® ultrascale™ ku115 device uses ssi technology and contains two super logic regions (slrs). T...

Page 13

Kintex ultrascale kcu1500 acceleration development board 13 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 2: platform characteristics ° input pipeline stages on the master interfaces connected to the host are variously floorplanned to each slr, straddling the boundary to facilitate known slr...

Page 14: Introduction

Kintex ultrascale kcu1500 acceleration development board 14 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3 hardware platform introduction in this chapter, the hardware architecture of the xilinx® acceleration kcu1500 4ddr expanded partial configuration platform is described from the perspec...

Page 15

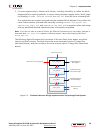

Kintex ultrascale kcu1500 acceleration development board 15 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform x-ref target - figure 3-1 figure 3-1: top-level ip integrator block diagram - default view with interfaces and wires x-ref target - figure 3-2 figure 3-2: top-level ...

Page 16: Host Connectivity

Kintex ultrascale kcu1500 acceleration development board 16 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform host connectivity the platform implements connectivity to the host computer using the xilinx dma subsystem for pci express® (pcie) ip, which contains a scatter-gathe...

Page 17

Kintex ultrascale kcu1500 acceleration development board 17 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform important: derived platforms with user modifications must not use ids identical to the reference design platform. See the sdaccel environment platform development gu...

Page 18: Memory Control

Kintex ultrascale kcu1500 acceleration development board 18 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform memory control the kintex ultrascale kcu1500 acceleration development board uses four channels of ddr4-2400 sdram at 4gb per channel for a total of 16gb. One instanc...

Page 19

Kintex ultrascale kcu1500 acceleration development board 19 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform contained within the memc sub-hierarchy of the reconfigurable expanded region as shown in the following figure, the four ddr4 ip instances are individually accessed,...

Page 20: Programmable Region

Kintex ultrascale kcu1500 acceleration development board 20 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform sdaccel opencl programmable region ip and the programmable region instantiated within the reconfigurable expanded region, the sdaccel opencl programmable region ip c...

Page 21

Kintex ultrascale kcu1500 acceleration development board 21 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform • the m00_axi through m03_axi interfaces are high-bandwidth, 512-bit axi memory-mapped master interfaces that indirectly connect to the four ddr4 ip memory controlle...

Page 22

Kintex ultrascale kcu1500 acceleration development board 22 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform • one axi interconnect instance is present per master interface, m00_axi through m03_axi . Though providing 1x1 connectivity in the platform with training kernels, t...

Page 23: Axi Interconnectivity

Kintex ultrascale kcu1500 acceleration development board 23 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform the following figure shows the advanced tab. For more information on the programmable region, the ip that defines it, and the dsa creation flow, see the sdaccel envi...

Page 24

Kintex ultrascale kcu1500 acceleration development board 24 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform • the interconnect_aximm_host instance of smartconnect ip is customized to use 1 slave interface and 5 master interfaces; a 1x5 customization, where each interface u...

Page 25

Kintex ultrascale kcu1500 acceleration development board 25 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform ° the m00_axi interface of each is connected to the corresponding ddr4 ip instance; therefore, the aclk port of each instance is driven by the connected axi interfac...

Page 26

Kintex ultrascale kcu1500 acceleration development board 26 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform application profiling and other features beyond the fundamentals of host connectivity, memory control, sdaccel system compiler support enabled by the programmable re...

Page 27: Clocking and Reset

Kintex ultrascale kcu1500 acceleration development board 27 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform after tabulation, key profiling data is transformed using an axi4-stream subset converter and buffered in an axi-stream fifo for interpretation by the sdx environmen...

Page 28

Kintex ultrascale kcu1500 acceleration development board 28 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform the xdma, axi4-lite control, kernel clock, kernel clock 2, and axi performance monitor clocks are all derived from the pcie 100 mhz differential ref_clk top-level in...

Page 29: Platform Resets

Kintex ultrascale kcu1500 acceleration development board 29 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform for example, if user kernel logic operating entirely on the kernel clock domain was constrained to the default of 300 mhz (3.333ns period) but finished implementatio...

Page 30

Kintex ultrascale kcu1500 acceleration development board 30 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 3: hardware platform when a new partial bitstream is to be downloaded, the device driver writes to a gate_pr register that causes its output to do the following: ° hold the static base r...

Page 31: Introduction

Kintex ultrascale kcu1500 acceleration development board 31 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4 software platform introduction the xilinx® acceleration kcu1500 4ddr expanded partial configuration platform is a memory-mapped system with pcie® host connectivity supported by a kerne...

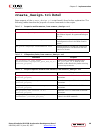

Page 32

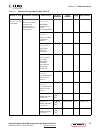

Kintex ultrascale kcu1500 acceleration development board 32 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4: software platform xdma, through dma_pf_demux (continued) s_axi_mgntpf axi4-lite control interface for management physical function (continued) scratchpad_ ram_ctrl axi bram controller...

Page 33

Kintex ultrascale kcu1500 acceleration development board 33 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4: software platform xdma, through dma_pf_demux (continued) s_axi_mgntpf axi4-lite control interface for management physical function (continued) sys_mgmt_wiz system management wizard s_...

Page 34

Kintex ultrascale kcu1500 acceleration development board 34 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4: software platform xdma, through dma_pf_demux (continued) s_axi_mgntpf axi4-lite control interface for management physical function (continued) xilmonitor_ fifo0 trace offload fifo for...

Page 35

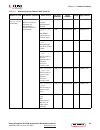

Kintex ultrascale kcu1500 acceleration development board 35 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4: software platform xdma m_axi axi memory-mapped data interface ddrmem_0 ddr4 channel 0 controller c0_ddr4_ s_axi 0x0000_0000 _ 0000_0000 4g 0x0000_0000_ ffff_ffff ddrmem_1 ddr4 channel...

Page 36: Software Layers

Kintex ultrascale kcu1500 acceleration development board 36 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4: software platform software layers the sdaccel runtime software is layered on top of a common low-level software interface called the hardware abstraction layer (hal). The hal driver p...

Page 37

Kintex ultrascale kcu1500 acceleration development board 37 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 4: software platform for more information about the common kernel mode drivers for hardware platforms targeting pcie accelerator cards with xdma ip, see the sdaccel environment platform ...

Page 38: Introduction

Kintex ultrascale kcu1500 acceleration development board 38 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 5 implementation introduction implementing the xilinx ® acceleration kcu1500 4ddr expanded partial reconfiguration platform in the vivado ® design suite is straightforward. The platform ...

Page 39

Kintex ultrascale kcu1500 acceleration development board 39 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 5: implementation 2. For more opportunity to interact with vivado, including the ability to refine the block diagram before running synthesis, to report timing between stages, and so for...

Page 40: Create_Design.Tcl

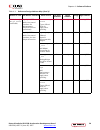

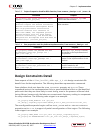

Kintex ultrascale kcu1500 acceleration development board 40 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 5: implementation create_design.Tcl detail some aspects of the create_design.Tcl script benefit from further explanation. The following tables describe the purpose of some commands in th...

Page 41: Design Constraints Detail

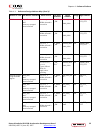

Kintex ultrascale kcu1500 acceleration development board 41 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 5: implementation design constraints detail some aspects of the xilinx_kcu1500_4ddr-xpr_4_0.Xdc design constraints file benefit from further explanation. The following describes represen...

Page 42

Kintex ultrascale kcu1500 acceleration development board 42 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 5: implementation a pblock is created, the reconfigurable expanded region logical hierarchy added to it, and then resized to include the ranges of physical resources that are used for th...

Page 43

Kintex ultrascale kcu1500 acceleration development board 43 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 5: implementation add_cells_to_pblock [get_pblocks pblock_upper] [get_cells [list xcl_design_i/expanded_region/memc/axicc_ddrmem_2_ctrl]] add_cells_to_pblock [get_pblocks pblock_upper] [...

Page 44: Introduction

Kintex ultrascale kcu1500 acceleration development board 44 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6 install, bring-up, and use introduction when implemented with a produced dsa as described in chapter 5, implementation , the xilinx ® acceleration kcu1500 4ddr expanded partial reconfi...

Page 45

Kintex ultrascale kcu1500 acceleration development board 45 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6: install, bring-up, and use 2. Use the xbinst utility included with the sdx environments installation to prepare board installation files, and program the configuration memory using th...

Page 46: Bring-Up Tests

Kintex ultrascale kcu1500 acceleration development board 46 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6: install, bring-up, and use the xbsak utility also offers more options and is very useful in bringing up and debugging a platform. For more details on the installation and bring-up pro...

Page 47: Device Identification

Kintex ultrascale kcu1500 acceleration development board 47 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6: install, bring-up, and use the following information can also be helpful when targeting the xilinx_kcu1500_4ddr-xpr_4_0.Dsa from the sdx environments installation, or as built from th...

Page 48: Clock Frequency

Kintex ultrascale kcu1500 acceleration development board 48 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6: install, bring-up, and use more information on map_connect can be found in the sdaccel environment user guide (ug1023) [ref 4] and the sdaccel environment optimization gui de (ug1027)...

Page 49: Timing Closure

Kintex ultrascale kcu1500 acceleration development board 49 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com chapter 6: install, bring-up, and use timing closure the platform contains many clock domains. With the exception of setup violations on the kernel clock domain (and if used, also kernel clock 2...

Page 50: Xilinx Resources

Kintex ultrascale kcu1500 acceleration development board 50 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com appendix a additional resources and legal notices xilinx resources for support resources such as answers, documentation, downloads, and forums, see xilinx support . Solution centers see the xili...

Page 51: References

Kintex ultrascale kcu1500 acceleration development board 51 ug1234 (v2017.1) june 20, 2017 www.Xilinx.Com appendix a: additional resources and legal notices references 1. Sdx environments release notes, installation, and licensing guide ( ug1238 ) 2. Sdaccel environment platform development guide ( ...