- DL manuals

- Xilinx

- Network Card

- LogiCORE 1000BASE-X

- User Manual

Xilinx LogiCORE 1000BASE-X User Manual

Summary of LogiCORE 1000BASE-X

Page 1

R logicore™ ip ethernet 1000base-x pcs/pma or sgmii v9.1 user guide ug155 march 24, 2008.

Page 2: Revision History

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 xilinx is disclosing this specification to you solely for use in the development of designs to operate on xilinx fpgas. Except as stated herein, none of the specification may be copied, reproduced, distributed, republished...

Page 3: Table of Contents

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com ug155 march 24, 2008 schedule of figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 schedule of tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 4

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 r implement the ethernet 1000base-x pcs/pma or sgmii core in your application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 chapter 5: using the client-side gm...

Page 5

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com ug155 march 24, 2008 r virtex-5 lxt and sxt devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111 virtex-5 fxt devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 r virtex-5 rocketio gtx transceivers for sgmii or dynamic standards switching constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168 ten-bit interface constraint...

Page 7

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com ug155 march 24, 2008 r appendix b: core latency core latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207 latency for 1000base-x pcs with tbi ...

Page 8

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 r.

Page 9: Schedule of Figures

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com ug155 march 24, 2008 chapter 2: core architecture figure 2-1: functional block diagram using rocketio transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . 24 figure 2-2: functional block diagram with a ten-bit interface . . . . . . ...

Page 10

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 r chapter 6: the ten-bit interface figure 6-1: ten-bit interface transmitter logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 figure 6-2: ten-bit-interface receiver logic . ....

Page 11

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com ug155 march 24, 2008 r chapter 11: dynamic switching of 1000base-x and sgmii standards figure 11-1: typical application for dynamic switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157 chapter 12: constraining the ...

Page 12

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 r.

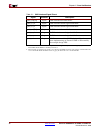

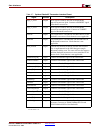

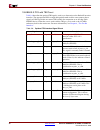

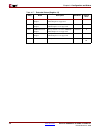

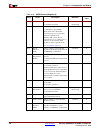

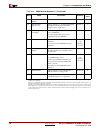

Page 13: Schedule of Tables

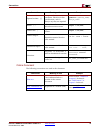

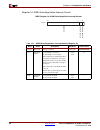

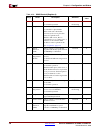

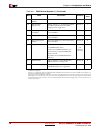

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com ug155 march 24, 2008 chapter 2: core architecture table 2-1: gmii interface signal pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 table 2-2: other common signals . . . . . . . . . . . . . . . . . . ...

Page 14

Www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 r table 9-21: phy identifier (registers 2 and 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139 table 9-22: sgmii auto-negotiation advertisement (register 4) . . . . . . . . . . . . . . . . . . 1...

Page 15: About This Guide

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 17 ug155 march 24, 2008 r preface about this guide the logicore™ ip ethernet 1000base-x pcs/pma or sgmii user guide provides information about generating a xilinx ethernet 1000base-x pcs/pma or sgmii core, customizing and simulating the core u...

Page 16: Conventions

18 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 preface: about this guide r • chapter 11, “dynamic switching of 1000base-x and sgmii standards” provides general guidelines for using the core to perform dynamic standards switching between 1000base-x and sgmii. • chapt...

Page 17

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 19 ug155 march 24, 2008 conventions r online document the following conventions are used in this document. Square brackets [ ] an optional entry or parameter. However, in bus specifications, such as bus[7:0] , they are required. Ngdbuild [ opt...

Page 18

20 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 preface: about this guide r.

Page 19: Introduction

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 21 ug155 march 24, 2008 r chapter 1 introduction the ethernet 1000base-x pcs/pma or sgmii core is a fully verified solution that supports verilog hdl and vhdl. In addition, the example design provided with the core supports both verilog and vh...

Page 20: Additional Core Resources

22 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 1: introduction r additional core resources for detailed information and updates about the ethernet 1000base-x pcs/pma or sgmii core, see the following documents, located on the xilinx ethernet 100base-x pcs/pma...

Page 21

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 23 ug155 march 24, 2008 feedback r document for comments or suggestions about this document, please submit a webcase from www.Support.Xilinx.Com/ . Be sure to include the following information: • document title • document number • page number(...

Page 22

24 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 1: introduction r.

Page 23: Core Architecture

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 23 ug155 march 24, 2008 r chapter 2 core architecture this chapter describes the architecture of the ethernet 1000base-x pcs/pma or sgmii core, including all interfaces and major functional blocks. System overview ethernet 1000base-x pcs/pma o...

Page 24

24 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r gmii block a client-side gmii is provided with the core, which can be used as an internal interface for connection to an embedded media access controller (mac) or other custom logic. Alter...

Page 25

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 25 ug155 march 24, 2008 system overview r optional pcs management registers configuration and status of the core, including access to and from the optional auto- negotiation function, uses the 1000base-x pcs management registers defined in iee...

Page 26: Core Interfaces

26 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r 8b/10b encoder 8b10b encoding, as defined in ieee 802.3 (tables 36-1a to 36-1e and table 36-2), is implemented in a block selectram™, configured as rom, and used as a large look-up table. ...

Page 27

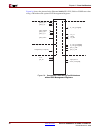

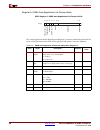

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 27 ug155 march 24, 2008 core interfaces r functionality. For more information, see chapter 3, “generating and customizing the core.” figure 2-3: component pinout using rocketio transceiver with pcs management registers mdc mdio_in gmii_rxd[7:0...

Page 28

28 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r figure 2-4 shows the pinout for the ethernet 1000base-x pcs/pma or sgmii core using a rocketio transceiver without the optional pcs management registers figure 2-4: component pinout using ...

Page 29

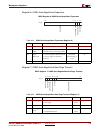

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 29 ug155 march 24, 2008 core interfaces r figure 2-5 shows the pinout for the ethernet 1000base-x pcs/pma or sgmii core when using the tbi with optional pcs management registers. The signals shown in the auto- negotiation box are included only...

Page 30

30 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r figure 2-6 shows the pinout for the ethernet 1000base-x pcs/pma or sgmii core when using a tbi without the optional pcs management registers. Figure 2-6: component pinout using ten-bit int...

Page 31

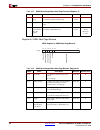

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 31 ug155 march 24, 2008 core interfaces r figure 2-7 shows the pinout for the ethernet 1000base-x pcs/pma or sgmii core using the optional dynamic switching logic (between 1000base-x and sgmii standards). This mode is shown used with a rocketi...

Page 32

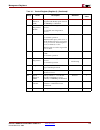

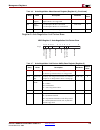

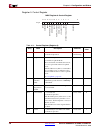

32 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r table 2-1: gmii interface signal pinout signal direction description gmii_txd[7:0] 1 1. When the transmitter elastic buffer is present these signals are synchronous to gmii_tx_clk. When th...

Page 33

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 33 ug155 march 24, 2008 core interfaces r common signal pinout table 2-2 describes the remaining signals common to all parameterizations of the core. Table 2-2: other common signals signal direction description reset input asynchronous reset f...

Page 34

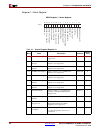

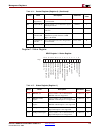

34 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r mdio management interface pinout (optional) table 2-3 describes the optional mdio interface signals of the core used to access the pcs management registers. These signals are typically con...

Page 35

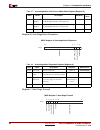

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 35 ug155 march 24, 2008 core interfaces r configuration vector (optional) table 2-4 shows the alternative to the optional mdio management interface, the configuration vector. See “optional configuration vector” in chapter 9 . Auto-negotiation ...

Page 36

36 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r dynamic switching signal pinout table 2-6 describes the signals present when the optional dynamic switching mode (between 1000base-x and sgmii standards) is selected. In this case, the mdi...

Page 37

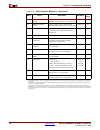

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 37 ug155 march 24, 2008 core interfaces r table 2-7: optional rocketio transceiver interface pinout signal direction description mgt_rx_reset 1 1. When the core is used with a rocketio transceiver, userclk2 is used as the 125 mhz reference clo...

Page 38

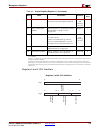

38 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 2: core architecture r 1000base-x pcs with tbi pinout table 2-8 describes the optional tbi signals, used as an alternative to the rocketio receiver interface. The appropriate hdl example design delivered with th...

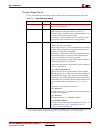

Page 39: Gui Interface

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 39 ug155 march 24, 2008 r chapter 3 generating and customizing the core the ethernet 1000base-x pcs/pma or sgmii core is generated using the core generator. This chapter describes the gui options used to generate and customize the core. Gui in...

Page 40

40 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 3: generating and customizing the core r select standard select from the following standards for the core: • 1000base-x . 1000base-x physical coding sublayer (pcs) functionality is designed to the ieee 802.3 spe...

Page 41

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 41 ug155 march 24, 2008 gui interface r physical interface depending on the target architecture, two physical interface options are available for the core. • rocketio . Uses a rocketio transceiver specific to the selected device family to exte...

Page 42

42 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 3: generating and customizing the core r this screen lets you select the receiver elastic buffer type to be used with the core. Before selecting this option, see “receiver elastic buffer implementations” in chap...

Page 43

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 43 ug155 march 24, 2008 parameter values in the xco file r rocketio tile configuration the rocketio tile configuration screen is only displayed if the rocketio interface is used with the virtex-4 or virtex-5 device families. Rocketio transceiv...

Page 44: Output Generation

44 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 3: generating and customizing the core r table 3-1 describes the xco file parameters, values and summarizes the gui defaults. The following is an example of the cset parameters in an xco file: cset component_nam...

Page 45: Designing With The Core

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 45 ug155 march 24, 2008 r chapter 4 designing with the core this chapter provides information about creating your own designs using the ethernet 1000base-x pcs/pma or sgmii core. Design guidelines, as well as the variety of implementations pre...

Page 46

46 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 4: designing with the core r 1000base-x standard using rocketio transceiver example design figure 4-1 illustrates the example design in 1000base-x mode using the virtex-ii pro or virtex-4 mgt, virtex-5 gtp or vi...

Page 47

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 47 ug155 march 24, 2008 design overview r 1000base-x standard with tbi example design figure 4-2 illustrates the example design in 1000base-x mode using a tbi. As illustrated, the example is split between two hierarchical layers. The block lev...

Page 48

48 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 4: designing with the core r sgmii standard using a rocketio transceiver example design figure 4-3 illustrates the example design in sgmii mode using the virtex-ii pro or virtex- 4 mgt, virtex-5 gtp or virtex-5 ...

Page 49

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 49 ug155 march 24, 2008 design overview r sgmii standard with tbi transceiver example design figure 4-3 illustrates the example design with the sgmii standard using a tbi. This is also the example design created when the dynamic switching capa...

Page 50: Design Guidelines

50 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 4: designing with the core r design guidelines generate the core generate the core using the core generator, as described in chapter 3, “generating and customizing the core.” examine the example design provided ...

Page 51

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 51 ug155 march 24, 2008 design guidelines r write an hdl application after reviewing the example design delivered with the core, write an hdl application that uses single or multiple instances of the block level module for the ethernet 1000bas...

Page 52

52 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 4: designing with the core r keep it registered to simplify timing and to increase system performance in an fpga design, keep all inputs and outputs registered between the user application and the core. All inpu...

Page 53

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 53 ug155 march 24, 2008 r chapter 5 using the client-side gmii data path this chapter provides general guidelines for creating designs using client-side gmii of the ethernet 1000base-x pcs/pma or sgmii core. Designing with the client-side gmii...

Page 54

54 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r error propagation a corrupted frame transfer is illustrated in figure 5-2 . An error may be injected into the frame by asserting gmii_tx_er at any point during the gmii_...

Page 55

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 55 ug155 march 24, 2008 designing with the client-side gmii for the 1000base-x standard r normal frame reception with extension field in accordance with the ieee 802.3 , clause 36, state machines for the 1000base-x pcs, gmii_rx_er may be drive...

Page 56

56 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r false carrier figure 5-6 illustrates the gmii signaling for a false carrier condition. False carrier is asserted by the core in response to certain error conditions, suc...

Page 57

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 57 ug155 march 24, 2008 designing with the client-side gmii for the 1000base-x standard r bits[4:2]: code group reception indicators these signals indicate the reception of particular types of group, as defined below. Figure 5-7 illustrates th...

Page 58

58 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r be included in the frame supplied to the core. The rocketio transceiver will replace these four bytes with the calculated crc value. Gmii reception the timing of normal ...

Page 59

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 59 ug155 march 24, 2008 designing with client-side gmii for the sgmii standard r designing with client-side gmii for the sgmii standard overview when the core is generated for the sgmii standard, changes are made to the core that affect the pc...

Page 60

60 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r 10 megabit per second frame transmission the operation of the core remains unchanged. It is the responsibility of the client logic (for example, an ethernet mac), to ent...

Page 61: Implementing External Gmii

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 61 ug155 march 24, 2008 using the gmii as an internal connection r 10 megabit per second frame reception the operation of the core remains unchanged. When operating at a speed of 10 mbps, every byte of the mac frame (from destination address t...

Page 62

62 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r virtex-ii pro and virtex-ii devices figure 5-14 illustrates how to create an external gmii transmitter in a virtex-ii family device. The signal names and logic shown on ...

Page 63

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 63 ug155 march 24, 2008 implementing external gmii r spartan-3, spartan-3e and spartan-3a devices the logic described previously for virtex-ii and virtex-ii pro devices does not meet the input setup and hold requirements for gmii with spartan-...

Page 64

64 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r virtex-4 devices the logic described previously for virtex-ii and virtex-ii pro devices does not meet the input setup and hold requirements for gmii with virtex-4 device...

Page 65

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 65 ug155 march 24, 2008 implementing external gmii r virtex-5 devices figure 5-17 illustrates how to create an external gmii transmitter in a virtex-5 family device. The signal names and logic shown on the figure exactly match those delivered ...

Page 66

66 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r gmii receiver logic figure 5-18 illustrates an external gmii receiver created in a virtex-ii family device. The signal names and logic shown in the figure exactly match ...

Page 67

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 67 ug155 march 24, 2008 implementing external gmii r figure 5-18: external gmii receiver logic iob logic obuft fddrrse opad d q '0' '1' gmii_rxd_obuf[0] opad opad opad obuft obuft obuft d q d q d q d q gmii_rx_dv_obuf gmii_rx_er_obuf gmii_rxd[...

Page 68

68 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 5: using the client-side gmii data path r.

Page 69: The Ten-Bit Interface

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 69 ug155 march 24, 2008 r chapter 6 the ten-bit interface this chapter provides general guidelines for creating 1000base-x, sgmii or dynamic standards switching designs using the ten-bit interface (tbi). An explanation of the tbi logic in all ...

Page 70

70 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 6: the ten-bit interface r receiver logic virtex-ii and virtex-ii pro devices figure 6-2 illustrates an external receiver tbi in virtex-ii devices. The signal names and logic displayed precisely match those deli...

Page 71

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 71 ug155 march 24, 2008 ten-bit-interface logic r synchronous to pma_rx_clk0_bufg and pma_rx_clk1_bufg , respectively. These busses are then immediately registered inside the core on their respective clock. Figure 6-2: ten-bit-interface receiv...

Page 72

72 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 6: the ten-bit interface r spartan-3, spartan-3e and spartan-3a devices the logic described previously for virtex-ii and virtex-ii pro devices does not meet the input setup and hold requirements for tbi with spa...

Page 73

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 73 ug155 march 24, 2008 ten-bit-interface logic r virtex-4 devices method 1 the virtex-4 fpga logic used by the example design delivered with the core is illustrated in figure 6-4 . This shows a virtex-4 device iddr primitive used with the ddr...

Page 74

74 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 6: the ten-bit interface r method 2 this logic from method 1 relies on pma_rx_clk0 and pma_rx_clk1 being exactly 180 degrees out of phase with each other since the falling edge of pma_rx_clk0 is used in place of...

Page 75

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 75 ug155 march 24, 2008 ten-bit-interface logic r virtex-5 devices method 1 the virtex-5 fpga logic used by the example design delivered with the core is illustrated in figure 6-6 . This shows a virtex-5 device iddr primitive used with the ddr...

Page 76

76 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 6: the ten-bit interface r method 2 this logic from method 1 relies on pma_rx_clk0 and pma_rx_clk1 being exactly 180 degrees out of phase with each other because the falling edge of pma_rx_clk0 is used in place ...

Page 77

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 77 ug155 march 24, 2008 clock sharing across multiple cores with tbi r clock sharing across multiple cores with tbi figure 6-8 illustrates sharing clock resources across multiple instantiations of the core when using the tbi. Gtx_clk may be sh...

Page 78

78 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 6: the ten-bit interface r.

Page 79: 1000Base-X With Rocketio

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 79 ug155 march 24, 2008 r chapter 7 1000base-x with rocketio transceivers this chapter provides general guidelines for creating 1000base-x designs that use rocketio transceivers for virtex-ii pro, virtex-4, and virtex-5 devices. Information ab...

Page 80

80 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r figure 7-1: 1000base-x connection to a virtex-ii pro mgt ethernet 1000base-x pcs/pma or sgmii logicore virtex-ii pro rocketio (gt_ethernet_1) brefclk2 txusrclk txusrclk...

Page 81

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 81 ug155 march 24, 2008 rocketio transceiver logic r virtex-4 fx devices the core is designed to integrate with the virtex-4 rocketio mgt. Figure 7-2 illustrates the connections and logic required between the core and mgt—the signal names and ...

Page 82

82 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r figure 7-2: 1000base-x connection to virtex-4 mgt ethernet 1000base-x pcs/pma or sgmii logicore virtex-4 gt11 rocketio (used) txusrclk txusrclk2 rxusrclk rxusrclk2 user...

Page 83

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 83 ug155 march 24, 2008 rocketio transceiver logic r virtex-5 lxt and sxt devices the core is designed to integrate with the virtex-5 rocketio gtp transceiver. Figure 7-3 illustrates the connections and logic required between the core and the ...

Page 84

84 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r figure 7-3: 1000base-x connection to virtex-5 gtp transceivers ethernet 1000base-x pcs/pma or sgmii logicore virtex-5 gtp rocketio (0) txu s rclk0 txu s rclk20 rxu s rc...

Page 85

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 85 ug155 march 24, 2008 rocketio transceiver logic r virtex-5 fxt devices the core is designed to integrate with the virtex-5 rocketio gtx transceiver. Figure 7-4 illustrates the connections and logic required between the core and the gtx tran...

Page 86

86 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r figure 7-4: 1000base-x connection to virtex-5 gtx transceivers ethernet 1000base-x pcs/pma or sgmii logicore virtex-5 gtp rocketio (0) txu s rclk0 txu s rclk20 rxu s rc...

Page 87

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 87 ug155 march 24, 2008 clock sharing across multiple cores with rocketio r clock sharing across multiple cores with rocketio virtex-ii pro devices figure 7-5 illustrates sharing clock resources across two instantiations of the core on the sam...

Page 88

88 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r virtex-4 fx devices figure 7-6 illustrates sharing clock resources across multiple instantiations of the core when using mgts. Note that the example design, when using ...

Page 89

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 89 ug155 march 24, 2008 clock sharing across multiple cores with rocketio r figure 7-6: clock management - multiple core instances, mgts for 1000base-x ethernet 1000base-x pcs/pma or sgmii core userclk userclk2 ipad b refclkp (250mhz) ipad b r...

Page 90

90 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r virtex-5 lxt and sxt devices figure 7-7 illustrates sharing clock resources across multiple instantiations of the core when using virtex-5 rocketio gtp transceivers. Th...

Page 91

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 91 ug155 march 24, 2008 clock sharing across multiple cores with rocketio r figure 7-7: clock management - multiple core instances, virtex-5 rocketio gtp transceivers for 1000base-x ethernet 1000base-x pcs/pma or sgmii core userclk userclk2 vi...

Page 92

92 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r virtex-5 fxt devices figure 7-8 illustrates sharing clock resources across multiple instantiations of the core when using virtex-5 rocketio gtx transceivers. The exampl...

Page 93

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 93 ug155 march 24, 2008 clock sharing across multiple cores with rocketio r figure 7-8: clock management - multiple core instances, virtex-5 rocketio gtx transceivers for 1000base-x ethernet 1000base-x pcs/pma or sgmii core userclk userclk2 vi...

Page 94

94 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 7: 1000base-x with rocketio transceivers r.

Page 95: With Rocketio Transceivers

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 95 ug155 march 24, 2008 r chapter 8 sgmii / dynamic standards switching with rocketio transceivers this chapter provides general guidelines for creating sgmii designs, and designs capable of switching between 1000base-x and sgmii standards (dy...

Page 96

96 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r (see the next section). However, there are logical implementations where this can be reliable and has the benefit of lower logic utilization. T...

Page 97

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 97 ug155 march 24, 2008 receiver elastic buffer implementations r considering the 10 mbps case, we would need 152200/5000 = 31 fifo entries in the elastic buffer above and below the half way point to guarantee that the buffer will not under or...

Page 98

98 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r closely related clock sources case 1 figure 8-2 illustrates a simplified diagram of a common situation where the core, in sgmii mode, is interf...

Page 99

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 99 ug155 march 24, 2008 rocketio logic with the fabric rx elastic buffer r rocketio logic with the fabric rx elastic buffer the example design delivered with the core is split between two hierarchical layers, as illustrated in figure 4-3 . The...

Page 100

100 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r figure 8-3: sgmii connection to a virtex-ii pro rocketio transceiver ethernet 1000base-x pcs/pma or sgmii logicore virtex-ii pro rocketio (gt_...

Page 101

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 101 ug155 march 24, 2008 rocketio logic with the fabric rx elastic buffer r virtex-4 devices for sgmii or dynamic standards switching the core is designed to integrate with the virtex-4 mgt. The connections and logic required between the core ...

Page 102

102 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r caution! The phy connected via sgmii may always provide dynamic sgmii data (when powered up). If not, and if signal_detect is not present, the...

Page 103

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 103 ug155 march 24, 2008 rocketio logic with the fabric rx elastic buffer r virtex-5 lxt or sxt devices for sgmii or dynamic standards switching the core is designed to integrate with the virtex-5 rocketio gtp transceiver. The connections and ...

Page 104

104 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r . Figure 8-5: sgmii connection to a virtex-5 rocketio gtp transceiver ethernet 1000base-x pcs/pma or sgmii logicore virtex-5 gtp rocketio (use...

Page 105

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 105 ug155 march 24, 2008 rocketio logic with the fabric rx elastic buffer r virtex-5 fxt devices for sgmii or dynamic standards switching the core is designed to integrate with the virtex-5 rocketio gtx transceiver. The connections and logic r...

Page 106

106 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r getting started guide and the core generator guide, at www.Xilinx.Com/support/software_manuals.Htm . Figure 8-6: sgmii connection to a virtex-...

Page 107

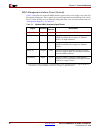

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 107 ug155 march 24, 2008 clock sharing - multiple cores with rocketio, fabric elastic buffer r clock sharing - multiple cores with rocketio, fabric elastic buffer virtex-ii pro devices figure 8-7 illustrates sharing clock resources across mult...

Page 108

108 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r the device. For more information, see the virtex-ii pro rocketio transceiver user guide . Each brefclk domain must use its own dcm to derive i...

Page 109

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 109 ug155 march 24, 2008 clock sharing - multiple cores with rocketio, fabric elastic buffer r virtex-4 fx devices figure 8-8 illustrates sharing clock resources across multiple instantiations of the core when using the virtex-4 rocketio mgt. ...

Page 110

110 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r figure 8-8: clock management with multiple core instances with virtex-4 mgts for sgmii component_n a me _ b lock (block level) ethernet 1000ba...

Page 111

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 111 ug155 march 24, 2008 clock sharing - multiple cores with rocketio, fabric elastic buffer r virtex-5 lxt and sxt devices figure 8-9 illustrates sharing clock resources across multiple instantiations of the core when using the virtex-5 rocke...

Page 112

112 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r . Figure 8-9: clock management with multiple core instances with virtex-5 gtp rocketio transceivers for sgmii component_n a me _ b lock (block...

Page 113

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 113 ug155 march 24, 2008 clock sharing - multiple cores with rocketio, fabric elastic buffer r virtex-5 fxt devices figure 8-9 illustrates sharing clock resources across multiple instantiations of the core when using the virtex-5 rocketio gtx ...

Page 114

114 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 8: sgmii / dynamic standards switching with rocketio transceivers r . Figure 8-10: clock management with multiple core instances with virtex-5 gtx rocketio transceivers for sgmii component_n a me _ b lock (bloc...

Page 115: Configuration and Status

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 115 ug155 march 24, 2008 r chapter 9 configuration and status this chapter provides general guidelines for configuring and monitoring the ethernet 1000base-x pcs/pma or sgmii core, including a detailed description of the core management regist...

Page 116

116 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r . The mdio bus system is a standardized interface for accessing the configuration and status registers of ethernet phy devices. In the example illustrated, the management host bus ...

Page 117

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 117 ug155 march 24, 2008 mdio management interface r write transaction figure 9-2 shows a write transaction across the mdio, defined as op=”01.” the addressed phy device (with physical address phyad) takes the 16-bit word in the data field and...

Page 118

118 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r known by the mdio master (in this case an ethernet mac), and placed into the phyad field of the mdio frame (see “mdio transactions” ). The phyad field for an mdio frame is a 5-bit ...

Page 119: Management Registers

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 119 ug155 march 24, 2008 management registers r . Management registers the contents of the management registers can be accessed using the regad field of the mdio frame. Contents will vary depending on the core generator options, and are define...

Page 120

120 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 0: control register 2,3 phy identifier 4 auto-negotiation advertisement register 5 auto-negotiation link partner ability base register 6 auto-negotiation expansion registe...

Page 121

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 121 ug155 march 24, 2008 management registers r 0.13 speed selection (lsb) always returns a 0 for this bit. Together with bit 0.6, speed selection of 1000 mbps is identified returns 0 0 0.12 auto- negotiation enable 1 = enable auto-negotiation...

Page 122

122 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 1: status register mdio register 1: status register table 9-4: status register (register 1) bit(s) name description attributes default value 1.15 100base-t4 always returns...

Page 123

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 123 ug155 march 24, 2008 management registers r registers 2 and 3: phy identifiers 1.4 remote fault 1 = remote fault condition detected 0 = no remote fault condition detected read only self- clearing on read 0 1.3 auto- negotiation ability alw...

Page 124

124 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 4: auto-negotiation advertisement table 9-5: phy identifier (registers 2 and 3) bit(s) name description attributes default value 2.15:0 organizationally unique identifier ...

Page 125

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 125 ug155 march 24, 2008 management registers r register 5: auto-negotiation link partner base 4.6 half duplex always returns a ‘0’ for this bit since half duplex mode is not supported returns 0 0 4.5 full duplex 1 = full duplex mode is advert...

Page 126

126 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 6: auto-negotiation expansion register 7: next page transmit 5.6 half duplex 1 = half duplex mode is supported 0 = half duplex mode is not supported read only 0 5.5 full d...

Page 127

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 127 ug155 march 24, 2008 management registers r register 8: next page receive table 9-9: auto-negotiation next page transmit (register 7) bit(s) name description attributes default value 7.15 next page 1 = additional next page(s) will follow 0...

Page 128

128 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 15: extended status 8.12 acknowledge 2 1 = comply with message 0 = cannot comply with message read only 0 8.11 toggle value toggles between subsequent next pages read only...

Page 129

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 129 ug155 march 24, 2008 management registers r register 16: vendor-specific auto-negotiation interrupt control 1000base-x standard without the optional auto-negotiation it is not the intention of this document to fully describe the 1000base-x...

Page 130

130 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 0: control register mdio register 0: control register table 9-14: control register (register 0) bit(s) name description attributes default value 0.15 reset 1 = pcs/pma res...

Page 131

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 131 ug155 march 24, 2008 management registers r register 1: status register 0.9 restart auto- negotiation ignore this bit because auto-negotiation is not included. Read/ write 0 0.8 duplex mode always returns a ‘1’ for this bit to signal full-...

Page 132

132 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r 1.10 100base-t2 full duplex always returns a ‘0’ for this bit since 100base-t2 full duplex is not supported returns 0 0 1.9 100base-t2 half duplex always returns a ‘0’ for this bit...

Page 133

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 133 ug155 march 24, 2008 management registers r registers 2 and 3: phy identifier register 15: extended status mdio registers 2 and 3: phy identifier table 9-16: phy identifier (registers 2 and 3) bit(s) name description attributes default val...

Page 134

134 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r table 9-17: extended status (register 15) bit(s) name description attributes default value 15.15 1000base-x full duplex always returns a ‘1’ since 1000base- x full duplex is suppor...

Page 135

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 135 ug155 march 24, 2008 management registers r sgmii standard using the optional auto-negotiation the registers provided for sgmii operation in this core are adaptations of those defined in ieee 802.3 clauses 37 and 22. In an sgmii implementa...

Page 136

136 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r table 9-19: sgmii control (register 0) bit(s) name description attributes default value 0.15 reset 1 = core reset 0 = normal operation read/write self clearing 0 0.14 loopback 1 = ...

Page 137

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 137 ug155 march 24, 2008 management registers r register 1: sgmii status 0.5 unidirectiona l enable enable transmit regardless of whether a valid link has been established read/ write 0 0.4:0 reserved always return 0s , writes ignored returns ...

Page 138

138 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r 1.7 unidirectional ability always returns ‘1,’ writes ignored returns 1 1 1.6 mf preamble suppression always returns a ‘1’ for this bit to indicate that management frame preamble s...

Page 139

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 139 ug155 march 24, 2008 management registers r registers 2 and 3: phy identifier register 4: sgmii auto-negotiation advertisement mdio registers 2 and 3: phy identifier table 9-21: phy identifier (registers 2 and 3) bit(s) name description at...

Page 140

140 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 5: sgmii auto-negotiation link partner ability the auto-negotiation ability base register (register 5) contains information related to the status of the link between the p...

Page 141

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 141 ug155 march 24, 2008 management registers r register 6: sgmii auto-negotiation expansion register 7: sgmii auto-negotiation next page transmit mdio register 6: sgmii auto-negotiation expansion table 9-24: sgmii auto-negotiation expansion (...

Page 142

142 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 8: sgmii next page receive 7.12 acknowled ge 2 1 = comply with message 0 = cannot comply with message read/ write 0 7.11 toggle value toggles between subsequent next pages...

Page 143

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 143 ug155 march 24, 2008 management registers r register 15: sgmii extended status mdio register 15: sgmii extended status table 9-27: sgmii extended status register (register 15) bit(s) name description attributes default value 15.15 1000base...

Page 144

144 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 16: sgmii auto-negotiation interrupt control mdio register 16: sgmii auto-negotiation interrupt control table 9-28: sgmii auto-negotiation interrupt control (register 16) ...

Page 145

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 145 ug155 march 24, 2008 management registers r sgmii standard without the optional auto-negotiation the registers provided for sgmii operation in this core are adaptations of those defined in ieee 802.3 clauses 37 and 22. In an sgmii implemen...

Page 146

146 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r table 9-30: sgmii control (register 0) bit(s) name description attributes default value 0.15 reset 1 = core reset 0 = normal operation read/write self clearing 0 0.14 loopback 1 = ...

Page 147

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 147 ug155 march 24, 2008 management registers r register 1: sgmii status 0.5 unidirectiona l enable enable transmit regardless of whether a valid link has been established read/ write 0 0.4:0 reserved always return 0s , writes ignored returns ...

Page 148

148 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r 1.7 unidirectional ability always returns ‘1,’ writes ignored returns 1 1 1.6 mf preamble suppression always returns a ‘1’ for this bit to indicate that management frame preamble s...

Page 149

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 149 ug155 march 24, 2008 management registers r registers 2 and 3: phy identifier register 4: sgmii auto-negotiation advertisement mdio registers 2 and 3: phy identifier table 9-32: phy identifier (registers 2 and 3) bit(s) name description at...

Page 150

150 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r register 15: sgmii extended status both 1000base-x and sgmii standards table 9-35 describes register 17, the vendor-specific standard selection register. This register is only pres...

Page 151

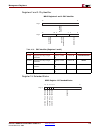

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 151 ug155 march 24, 2008 optional configuration vector r register 17: vendor-specific standard selection register optional configuration vector if “mdio management interface” is omitted, relevant configuration signals are brought out of the co...

Page 152

152 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 9: configuration and status r these signals may be changed by the user application at any time. The clock domain heading denotes the clock domain the configuration signal is registered in before use by the core...

Page 153: Auto-Negotiation

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 153 ug155 march 24, 2008 r chapter 10 auto-negotiation this chapter provides general guidelines for using the auto-negotiation function of the ethernet 1000base-x pcs/pma or sgmii core. Auto-negotiation is controlled and monitored through the ...

Page 154

154 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 10: auto-negotiation r a link segment (the link partner) and to detect corresponding operational modes that the link partner advertises. Figure 10-1 illustrates the operation of 1000base-x auto- negotiation. Th...

Page 155

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 155 ug155 march 24, 2008 overview of operation r sgmii standard figure 10-2 illustrates the operation of sgmii auto-negotiation. Additional information about sgmii standard auto-negotiation is provided in the following sections. The sgmii capa...

Page 156

156 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 10: auto-negotiation r setting the configurable link timer the optional auto-negotiation function has a link timer ( link_timer[8:0] ) port. This port sets the period of the auto-negotiation link timer. This po...

Page 157: Sgmii Standards

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 157 ug155 march 24, 2008 r chapter 11 dynamic switching of 1000base-x and sgmii standards this chapter provides general guidelines for using the core to perform dynamic standards switching between 1000base-x and sgmii. The core will only provi...

Page 158: Operation of The Core

158 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 11: dynamic switching of 1000base-x and sgmii standards r operation of the core selecting the power-on / reset standard the external port of the core, basex_or_sgmii (see “dynamic switching signal pinout” in ch...

Page 159

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 159 ug155 march 24, 2008 operation of the core r replace the link_timer_value[8:0] port that is used when the core is generated for a single standard. • link_timer_basex[8:0] the value placed on this port is sampled at the beginning of the aut...

Page 160

160 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 11: dynamic switching of 1000base-x and sgmii standards r.

Page 161: Constraining The Core

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 161 ug155 march 24, 2008 r chapter 12 constraining the core this chapter defines the constraint requirements of the ethernet 1000base-x pcs/pma or sgmii core. An example ucf is provided with the hdl example design for the core to implement the...

Page 162

162 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r the hdl source code for the example design and with the information contained in chapter 7, “1000base-x with rocketio transceivers.” clock period constraints the clock provided to us...

Page 163

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 163 ug155 march 24, 2008 required constraints r ############################################################ # rocket i/o placement: # ############################################################ # place the rocket i/o inst "rocketio/mgt" loc ...

Page 164

164 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r virtex-4 rocketio mgts for 1000base-x constraints the constraints defined in this section are implemented in the ucf for the example designs delivered with the core. Sections from th...

Page 165

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 165 ug155 march 24, 2008 required constraints r the following ucf syntax shows these constraints being applied. #*********************************************************** # pcs/pma clock period constraints: please do not relax * #***********...

Page 166

166 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r virtex-4 rocketio mgts for sgmii or dynamic standards switching constraints all the constraints described in the section “virtex-4 rocketio mgts for 1000base-x constraints.” in addit...

Page 167

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 167 ug155 march 24, 2008 required constraints r virtex-5 rocketio gtp transceivers for sgmii or dynamic standards switching constraints if the core is generated to use the gtp rx elastic buffer, all of the constraints apply, as defined in “clo...

Page 168

168 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r net "*clkin" tnm_net = "clkin"; timespec "ts_clkin" = period "clkin" 8 ns high 50 %; net "*refclkout" tnm_net = "refclkout"; timespec "ts_refclkout" = period "refclkout" 8 ns high 50...

Page 169

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 169 ug155 march 24, 2008 required constraints r clock period constraints the clocks provided to pma_rx_clk0 and pma_rx_clk1 must be constrained for a clock frequency of 62.5 mhz. The clock provided to gtx_clk must be constrained for a clock fr...

Page 170

170 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r in addition, the example design provides pad locking on the tbi for several families. This is included as a guideline only, and there are no specific i/o location constraints for thi...

Page 171

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 171 ug155 march 24, 2008 required constraints r inst "core_wrapper/tbi_rx_clk1_dcm" clkout_phase_shift = fixed; inst "core_wrapper/tbi_rx_clk1_dcm" phase_shift = -10; inst "core_wrapper/tbi_rx_clk1_dcm" deskew_adjust = 0; the values of phase_s...

Page 172

172 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r virtex-5 devices figure 6-6, page 75 illustrates the tbi input logic provided by the example design for the virtex-5 family. Iodelay elements are instantiated on the tbi data input p...

Page 173

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 173 ug155 march 24, 2008 required constraints r ############################################################ # gmii clock period constraints: please do not relax # ############################################################ net "gmii_tx_clk_b...

Page 174

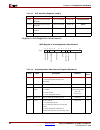

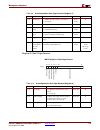

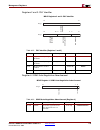

174 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r gmii input setup/hold timing input gmii timing specification figure 12-3 and table 12-2 illustrate the setup and hold time window for the input gmii signals. These are the worst-case...

Page 175

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 175 ug155 march 24, 2008 required constraints r timing which is achieved after place-and-route is reported in the datasheet section of the trce report (created by the implement script). For customers fixing their own pinout, the setup and hold...

Page 176

176 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r inst "gmii_data_bus[6].Delay_gmii_txd" idelay_value = "33"; inst "gmii_data_bus[5].Delay_gmii_txd" idelay_value = "33"; inst "gmii_data_bus[4].Delay_gmii_txd" idelay_value = "33"; in...

Page 178

178 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 12: constraining the core r.

Page 179: Interfacing to Other Cores

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 179 ug155 march 24, 2008 r chapter 13 interfacing to other cores this chapter describes some additional design considerations associated with implementing the ethernet 1000base-x pcs/pma or sgmii core with other cores. • 1-gigabit ethernet mac...

Page 180

180 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r figure 13-1: 1-gigabit ethernet mac extended to include 1000base-x pcs with tbi 1-gigabit ethernet mac logicore gmii_rx_clk gmii_rxd[7:0] gmii_rx_dv gmii_rx_er gmii_txd[7:0] gmi...

Page 181

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 181 ug155 march 24, 2008 integrating with the 1-gigabit ethernet mac core r integration of the 1-gigabit ethernet mac using a rocketio transceiver virtex-ii pro devices figure 13-2 illustrates the connections and clock management logic require...

Page 182

182 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r • if both cores have been generated with the optional management interface, the mdio port can be connected up to that of the 1-gigabit ethernet mac core, allowing the mac to acc...

Page 183

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 183 ug155 march 24, 2008 integrating with the 1-gigabit ethernet mac core r features of this configuration include: • direct internal connections are made between the gmii interfaces between the two cores. • if both cores have been generated w...

Page 184

184 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r features of this configuration include: • direct internal connections are made between the gmii interfaces between the two cores. • if both cores have been generated with the op...

Page 185

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 185 ug155 march 24, 2008 integrating with the tri-mode ethernet mac core r features of this configuration include: • direct internal connections are made between the gmii interfaces between the two cores. • if both cores have been generated wi...

Page 186

186 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r • if both cores have been generated with the optional management interface, the mdio port can be connected to that of the tri-speed ethernet mac core, allowing the mac to access...

Page 187

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 187 ug155 march 24, 2008 integrating with the tri-mode ethernet mac core r figure 13-6: tri-speed ethernet mac extended to use an sgmii with tbi tri-speed ethernet mac logicore phyemacrxd[7:0] phyemacrxdv phyemacrxer emacphytxd7:0] emacphytxen...

Page 188

188 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r integration of the tri-mode ethernet mac to provide sgmii (or dynamic switching) functionality using rocketio transceivers virtex-ii pro devices figure 13-7 illustrates the conn...

Page 189

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 189 ug155 march 24, 2008 integrating with the tri-mode ethernet mac core r figure 13-7: tri-speed ethernet mac extended to use an sgmii in virtex-ii pro tri-speed ethernet mac logicore phyemacrxd[7:0] phyemacrxdv phyemacrxer emacphytxd7:0] ema...

Page 190

190 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r virtex-4 devices figure 13-8 illustrates the connections and clock management logic required to interface the ethernet 1000base-x pcs/pma or sgmii core (when used in sgmii mode ...

Page 191

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 191 ug155 march 24, 2008 integrating with the tri-mode ethernet mac core r figure 13-8: tri-speed ethernet mac extended to use an sgmii in virtex-4 tri-speed ethernet mac logicore phyemacrxd[7:0] phyemacrxdv phyemacrxer emacphytxd7:0] emacphyt...

Page 192

192 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r virtex-5 lxt and sxt devices figure 13-9 illustrates the connections and clock management logic required to interface the ethernet 1000base-x pcs/pma or sgmii core (when used in...

Page 193

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 193 ug155 march 24, 2008 integrating with the tri-mode ethernet mac core r figure 13-9: tri-speed ethernet mac extended to use an sgmii in virtex-5 lxt/sxt tri-speed ethernet mac logicore phyemacrxd[7:0] phyemacrxdv phyemacrxer emacphytxd7:0] ...

Page 194

194 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r virtex-5 fxt devices figure 13-10 illustrates the connections and clock management logic required to interface the ethernet 1000base-x pcs/pma or sgmii core (when used in sgmii ...

Page 195

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 195 ug155 march 24, 2008 integrating with the tri-mode ethernet mac core r figure 13-10: tri-speed ethernet mac extended to use an sgmii in virtex-5 fxt tri-speed ethernet mac logicore phyemacrxd[7:0] phyemacrxdv phyemacrxer emacphytxd7:0] ema...

Page 196

196 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 13: interfacing to other cores r.

Page 197: Power Management

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 197 ug155 march 24, 2008 r chapter 14 special design considerations this chapter describes the unique design considerations associated with implementing the ethernet 1000base-x pcs/pma or sgmii core. Power management no power management consid...

Page 198

198 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 14: special design considerations r page 38 ). This instructs the attached pma serdes device to enter loopback mode as illustrated in figure 14-1 . Core with rocketio transceiver the loopback path is implemente...

Page 199

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 199 ug155 march 24, 2008 loopback r figure 14-2: loopback implementation when using the core with rocketio transceivers ethernet 1000base-x pcs/pma or sgmii core rocketio transceiver tx rx fpga loopback occurs in core pcs tx engine pcs rx engi...

Page 200

200 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 14: special design considerations r.

Page 201: Implementing The Design

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 201 ug155 march 24, 2008 r chapter 15 implementing the design this chapter describes how to simulate and implement your design containing the ethernet 1000base-x pcs/pma or sgmii core. Pre-implementation simulation a functional model of the et...

Page 202: Implementation

202 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 15: implementing the design r see the xst user guide for more information on creating project and synthesis script files, and running the xst program. Xst - verilog there is a module declaration for the etherne...

Page 203

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 203 ug155 march 24, 2008 post-implementation simulation r layout and timing requirements specified within the pcf file. The par command outputs the placed and routed physical design to an ncd file. An example of the par command is: $ par top_l...

Page 204

204 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 chapter 15: implementing the design r in addition, use the following guidlines to determine the simulator type required: virtex-5 devices virtex-5 device designs incorporating a rocketio transceiver require either a ve...

Page 205: Interoperability

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 205 ug155 march 24, 2008 r appendix a core verification, compliance, and interoperability verification the ethernet 1000base-x pcs/pma or sgmii core has been verified with extensive simulation and hardware verification. Simulation a highly par...

Page 206

206 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix a: core verification, compliance, and interoperability r.

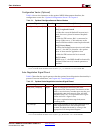

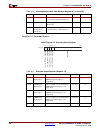

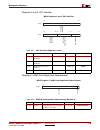

Page 207: Core Latency

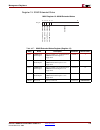

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 207 ug155 march 24, 2008 r appendix b core latency core latency the standalone core does not meet all the latency requirements specified in ieee 802.3 due to the latency of the elastic buffers in both tbi and rocketio transceiver versions. How...

Page 208

208 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix b: core latency r latency for 1000base-x pcs and pma using a rocketio transceiver these measurements are for the core only–they do not include the latency through the virtex-ii pro or virtex-4 mgt, virtex-5 gt...

Page 209: Value

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 209 ug155 march 24, 2008 r appendix c calculating the dcm fixed phase shift value requirement for dcm phase shifting a dcm is used in the clock path to meet the input setup and hold requirements when using the core with a tbi (see chapter 6, “...

Page 210

210 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix c: calculating the dcm fixed phase shift value r phase shift values must be tested; increments of 4 (52, 56, 60, etc.) correspond to roughly one dcm tap, and consequently provide an appropriate step size. It i...

Page 211: 1000Base-X State Machines

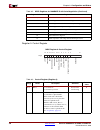

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 211 ug155 march 24, 2008 r appendix d 1000base-x state machines this appendix is intended to serve as a reference for the basic operation of the 1000base-x ieee 802.3 clause 36 transmitter and receiver state machines. Introduction table d-1 il...

Page 212: Start of Frame Encoding

212 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix d: 1000base-x state machines r start of frame encoding the even transmission case figure d-1 illustrates the translation of gmii encoding into the code-group stream performed by the pcs transmit engine. This s...

Page 213

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 213 ug155 march 24, 2008 start of frame encoding r reception of the even case figure d-2 illustrates the reception of the in-bound code-group stream, received either serially using the rocketio transceiver, or in parallel across the tbi, and t...

Page 214

214 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix d: 1000base-x state machines r reception of the odd case figure d-4 illustrates the reception of the in-bound code-group stream, received either serially using the rocketio transceiver, or in parallel across t...

Page 215: End of Frame Encoding

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 215 ug155 march 24, 2008 end of frame encoding r preamble shrinkage as previously described, a single byte of preamble can be lost across the 1000base-x system (the actual loss occurs in the 1000base-x pcs transmitter state machine). • there i...

Page 216

216 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix d: 1000base-x state machines r reception of the even case figure d-6 illustrates the reception of the in-bound code-group stream, received either serially using the rocketio transceiver, or in parallel across ...

Page 217

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 217 ug155 march 24, 2008 end of frame encoding r note: the first idle to follow the frame termination sequence will be a /i1/ if the frame ended with positive running disparity or a /i2/ if the frame ended with negative running disparity. This...

Page 218

218 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix d: 1000base-x state machines r.

Page 219: Introduction

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 219 ug155 march 24, 2008 r appendix e rx elastic buffer specifications this appendix is intended to serve as a reference for the rx elastic buffer sizes used in the core, and the related maximum frame sizes that can be used without causing a b...

Page 220

220 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix e: rx elastic buffer specifications r virtex-ii pro and virtex-5 devices consider the virtex-ii pro and virtex-5 fpga example, where the shaded area represents the usable buffer availability for the duration o...

Page 221

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 221 ug155 march 24, 2008 rx elastic buffers: depths and maximum frame sizes r virtex-4 fx consider the virtex-4 fx case also illustrated in figure e-1 . The thresholds are different to that of the virtex-ii pro/virtex-5 case, but the overall s...

Page 222

222 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix e: rx elastic buffer specifications r sgmii fabric rx elastic buffer figure e-2 illustrates the alternative fpga fabric rx elastic buffer depth and thresholds in virtex-ii pro, virtex-4 fx and virtex-5 lxt dev...

Page 223

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 223 ug155 march 24, 2008 rx elastic buffers: depths and maximum frame sizes r tbi rx elastic buffer for sgmii / dynamic switching the rx elastic buffer used for the sgmii or dynamic standards switching is identical to the method use in “sgmii ...

Page 224: Clock Correction

224 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix e: rx elastic buffer specifications r note that this analysis assumes that the buffer is approximately at the half-full level at the start of the frame reception. As illustrated, there are two locations of unc...

Page 225

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 225 ug155 march 24, 2008 clock correction r idle character removal at 100 mbps (sgmii) at sgmii, 100 mbps, each byte is repeated 10 times. This also applies to the interframe gap period. For this reason, the minimum of 8 bytes for the 1 gbps c...

Page 226: Jumbo Frame Reception

226 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix e: rx elastic buffer specifications r maximum frame sizes for sustained frame reception sustained frame reception refers to the maximum size of frames which can be continuously received when each frame is sepa...

Page 227: Debugging Guide

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 227 ug155 march 24, 2008 r appendix f debugging guide this appendix provides assistance for debugging the core within a system. For additional help, contact xilinx by submitting a webcase at support.Xilinx.Com/ . General checks • ensure that a...

Page 228

228 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix f: debugging guide r if data is being transmitted and received between the core and its link partner, but with a high rate of packet loss, see “problems with a high bit error rate.” problems with auto-negotiat...

Page 229

Ethernet 1000base-x pcs/pma or sgmii v9.1 www.Xilinx.Com 229 ug155 march 24, 2008 problems with a high bit error rate r rocketio transceiver specific when using a rocketio transceiver, perform these additional checks: • ensure that the polarities of the txn/txp and rxn/rxp lines are not reversed. If...

Page 230

230 www.Xilinx.Com ethernet 1000base-x pcs/pma or sgmii v9.1 ug155 march 24, 2008 appendix f: debugging guide r rocketio transceiver specific checks perform these additional checks when using a rocketio transceiver: • directly monitor the following ports of the rocketio by attaching error counters t...