- DL manuals

- Xilinx

- Computer Hardware

- LogiCORE IP CAN 3.2

- Getting Started Manual

Xilinx LogiCORE IP CAN 3.2 Getting Started Manual

Summary of LogiCORE IP CAN 3.2

Page 1

Logicore™ ip can v3.2 getting started guide ug186 april 19, 2010

Page 2

Can getting started guide www.Xilinx.Com ug186 april 19, 2010 xilinx is providing this product documentation, hereinafter “information,” to you “as is” with no warranty of any kind, express or implied. Xilinx makes no representation that the information, or any particular implementation thereof, is ...

Page 3: Table of Contents

Can getting started guide www.Xilinx.Com 3 ug186 april 19, 2010 schedule of figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 preface: about this guide guide contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 4

4 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design directory and file contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5: Schedule of Figures

Can getting started guide www.Xilinx.Com 5 ug186 april 19, 2010 chapter 1: introduction chapter 2: licensing the core chapter 3: quick start example design figure 3-1: example design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 figure 3-2...

Page 6

6 www.Xilinx.Com can getting started guide ug186 april 19, 2010

Page 7: About This Guide

Can getting started guide www.Xilinx.Com 7 ug186 april 19, 2010 preface about this guide the can v3.2 getting started guide provides information about generating the logicore™ ip can core, customizing and simulating the core with the provided example design, and running the design files through impl...

Page 8

8 www.Xilinx.Com can getting started guide ug186 april 19, 2010 preface: about this guide online document the following linking conventions are used in this document: italic font variables in a syntax statement for which you must supply values ngdbuild design_name references to other manuals see the...

Page 9: Introduction

Can getting started guide www.Xilinx.Com 9 ug186 april 19, 2010 chapter 1 introduction the logicore™ ip can v3.2 core is a compact, full-featured targeted design platform that conforms to iso 11898-1, can2.0a and can2.0b standards. Bit rates of up to 1 mbps are supported. The core size can be optimi...

Page 10: Additional Core Resources

10 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 1: introduction recommended design experience although the can core is a fully-verified targeted design platform, the challenge associated with implementing a complete can design varies, depending on the application requirement...

Page 11: Licensing The Core

Can getting started guide www.Xilinx.Com 11 ug186 april 19, 2010 chapter 2 licensing the core this chapter provides instructions for obtaining a license for the can core, which you must do before using the core in your designs. The can core is provided under the terms of the xilinx logicore site lic...

Page 12: Obtaining Your License Key

12 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 2: licensing the core full the full license key is available when you purchase the core and provides full access to all core functionality both in simulation and in hardware, including: • gate-level functional simulation suppor...

Page 13: Quick Start Example Design

Can getting started guide www.Xilinx.Com 13 ug186 april 19, 2010 chapter 3 quick start example design this chapter provides instructions to generate a can core quickly, run the design through implementation with the xilinx tools, and simulate the example design using the provided demonstration test ...

Page 14: Generating The Core

14 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 3: quick start example design generating the core this section describes how to generate a can core with default values using the xilinx core generator™ tool. To generate the core: 1. Start the core generator tool. For help sta...

Page 15

Can getting started guide www.Xilinx.Com 15 ug186 april 19, 2010 implementing the example design 7. In the component name field, enter a name for the core instance. This example uses the name quickstart. 8. After selecting the parameters from the gui screens, click finish. The core and its supportin...

Page 16

16 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 3: quick start example design functional simulation this section provides instructions for running a functional simulation of the can core using either vhdl or verilog. Functional simulation models are provided when the core is...

Page 17: Detailed Example Design

Can getting started guide www.Xilinx.Com 17 ug186 april 19, 2010 chapter 4 detailed example design this chapter provides detailed information about the example design, including a description of files and the directory structure generated by the xilinx core generator™ software, the purpose and conte...

Page 18: Directory and File Contents

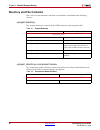

18 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design directory and file contents the can v3.2 core directories and their associated files are defined in the following sections. The contains all the core generator software project files. / the directory ...

Page 19

Can getting started guide www.Xilinx.Com 19 ug186 april 19, 2010 directory and file contents example design the example design directory contains the example design files provided with the core. /doc the doc directory contains the pdf documentation provided with the core. Table 4-3: example design d...

Page 20

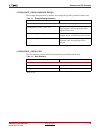

20 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design /implement the implement directory contains the core implementation script files. Generated for full- system hardware evaluation and full license types. /implement/results the results directory is cre...

Page 21

Can getting started guide www.Xilinx.Com 21 ug186 april 19, 2010 directory and file contents /simulation/functional the functional directory contains functional simulation scripts provided with the core. Table 4-8: functional directory name description //simulation/functional simulate_mti.Do a macro...

Page 22

22 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design simulation/timing the timing simulation directory is generated only for full-system hardware evaluation and full-license types. Table 4-9: timing directory name description //simulation/timing simulat...

Page 23: Implementation Scripts

Can getting started guide www.Xilinx.Com 23 ug186 april 19, 2010 implementation scripts implementation scripts note: present only with a full license. The implementation script is either a shell script(.Sh) or batch file (.Bat) that processes the example design through the xilinx tool flow. It is lo...

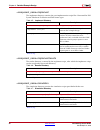

Page 24: Example Design Configuration

24 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design timing simulation note: present only with a full license. The test scripts are a modelsim or a cadence ies macro that automates the simulation of the test bench. They are located in: //simulation/timi...

Page 25: Demonstration Test Bench

Can getting started guide www.Xilinx.Com 25 ug186 april 19, 2010 demonstration test bench demonstration test bench figure 4-2 illustrates the demonstration test bench. Test bench functionality the demonstration test bench is a straightforward vhdl or verilog file to exercise the example design and t...

Page 26

26 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design • five messages are written in sequence: 1. The first message is written to the txhpb and is a standard data frame. 2. The second message is written to the tx fifo and is a standard data frame. 3. The...

Page 27

Can getting started guide www.Xilinx.Com 27 ug186 april 19, 2010 demonstration test bench • after the fourth message is transmitted and received, the interrupt enable register is written to enable interrupts for txok, rxok and txbfll. This register is read from and the value read is compared with th...

Page 28

28 www.Xilinx.Com can getting started guide ug186 april 19, 2010 chapter 4: detailed example design.