- DL manuals

- Xilinx

- Computer Hardware

- LogiCORE IP MAC v8.5

- User Manual

Xilinx LogiCORE IP MAC v8.5 User Manual

Summary of LogiCORE IP MAC v8.5

Page 1

R -- discontinued product -- logicore™ ip 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009.

Page 2

Www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 -- discontinued product -- xilinx is providing this product documentation, hereinafter “information,” to you “as is” with no warranty of any kind, express or implied. Xilinx makes no representation that the information, or an...

Page 3: Revision History

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com ug144 april 24, 2009 -- discontinued product -- revision history the following table shows the revision history for this document. Date version revision 09/30/04 1.0 initial xilinx release. 04/28/05 2.0 updated to 1-gigabit ethernet mac version 6...

Page 4

Www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 -- discontinued product --.

Page 5: Table of Contents

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com ug144 april 24, 2009 -- discontinued product -- schedule of figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 schedule of tables . . . . . . . . . . . . . . . . . . . . ....

Page 6

Www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 r -- discontinued product -- chapter 4: designing with the core general design guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 design steps . . . . . . . . . . ....

Page 7

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com ug144 april 24, 2009 r -- discontinued product -- connecting the mdio to an internally integrated phy . . . . . . . . . . . . . . . . . . . . . . . . 76 connecting the mdio to an external phy . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 8

Www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 r -- discontinued product -- chapter 12: implementing your design pre-implementation simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123 using the simulation model . . . . . ...

Page 9: Schedule of Figures

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 9 ug144 april 24, 2009 -- discontinued product -- chapter 1: introduction chapter 2: core architecture figure 2-1: block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 figure 2...

Page 10

10 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 r -- discontinued product -- chapter 7: using the physical side interface figure 7-1: external gmii transmitter logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 figure 7-2: external gmii r...

Page 11

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 11 ug144 april 24, 2009 r -- discontinued product -- chapter 11: interfacing to other cores figure 11-1: 1-gigabit ethernet mac extended to include 1000base-x pcs with tbi 114 figure 11-2: 1-gigabit ethernet mac extended to include 1000base-x pcs...

Page 12

12 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 r -- discontinued product --.

Page 13: Schedule of Tables

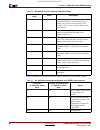

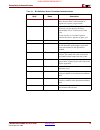

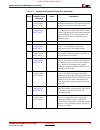

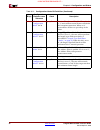

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 13 ug144 april 24, 2009 -- discontinued product -- chapter 1: introduction chapter 2: core architecture table 2-1: transmitter client interface signal pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 table 2-2: receive clien...

Page 14

14 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 r -- discontinued product -- table 8-8: unicast address word 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 table 8-9: unicast address word 1 . . . . . . . . . . . . . . . ...

Page 15: About This Guide

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 15 ug144 april 24, 2009 r -- discontinued product -- preface about this guide the logicore™ ip 1-gigabit ethernet mac user guide provides information about generating the core, customizing and simulating the core utilizing the provided example de...

Page 16: Conventions

16 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 preface: about this guide r -- discontinued product -- conventions this document uses the following conventions. An example illustrates each convention. Typographical the following typographical conventions are used in thi...

Page 17

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 17 ug144 april 24, 2009 conventions r -- discontinued product -- online document the following linking conventions are used in this document: list of acronyms the following table describes acronyms used in this manual. Convention meaning or use e...

Page 18

18 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 preface: about this guide r -- discontinued product -- ncd native circuit description ngc native generic circuit ngd native generic database ns nanoseconds pcb printed circuit board pcs physical coding sublayer phy physica...

Page 19: Introduction

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 19 ug144 april 24, 2009 r -- discontinued product -- chapter 1 introduction the 1-gigabit ethernet mac (gemac) core is a fully verified solution that supports verilog-hdl and vhdl. In addition, the example design provided with the core is provide...

Page 20: Specifications

20 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 1: introduction r -- discontinued product -- specifications • ieee 802.3 2005 • reduced gigabit media independent interface (rgmii) version 2.0 technical support for technical support, see support.Xilinx.Com/ . Que...

Page 21: Core Architecture

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 21 ug144 april 24, 2009 r -- discontinued product -- chapter 2 core architecture this chapter describes the gemac core architecture, including the major functional blocks and all interfaces. System overview figure 2-1 illustrates a block diagram ...

Page 22

22 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 2: core architecture r -- discontinued product -- core components transmit engine the transmit engine accepts ethernet frame data from the client transmitter interface, adds the preamble field to the start of the f...

Page 23: Core Interfaces

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 23 ug144 april 24, 2009 core interfaces r -- discontinued product -- core interfaces gmac core with optional management interface figure 2-2 shows the pinout for the gemac core using the optional management interface. The interface is unchanged, ...

Page 24

24 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 2: core architecture r -- discontinued product -- gmac core without management interface and with address filter figure 2-3 shows the pinout for the gemac core when the optional management interface is omitted and ...

Page 25

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 25 ug144 april 24, 2009 core interfaces r -- discontinued product -- gemac core without management interface and without address filter figure 2-4 shows the pinout for the gemac core when the optional management interface is omitted and the optio...

Page 26

26 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 2: core architecture r -- discontinued product -- all ports of the core are internal connections in fpga fabric. An hdl example design is delivered with the core that will add ibufs, obufs, and iob flip-flops to th...

Page 27

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 27 ug144 april 24, 2009 core interfaces r -- discontinued product -- receiver interface table 2-2 describes the client-side receiver signals of the gemac core. These signals are used by to transfer data to the client. See “receiving inbound frame...

Page 28

28 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 2: core architecture r -- discontinued product -- management interface (optional) table 2-4 describes the optional signals used by the client to access the management features of the gemac core. See “using the opti...

Page 29

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 29 ug144 april 24, 2009 core interfaces r -- discontinued product -- configuration vector (optional) table 2-6 describes the alternative to the optional management interface signals. The configuration vector uses direct inputs to the core to repl...

Page 30

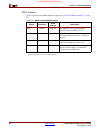

30 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 2: core architecture r -- discontinued product -- mdio interface table 2-9 describes the mdio interface signals. See “using the mdio interface,” on page 76 . Table 2-9: mdio interface signal pinout signal direction...

Page 31: Generating The Core

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 31 ug144 april 24, 2009 r -- discontinued product -- chapter 3 generating the core the gemac core is generated through the xilinx core generator™ using a graphical user interface (gui). This chapter describes the gui options used to generate and ...

Page 32

32 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 3: generating the core r -- discontinued product -- component name the component name is used as the base name of the output files generated for the core. Names must begin with a letter and must be composed from th...

Page 33: Output Generation

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 33 ug144 april 24, 2009 output generation r -- discontinued product -- output generation the output files generated from the core generator tool are placed in the core generator project directory. The list of output files includes the following i...

Page 34

34 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 3: generating the core r -- discontinued product --.

Page 35: Designing With The Core

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 35 ug144 april 24, 2009 r -- discontinued product -- chapter 4 designing with the core this chapter provides general guidelines for creating designs using the gemac core. To work with the example design included with the gemac core, see the 1-gig...

Page 36

36 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 4: designing with the core r -- discontinued product -- using the example design as a starting point, you can do the following: • edit the hdl top level of the example design file to: ♦ change the clocking scheme. ...

Page 37

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 37 ug144 april 24, 2009 general design guidelines r -- discontinued product -- implementing the 1-gigabit ethernet mac in your application the example design can be studied as an example of how to do the following: • instantiate the core from hdl...

Page 38

38 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 4: designing with the core r -- discontinued product -- see also appendix c, “calculating dcm phase-shifting” to meet spartan-3, spartan-3e and spartan-3a device setup and hold requirements for external gmii. Keep ...

Page 39: Receiving Inbound Frames

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 39 ug144 april 24, 2009 r -- discontinued product -- chapter 5 using the client side data path this chapter provides general guidelines for creating designs using the gemac core, including a detailed description of each client-side data flow inte...

Page 40

40 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- frame parameters (destination address, source address, length/type and optionally fcs) are supplied on the data bus according to the timing diagram. I...

Page 41

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 41 ug144 april 24, 2009 receiving inbound frames r -- discontinued product -- frame reception with errors figure 5-2 illustrates an unsuccessful frame reception (for example, a fragment frame or a frame with an incorrect fcs). In this case, the r...

Page 42

42 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- client-supplied fcs passing if the gemac core is configured to pass the fcs field to the client (see “configuration registers,” on page 78 ), this is ...

Page 43

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 43 ug144 april 24, 2009 receiving inbound frames r -- discontinued product -- maximum permitted frame length the maximum legal length of a frame specified in ieee 802.3-2005 is 1518 bytes for non- vlan tagged frames. Vlan tagged frames may be ext...

Page 44

44 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- address filter if the optional address filter is included in the core, the mac is able to reject frames that do not contain a known address in their d...

Page 45

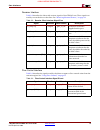

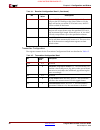

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 45 ug144 april 24, 2009 receiving inbound frames r -- discontinued product -- table 5-2: bit definition for the receiver statistics vector rx_statistics_vector bit(s) name description 27 address match if the optional address filter is included in...

Page 46

46 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- table 5-3 provides conversion information against previous versions of the gemac. 20 out of bounds asserted if the previous frame exceeded the specifi...

Page 47: Transmitting Outbound Frames

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 47 ug144 april 24, 2009 transmitting outbound frames r -- discontinued product -- transmitting outbound frames ethernet frames to be transmitted are presented to the client logic on the transmitter subset of the client-side interface. For port de...

Page 48

48 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- client-supplied fcs passing the transmission timing depicted in figure 5-7 shows the gemac core configured to have the fcs field passed in by the clie...

Page 49

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 49 ug144 april 24, 2009 transmitting outbound frames r -- discontinued product -- vlan tagged frames figure 5-9 illustrates transmission of a vlan tagged frame (if enabled). The handshaking signals across the interface do not change; however, the...

Page 50

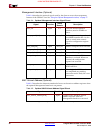

50 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- transmitter statistics vector the statistics for the transmitted frame are contained within the tx_statistic_vector. The vector is driven synchronousl...

Page 51

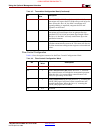

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 51 ug144 april 24, 2009 transmitting outbound frames r -- discontinued product -- table 5-4: bit definition for the transmitter statistics vector tx_statistics_vector bit(s) name description 31 pause frame asserted if the previous frame was a pau...

Page 52

52 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 5: using the client side data path r -- discontinued product -- table 5-5 provides conversion information against previous versions of the gemac. Table 5-5: tx statistics conversion to previous core gemac core vers...

Page 53: Using Flow Control

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 53 ug144 april 24, 2009 r -- discontinued product -- chapter 6 using flow control this chapter describes the operation of the flow-control logic of the gemac core. The flow control block is designed to clause 31 of the ieee 802.3-2005 standard. T...

Page 54

54 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 6: using flow control r -- discontinued product -- the user mac on the left side has a reference clock slightly slower than the nominal 125 mhz. The link partner mac on the right side has a reference clock slightly...

Page 55

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 55 ug144 april 24, 2009 overview of flow control r -- discontinued product -- pause control frames control frames are a unique type of ethernet frame, defined in clause 31 of the ieee 802.3- 2005 standard. Control frames are differentiated from o...

Page 56

56 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 6: using flow control r -- discontinued product -- flow control operation of the gemac transmitting a pause control frame core-initiated pause request if the gemac core is configured to support transmit flow contro...

Page 57

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 57 ug144 april 24, 2009 flow control operation of the gemac r -- discontinued product -- receiving a pause control frame core initiated response to a pause request an error free control frame is a received frame matching the format of figure 6-2 ...

Page 58

58 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 6: using flow control r -- discontinued product -- flow control implementation example this section provides a basic overview of a flow control implementation, using figure 6-1 as a sample. To summarize the example...

Page 59

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 59 ug144 april 24, 2009 flow control implementation example r -- discontinued product -- operation figure 6-4 illustrates the fifo occupancy over a period of time. The following describes the sequence of flow control operation. 1. The average fif...

Page 60

60 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 6: using flow control r -- discontinued product --.

Page 61: Implementing External Gmii

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 61 ug144 april 24, 2009 r -- discontinued product -- chapter 7 using the physical side interface this chapter provides general guidelines for creating designs using the physical side interface of the gemac core. The physical side interface implem...

Page 62

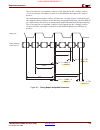

62 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- figure 7-1: external gmii transmitter logic ipad ibufg iob logic gtx_clk bufg gtx_clk_bufg gmii_tx_clk obuf fddrrse iob logic opad d q d q '0' '1' d...

Page 63

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 63 ug144 april 24, 2009 implementing external gmii r -- discontinued product -- gmii receiver logic spartan-3, spartan-3e, spartan-3a and virtex-4 devices a dcm must be used on the gmii_rx_clk clock path, as illustrated in figure 7-2 , to meet th...

Page 64

64 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- dcm reset circuitry a dcm reset module, not illustrated in figure 7-2 , is also present and is instantiated in the example design next to the dcm. S...

Page 65

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 65 ug144 april 24, 2009 implementing external gmii r -- discontinued product -- virtex-5 devices an iodelay component may be used on the clock, data and control paths, as illustrated in figure 7-3 . These can be used to either shift the input clo...

Page 66: Implementing External Rgmii

66 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- implementing external rgmii the hdl example design delivered with the core implements an external rgmii when rgmii is selected from the core generat...

Page 67

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 67 ug144 april 24, 2009 implementing external rgmii r -- discontinued product -- figure 7-4 shows that the output transmitter signals are registered on gtx_clk_bufg, in the fpga fabric, including the encoded rgmii_tx_ctl_int signal, derived from ...

Page 68

68 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- the logic required to forward the transmitter clock is also shown: this uses an oddr register so that the clock signal produced incurs exactly on th...

Page 69

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 69 ug144 april 24, 2009 implementing external rgmii r -- discontinued product -- virtex-5 devices the same logic that is used in figure 7-5 can also be used without modification for virtex-5 devices. However, an alternative solution has been adop...

Page 70

70 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- the logic required to forward the transmitter clock is also shown. It has matching logic to the data and control signals to provide a known relation...

Page 71

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 71 ug144 april 24, 2009 implementing external rgmii r -- discontinued product -- figure 7-7: external rgmii receiver logic rgmii_rxc ibufg iob logic ipad rgmii_rxd[0] ibuf ipad d q 1-gigabit ethernet mac core gmii_rxd_reg[0] gmii_rx_dv_reg gmii_r...

Page 72

72 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- virtex-4 devices figure 7-8 shows using the physical receiver interface of the core to create an external rgmii in a virtex-4 device. The signal nam...

Page 73

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 73 ug144 april 24, 2009 implementing external rgmii r -- discontinued product -- • this can be achieved by connecting the reset_200ms signal to the reset_200ms_in signal at any level of example design hdl hierarchy. Figure 7-8: external rgmii rec...

Page 74

74 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- virtex-5 devices figure 7-9 shows using the physical receiver interface of the core to create an external rgmii in a virtex-5 device. The signal nam...

Page 75

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 75 ug144 april 24, 2009 implementing external rgmii r -- discontinued product -- rgmii inband status decoding logic the inband status decoding logic is common to all device families. Figure 7-10 illustrates the decoding of rgmii inband status inf...

Page 76: Using The Mdio Interface

76 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 7: using the physical side interface r -- discontinued product -- using the mdio interface the mdio interface is accessed through the optional management interface and is typically connected to the mdio port of a p...

Page 77: Configuration and Status

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 77 ug144 april 24, 2009 r -- discontinued product -- chapter 8 configuration and status this chapter provides general guidelines for configuring and monitoring the gemac core, including a detailed description of the client-side management interfa...

Page 78

78 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- configuration registers after a power-up or system reset, the client may reconfigure the core parameters using their defaults. Configuration changes can be w...

Page 79

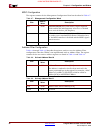

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 79 ug144 april 24, 2009 using the optional management interface r -- discontinued product -- receiver configuration the register contents for the two receiver configuration words are shown in table 8-3 and table 8-4 . Table 8-3: receiver configur...

Page 80

80 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- transmitter configuration the register contents for the transmitter configuration word are described in table 8-5 . 29 0 in-band fcs enable when this bit is ...

Page 81

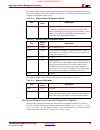

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 81 ug144 april 24, 2009 using the optional management interface r -- discontinued product -- flow control configuration table 8-6 lists the register contents for the flow control configuration word. 29 0 in-band fcs enable when this bit is ‘1,’ t...

Page 82

82 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- mdio configuration the register contents for the management configuration word are described in table 8-7 . Address filter configuration table 8-8 through ta...

Page 83

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 83 ug144 april 24, 2009 using the optional management interface r -- discontinued product -- the address filter can be programmed to respond to four separate additional addresses stored in an address table in the address filter. Table 8-10 and ta...

Page 84

84 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- reading from the configuration register words is similar, but the upper host_opcode bit should be ‘1,’ as shown in figure 8-2 . In this case, the contents of...

Page 85

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 85 ug144 april 24, 2009 using the optional management interface r -- discontinued product -- accessing the address table to write to a specific entry in the address table, you must first write the least significant 32- bits of the address into th...

Page 86

86 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- mdio interface introduction to mdio the mdio interface for 1 gbps operation (and slower speeds) is defined in ieee 802.3 clause 22. This is a two wire interf...

Page 87

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 87 ug144 april 24, 2009 using the optional management interface r -- discontinued product -- there are two different transaction types of mdio for write and read. They are described in this section. Abbreviations used the following abbreviations ...

Page 88

88 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- read transaction figure 8-7 shows a read transaction; this is defined by op=”10”. The addressed mmd (phyad) device returns the 16-bit word from the register ...

Page 89

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 89 ug144 april 24, 2009 using the optional management interface r -- discontinued product -- figure 8-8 shows access to the mdio interface through the management interface. For mdio transactions, the following applies: • host_miim_sel is ‘1’ • ho...

Page 90

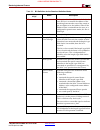

90 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- access without the management interface if the optional management interface is omitted from the core, all of the relevant configuration settings described i...

Page 91

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 91 ug144 april 24, 2009 access without the management interface r -- discontinued product -- 53 “receiver configuration word 1” bit 31 n/a receiver reset . When this bit is ‘1,’ the receiver is held in reset. This signal is an input to the reset ...

Page 92

92 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 8: configuration and status r -- discontinued product -- 62 “flow control configuration word” bit 30 gtx_clk receive flow control enable . When this bit is ‘1,’ received flow control frames will inhibit the transmi...

Page 93: Constraining The Core

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 93 ug144 april 24, 2009 r -- discontinued product -- chapter 9 constraining the core this chapter defines the gemac core constraint requirements. An example ucf that implements the constraints defined in this chapter is provided with the hdl exam...

Page 94

94 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- period constraints for clock nets gtx_clk the clock provided to gtx_clk must be constrained for a clock frequency of 125 mhz. The following ucf syntax shows the...

Page 95

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 95 ug144 april 24, 2009 required constraints r -- discontinued product -- the ucf syntax which follows targets the mdio logic flip-flops and groups them together. Reduced clock period constraints are then applied. ################################...

Page 96

96 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- timespecs for reset logic within the core internally, the core is divided into clock/reset domains that group elements with common clock and reset signals. The ...

Page 97

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 97 ug144 april 24, 2009 required constraints r -- discontinued product -- gmii input setup/hold timing figure 9-1 and table 9-1 illustrate the setup and hold time window for the input gmii signals. This is the worst-case data valid window present...

Page 98

98 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- the fixed phase-shift is applied to the dcm using the following ucf syntax: inst *gmii_interface/gmii_rxc_dcm clkout_phase_shift = fixed; inst *gmii_interface/g...

Page 99

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 99 ug144 april 24, 2009 required constraints r -- discontinued product -- understanding timing reports for gmii setup/hold timing non-virtex-5 devices setup and hold results for the gmii input bus can be found in the data sheet section of the tim...

Page 100

100 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- data sheet report: ----------------- all values displayed in nanoseconds (ns) setup/hold to clock gmii_rx_clk ------------+------------+------------+----------...

Page 101

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 101 ug144 april 24, 2009 required constraints r -- discontinued product -- the implementation requires 7.554 ns of hold. Figure 9-2 illustrates that this represents a figure of -0.446 ns relative to the following rising edge of the clock (since t...

Page 102

102 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- the rgmii v2.0 is a 1.5 volt signal-level interface. The 1.5 volt hstl class i selectio standard is used for rgmii interface pins. Use the following constraint...

Page 103

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 103 ug144 april 24, 2009 required constraints r -- discontinued product -- inst "rgmii_rxd>" tnm = in_rgmii; inst "rgmii_rx_ctl" tnm = in_rgmii; timegrp "ddr_rising" = ffs; timegrp "ddr_falling" = falling ffs; timegrp "in_rgmii" offset = in 1.1 n...

Page 104

104 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- inst *rgmii_interface/delay_rgmii_tx_clk idelay_type = “fixed”; inst *rgmii_interface/delay_rgmii_tx_clk odelay_value = 25; inst *rgmii_interface/delay_rgmii_t...

Page 105

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 105 ug144 april 24, 2009 required constraints r -- discontinued product -- understanding timing reports for rgmii setup/hold timing non-virtex-5 devices setup and hold results for the rgmii input bus can be found in the data sheet section of the ...

Page 106

106 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product -- data sheet report: ----------------- all values displayed in nanoseconds (ns) setup/hold to clock rgmii_rxc ------------+------------+------------+------------...

Page 107

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 107 ug144 april 24, 2009 required constraints r -- discontinued product -- this is less than the 1 ns required, so there is slack. Equally for the –ve edge, we have –11.179 ns of setup—this edge is at time 12 ns and therefore this equates to a se...

Page 108

108 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 9: constraining the core r -- discontinued product --.

Page 109: Clocking and Resetting

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 109 ug144 april 24, 2009 r -- discontinued product -- chapter 10 clocking and resetting this chapter describes clock management considerations that are associated with implementing the gemac core. It describes the clock management logic for all i...

Page 110: Multiple Cores

110 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 10: clocking and resetting r -- discontinued product -- with rgmii standard clocking scheme figure 10-2 illustrates the clock management used with an external rgmii interface. All clocks illustrated have a frequen...

Page 111

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 111 ug144 april 24, 2009 multiple cores r -- discontinued product -- note: although not illustrated, if the optional management interface is used, host_clk can also be shared between cores. With rgmii figure 10-4 illustrates sharing clock resourc...

Page 112: Reset Conditions

112 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 10: clocking and resetting r -- discontinued product -- reset conditions internally, the core is divided up into clock/reset domains that group together elements with common clock and reset signals. The reset circ...

Page 113: Interfacing to Other Cores

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 113 ug144 april 24, 2009 r -- discontinued product -- chapter 11 interfacing to other cores ethernet 1000base-x pcs/pma or sgmii core the gemac core can be integrated in a single device with the ethernet 1000base-x pcs/pma or sgmii core to extend...

Page 114

114 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 11: interfacing to other cores r -- discontinued product -- integration to provide 1000base-x pcs with tbi figure 11-1 illustrates the connections and clock management logic required to interface the gemac core to...

Page 115

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 115 ug144 april 24, 2009 ethernet 1000base-x pcs/pma or sgmii core r -- discontinued product -- integration to provide 1000base-x pcs and pma using a rocketio transceiver virtex-4 devices figure 11-2 illustrates the connections and clock manageme...

Page 116

116 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 11: interfacing to other cores r -- discontinued product -- figure 11-2 illustrates the following: • direct internal connections are made between the gmii interfaces between the two cores. • if the gemac has been ...

Page 117

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 117 ug144 april 24, 2009 ethernet 1000base-x pcs/pma or sgmii core r -- discontinued product -- virtex-5 lxt and sxt devices figure 11-3 illustrates the connections and clock management logic required to interface the gemac core to the ethernet 1...

Page 118

118 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 11: interfacing to other cores r -- discontinued product -- • due to the embedded receiver elastic buffer in the ethernet 1000base-x pcs/pma or sgmii core, the entire gmii is synchronous to a single clock domain. ...

Page 119: Ethernet Statistics Core

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 119 ug144 april 24, 2009 ethernet statistics core r -- discontinued product -- features of this configuration include: • direct internal connections are made between the gmii interfaces between the two cores. • if the gemac has been generated wit...

Page 120

120 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 11: interfacing to other cores r -- discontinued product -- figure 11-5 illustrates connecting the ethernet statistics core to the mac. Figure 11-5: interfacing the ethernet statistics to the 1-gigabit ethernet ma...

Page 121

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 121 ug144 april 24, 2009 ethernet statistics core r -- discontinued product -- the management interfaces of the two cores can be shared by avoiding bus conflict, as follows: • selecting a different address range for the statistics to that of the ...

Page 122

122 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 11: interfacing to other cores r -- discontinued product --.

Page 123: Implementing Your Design

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 123 ug144 april 24, 2009 r -- discontinued product -- chapter 12 implementing your design this chapter describes how to simulate and implement your design containing the gemac core. Pre-implementation simulation a unit delay structural model of t...

Page 124: Implementation

124 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 12: implementing your design r -- discontinued product -- to synthesize the design, run: $ xst -ifn top_level_module_name.Scr see the xst user guide for more information on creating project and synthesis script fi...

Page 125

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 125 ug144 april 24, 2009 post-implementation simulation r -- discontinued product -- placing-and-routing the design execute the par command to place-and-route your design logic components (mapped physical logic cells) contained within an ncd file...

Page 126

126 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 chapter 12: implementing your design r -- discontinued product -- using the model for information about setting up your simulator to use the pre-implemented model, see the xilinx synthesis and verification design guide in...

Page 127: Using The Client-Side Fifo

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 127 ug144 april 24, 2009 r -- discontinued product -- appendix a using the client-side fifo the example design provided with the gemac core contains a fifo used on the client- side of the core. The source code for the fifo is provided, and may be...

Page 128: Interfaces

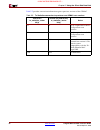

128 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 appendix a: using the client-side fifo r -- discontinued product -- interfaces transmit fifo table a-1 describes the transmit fifo client interface. For more information on the mac client interface, see “transmitting outb...

Page 129

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 129 ug144 april 24, 2009 interfaces r -- discontinued product -- receive fifo table a-3 describes the receive fifo client interface. For more information on the mac client interface, see “receiving inbound frames,” on page 39 . Table a-4 describe...

Page 130

130 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 appendix a: using the client-side fifo r -- discontinued product -- overview of locallink interface data flow data is transferred on the locallink interface from source to destination, with the flow being governed by the ...

Page 131: Functional Operation

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 131 ug144 april 24, 2009 functional operation r -- discontinued product -- functional operation clock requirements the fifo is designed to work with rx_clk and tx_clk running at mac clock speeds up to 125 mhz. The rx_ll_clock should be no slower ...

Page 132

132 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 appendix a: using the client-side fifo r -- discontinued product -- verilog the compiler directive full_duplex_only is defined to allow for removal of logic and performance constraints that are necessary only in half-dupl...

Page 133: Interoperability

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 133 ug144 april 24, 2009 r -- discontinued product -- appendix b core verification, compliance, and interoperability the gemac core has been verified with extensive simulation and hardware testing. Verification by simulation a highly parameteriza...

Page 134

134 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 appendix b: core verification, compliance, and interoperability r -- discontinued product --.

Page 135: Dcm Phase-Shifting

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 135 ug144 april 24, 2009 r -- discontinued product -- appendix c calculating dcm phase-shifting dcm phase-shifting a dcm is used in the receiver clock path to meet the input setup and hold requirements when using the core with an rgmii (see “impl...

Page 136

136 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 appendix c: calculating dcm phase-shifting r -- discontinued product -- perform a complete sweep of phase-shift settings during your initial system test. Use only positive (0 to 255) phase-shift settings, and use a test r...

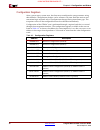

Page 137: Core Latency

1-gigabit ethernet mac v8.5 user guide www.Xilinx.Com 137 ug144 april 24, 2009 r -- discontinued product -- appendix d core latency transmit path latency as measured from a data octet accepted on tx_data[7:0] of the transmitter client-side interface, until that data octet appears on gmii_txd[7:0] of...

Page 138

138 www.Xilinx.Com 1-gigabit ethernet mac v8.5 user guide ug144 april 24, 2009 appendix d: core latency r -- discontinued product --.