- DL manuals

- Xilinx

- I/O Systems

- LogiCORE IP v1.02a

- Product Manual

Xilinx LogiCORE IP v1.02a Product Manual - Fixed Interval Timer, Fit

I/O Module v1.02a

8

PG052 October 16, 2012

Licensing and Ordering Information

Fixed Interval Timer, FIT

The Fixed Interval Timer generates a strobe signal at fixed intervals. The Fixed Interval

Timer asserts the output signal and generates an interrupt according to the selected

parameter values.

Programmable Interval Timer, PIT

The Programmable Interval Timer, PIT, has a configurable width from 1 to 32. The PIT

operation and period are controlled by software. An interrupt can be generated when the

timer lapses.

General Purpose Output, GPO

The General Purpose Output, GPO, drives I/O Module GPO output signals defined by the

value of the corresponding GPO register, programmable from software. The width and

initial value are defined by parameters.

General Purpose Input, GPI

The General Purpose Input, GPI, makes it possible for software to sample the value of the

I/O Module GPI input signals by reading the GPI register. The width and whether to

generate an interrupt are defined by parameters.

Interrupt Controller INTC

The Interrupt Controller handles both I/O module internal interrupt events and external

ones. The internal interrupt events originate from the UART, the Fixed Interval Timers, the

Programmable Interval Timers, or the General Purpose Inputs.

Licensing and Ordering Information

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado

Design Suite and ISE Design Suite Embedded Edition tools under the terms of the

.

Information about this and other Xilinx LogiCORE IP modules is available at the

page. For information on pricing and availability of other Xilinx

LogiCORE IP modules and tools, contact your

Summary of LogiCORE IP v1.02a

Page 1

Logicore ip i/o module v1.02a product guide pg052 october 16, 2012.

Page 2

I/o module v1.02a www.Xilinx.Com 2 pg052 october 16, 2012 table of contents section i: summary ip facts chapter 1: overview feature summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 licensing and ordering info...

Page 3

I/o module v1.02a www.Xilinx.Com 3 pg052 october 16, 2012 clock frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4

I/o module v1.02a www.Xilinx.Com 4 pg052 october 16, 2012 section i: summary ip facts overview product specification designing with the core.

Page 5: Introduction

I/o module v1.02a www.Xilinx.Com 5 pg052 october 16, 2012 product specification introduction the logicore™ i/o module is a highly integrated and light-weight implementation of a standard set of peripherals. The i/o module is a standalone version of the tightly coupled i/o module included in the logi...

Page 6

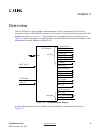

I/o module v1.02a www.Xilinx.Com 6 pg052 october 16, 2012 chapter 1 overview the i/o module is a light-weight implementation of a set of standard i/o functions commonly used in a microblaze™ processor sub-system. The input/output signals of the i/o module are shown in figure 1-1 . The detailed list ...

Page 7: Feature Summary

I/o module v1.02a www.Xilinx.Com 7 pg052 october 16, 2012 feature summary feature summary i/o bus the i/o bus provides a simple bus for accessing to external modules. The i/o bus is mapped in the microblaze memory space, with the i/o bus address directly reflecting the byte address used by microblaz...

Page 8: Fixed Interval Timer, Fit

I/o module v1.02a www.Xilinx.Com 8 pg052 october 16, 2012 licensing and ordering information fixed interval timer, fit the fixed interval timer generates a strobe signal at fixed intervals. The fixed interval timer asserts the output signal and generates an interrupt according to the selected parame...

Page 9: Standards

I/o module v1.02a www.Xilinx.Com 9 pg052 october 16, 2012 product specification chapter 2 product specification standards the i/o bus interface provided by the i/o module is fully compatible with the xilinx dynamic reconfiguration port (drp). For a detailed description of the drp, see the 7 series f...

Page 10: Throughput

I/o module v1.02a www.Xilinx.Com 10 pg052 october 16, 2012 product specification resource utilization data write to i/o module registers is performed the clock cycle after the address strobe is asserted. Data accesses to peripherals connected on the i/o bus take three clock cycles plus the number of...

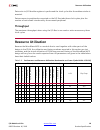

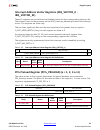

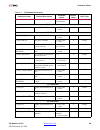

Page 11: Port Descriptions

I/o module v1.02a www.Xilinx.Com 11 pg052 october 16, 2012 product specification port descriptions port descriptions the i/o ports and signals for the i/o module are listed and described in table 2-3 . Table 2-3: i/o module i/o signals port name msb:lsb i/o description lmb signals lmb_abus 0:c_lmb_a...

Page 12

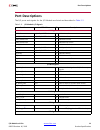

I/o module v1.02a www.Xilinx.Com 12 pg052 october 16, 2012 product specification port descriptions parameter - port dependencies the width of many of the i/o module signals depends on design parameters. The dependencies between the design parameters and i/o signals are shown in table 2-4 . Pitx_enab...

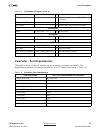

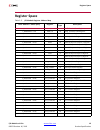

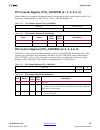

Page 13: Register Space

I/o module v1.02a www.Xilinx.Com 13 pg052 october 16, 2012 product specification register space register space table 2-5: i/o module register address map base address + offset (hex) register access type description c_baseaddr + 0x0 uart_rx r uart receive data register c_baseaddr + 0x4 uart_tx w uart...

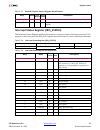

Page 14

I/o module v1.02a www.Xilinx.Com 14 pg052 october 16, 2012 product specification register space uart receive data register (uart_rx) this register contains data received by the uart. Reading this location results in reading the current word from the register. When a read request is issued without ha...

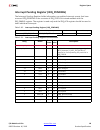

Page 15

I/o module v1.02a www.Xilinx.Com 15 pg052 october 16, 2012 product specification register space uart status register (uart_status) the uart status register contains the status of the receive and transmit registers, and if there are any errors. This is read only register. If a write request is issued...

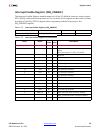

Page 16

I/o module v1.02a www.Xilinx.Com 16 pg052 october 16, 2012 product specification register space uart programmable baud rate register (uart_baud) this register sets the baud rate when using programmable baud rate. The initial value of the register is determined from the selected fixed baud rate c_uar...

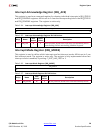

Page 17

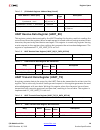

I/o module v1.02a www.Xilinx.Com 17 pg052 october 16, 2012 product specification register space interrupt status register (irq_status) the interrupt status register holds information on interrupt events that have occurred. The register is read-only and the irq_ack register should be used to clear in...

Page 18

I/o module v1.02a www.Xilinx.Com 18 pg052 october 16, 2012 product specification register space interrupt pending register (irq_pending) the interrupt pending register holds information on enabled interrupt events that have occurred. Irq_pending is the contents of irq_status bit-wised masked with th...

Page 19

I/o module v1.02a www.Xilinx.Com 19 pg052 october 16, 2012 product specification register space interrupt enable register (irq_enable) the interrupt enable register enables assertion of the i/o module interrupt output signal intc_irq by individual interrupt sources. The contents of this register are...

Page 20

I/o module v1.02a www.Xilinx.Com 20 pg052 october 16, 2012 product specification register space interrupt acknowledge register (irq_ack) this register is used as a command register for clearing individual interrupts in irq_status and irq_pending registers. All bits set to 1 clear the corresponding b...

Page 21: Irq_Vector_31)

I/o module v1.02a www.Xilinx.Com 21 pg052 october 16, 2012 product specification register space interrupt address vector registers (irq_vector_0 - irq_vector_31) these 32 registers are used as interrupt address vector for the corresponding interrupt bit. The content is sent to the processor on the i...

Page 22

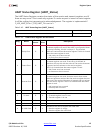

I/o module v1.02a www.Xilinx.Com 22 pg052 october 16, 2012 product specification register space pitx counter register (pitx_counter) (x = 1, 2, 3 or 4) when reading this register the data obtained is a sample of the current counter value. The register is implemented if c_use_pitx is 1 and c_pitx_rea...

Page 23: General Design Guidelines

I/o module v1.02a www.Xilinx.Com 23 pg052 october 16, 2012 chapter 3 designing with the core this chapter includes guidelines and additional information to facilitate designing with the core. General design guidelines i/o bus the i/o bus provides a simple bus for accessing to external modules using ...

Page 24

I/o module v1.02a www.Xilinx.Com 24 pg052 october 16, 2012 general design guidelines . The byte enable signals indicate which byte lanes of the data bus contain valid data. Valid values for io_byte_enable are shown in table 3-1 . The io_byte_enable signal should be used instead of the two least sign...

Page 25: Uart

I/o module v1.02a www.Xilinx.Com 25 pg052 october 16, 2012 general design guidelines the i/o bus is fully compatible with the xilinx dynamic reconfiguration port (drp). This configuration port supports partial dynamic reconfiguration of functional blocks, such as cmts, clock management, xadc, serial...

Page 26: Fixed Interval Timer, Fit

I/o module v1.02a www.Xilinx.Com 26 pg052 october 16, 2012 general design guidelines the uart can be configured with either fixed or programmable baud rate. When using programmable baud rate the uart_baud register is used to set the baud rate. The initial value of this register is determined from th...

Page 27: General Purpose Output, Gpo

I/o module v1.02a www.Xilinx.Com 27 pg052 october 16, 2012 general design guidelines general purpose output, gpo the general purpose output, gpo, drives i/o module gpo output signals defined by the value of the gpox register, programmable from software. The width of the gpox is defined by the c_gpox...

Page 28: Lmb Timing

I/o module v1.02a www.Xilinx.Com 28 pg052 october 16, 2012 lmb timing an interrupt is cleared in both the interrupt status and interrupt pending registers by writing to the interrupt acknowledge register, with bits set corresponding to the interrupts that should be cleared. Either normal or fast int...

Page 29: Protocol Description

I/o module v1.02a www.Xilinx.Com 29 pg052 october 16, 2012 protocol description protocol description see lmb interface description timing diagrams in the microblaze processor reference guide [ref 1] ..

Page 30

I/o module v1.02a www.Xilinx.Com 30 pg052 october 16, 2012 section ii: vivado design suite customizing and generating the core constraining the core.

Page 31: Gui

I/o module v1.02a www.Xilinx.Com 31 pg052 october 16, 2012 chapter 4 customizing and generating the core this chapter includes information on using xilinx tools to customize and generate the core in the vivado™ design suite. Gui the i/o module parameters are divided in seven tabs: system, uart, fit ...

Page 32

I/o module v1.02a www.Xilinx.Com 32 pg052 october 16, 2012 gui • i/o module register address decode mask - a mask indicating which address bits the module takes into account when decoding a register access. • enable io bus - enables the i/o bus to connect to drp or external peripherals. • i/o module...

Page 33

I/o module v1.02a www.Xilinx.Com 33 pg052 october 16, 2012 gui • number of data bits - defines the number of data bits used by the uart. Should almost always be set to 8. • use parity - enable this parameter to use parity checking of the uart characters. • even or odd parity - select odd or even par...

Page 34

I/o module v1.02a www.Xilinx.Com 34 pg052 october 16, 2012 gui the pit timer parameter tab showing the parameters for one of the four timers is shown in figure 4-4 . • use pit - enable the programmable interval timer. • number of bits for timer - the maximum number of cycles to count before stopping...

Page 35

I/o module v1.02a www.Xilinx.Com 35 pg052 october 16, 2012 gui • use gpo - enable the general purpose output port. • number of bits - set the number of bits of the general purpose output port. • initial value of gpo - set the initial value of the general purpose output port. The right most bit in th...

Page 36

I/o module v1.02a www.Xilinx.Com 36 pg052 october 16, 2012 gui • use gpi - enable the general purpose input port. • number of bits - set the number of bits of the general purpose input port. • generate interrupt - generate an interrupt when a general purpose input changes. The interrupt parameter ta...

Page 37: Parameter Values

I/o module v1.02a www.Xilinx.Com 37 pg052 october 16, 2012 parameter values • use external interrupts - enable the use of external interrupt inputs. • number of external inputs - select the number of used external interrupt inputs. • level or edge of external interrupts - select whether the input is...

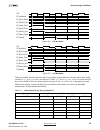

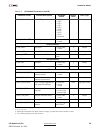

Page 38

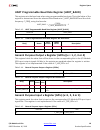

I/o module v1.02a www.Xilinx.Com 38 pg052 october 16, 2012 parameter values table 4-1: i/o module parameters parameter name feature/description allowable values default value vhdl type c_family (1) fpga architecture supported architectures “virtex5” string i/o bus parameter c_use_io_bus use i/o bus ...

Page 39

I/o module v1.02a www.Xilinx.Com 39 pg052 october 16, 2012 parameter values c_pitx_prescaler (2)(3) select pitx prescaler 0 = no prescaler 1 = fit1 2 = fit2 3 = fit3 4 = fit4 5 = pit1 6 = pit2 7 = pit3 8 = pit4 9 = external 0 integer c_pitx_interrupt (2) use pitx_interrupt in intc 0 = not used 1 = u...

Page 40: Required Constraints

I/o module v1.02a www.Xilinx.Com 40 pg052 october 16, 2012 chapter 5 constraining the core required constraints there are no required constraints for this core. Device, package, and speed grade selections there are no device, package or speed grade requirements for this core. Clock frequencies there...

Page 41: Banking

I/o module v1.02a www.Xilinx.Com 41 pg052 october 16, 2012 banking banking there are no specific banking rules for this core. Transceiver placement there are no transceiver placement requirements for this core. I/o standard and placement there are no specific i/o standards and placement requirements...

Page 42

I/o module v1.02a www.Xilinx.Com 42 pg052 october 16, 2012 section iii: ise design suite customizing and generating the core constraining the core.

Page 43: Gui

I/o module v1.02a www.Xilinx.Com 43 pg052 october 16, 2012 chapter 6 customizing and generating the core this chapter includes information on using xilinx tools to customize and generate the core in the ise® design suite. Gui the i/o module parameters are divided in seven tabs: system, uart, fit tim...

Page 44

I/o module v1.02a www.Xilinx.Com 44 pg052 october 16, 2012 gui • i/o module register address decode mask - a mask indicating which address bits the module takes into account when decoding a register access. • enable io bus - enables the i/o bus to connect to drp or external peripherals. • i/o module...

Page 45

I/o module v1.02a www.Xilinx.Com 45 pg052 october 16, 2012 gui • programmable baud rate - determines if the uart baud rate is programmable. The default baud rate is calculated based on the input clock frequency and the defined baud rate. • number of data bits - defines the number of data bits used b...

Page 46

I/o module v1.02a www.Xilinx.Com 46 pg052 october 16, 2012 gui • number of clocks between strobes - the number of clock cycles between each strobe. • generate interrupt - generate an interrupt for each fixed interval timer strobe. The pit timer parameter tab showing the parameters for one of the fou...

Page 47

I/o module v1.02a www.Xilinx.Com 47 pg052 october 16, 2012 gui • use gpo - enable the general purpose output port. • number of bits - set the number of bits of the general purpose output port. • initial value of gpo - set the initial value of the general purpose output port. The right most bit in th...

Page 48

I/o module v1.02a www.Xilinx.Com 48 pg052 october 16, 2012 gui • use gpi - enable the general purpose input port. • number of bits - set the number of bits of the general purpose input port. • generate interrupt - generate an interrupt when a general purpose input changes. X-ref target - figure 6-6 ...

Page 49: Parameter Values

I/o module v1.02a www.Xilinx.Com 49 pg052 october 16, 2012 parameter values the interrupt parameter tab is shown in figure 6-7 . • use external interrupts - shows if external interrupt inputs are used. • number of external inputs - shows the number of used external interrupt inputs. • use low-latenc...

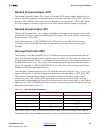

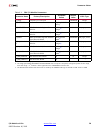

Page 50

I/o module v1.02a www.Xilinx.Com 50 pg052 october 16, 2012 parameter values table 6-1: edk i/o module parameters parameter name feature/description allowable values default value vhdl type c_freq (1) frequency of clk input 100000000 integer c_instance (1) instance name any legal vhdl string “iomodul...

Page 51: Clock Management

I/o module v1.02a www.Xilinx.Com 51 pg052 october 16, 2012 chapter 7 constraining the core clock management the i/o module is fully synchronous with all clocked elements clocked by the clk input. To operate properly when connected to microblaze™, the clk must be the same as the microblaze clk ..

Page 52

I/o module v1.02a www.Xilinx.Com 52 pg052 october 16, 2012 section iv: appendices migrating debugging application software development additional resources.

Page 53

I/o module v1.02a www.Xilinx.Com 53 pg052 october 16, 2012 appendix a migrating this appendix describes migrating from older versions of the ip to the current ip release. For information on migrating to the vivado™ design suite, see the vivado design suite migration methodology guide [ref 3] ..

Page 54: Solution Centers

Shortened title with core version www.Xilinx.Com 54 pg000 august 10, 2012 appendix b debugging solution centers see the xilinx solution centers for support on devices, software tools, and intellectual property at all stages of the design cycle. Topics include design assistance, advisories, and troub...

Page 55: Device Drivers

I/o module v1.02a www.Xilinx.Com 55 pg052 october 16, 2012 appendix c application software development device drivers the i/o module is supported by the io module driver, included with xilinx software development kit..

Page 56: Xilinx Resources

I/o module v1.02a www.Xilinx.Com 56 pg052 october 16, 2012 appendix d additional resources xilinx resources for support resources such as answers, documentation, downloads, and forums, see the xilinx support website at: www.Xilinx.Com/support . For a glossary of technical terms used in xilinx docume...

Page 57: Revision History

I/o module v1.02a www.Xilinx.Com 57 pg052 october 16, 2012 revision history revision history the following table shows the revision history for this document. Notice of disclaimer the information disclosed to you hereunder (the “materials”) is provided solely for the selection and use of xilinx prod...