- DL manuals

- Xilinx

- Media Converter

- LogiCORE IP

- User Manual

Xilinx LogiCORE IP User Manual

Summary of LogiCORE IP

Page 1

Logicore™ ip video scaler v4.0 user guide ug805 march 1, 2011.

Page 2: Revision History

Video scaler v4.0 user guide www.Xilinx.Com ug805 march 1, 2011 xilinx is providing this product documentation, hereinafter “information,” to you “as is” with no warranty of any kind, express or implied. Xilinx makes no representation that the information, or any particular implementation thereof, i...

Page 3: Table of Contents

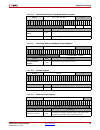

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide table of contents revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 schedule of figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 4

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide chapter 5: scaler architectures architecture descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 single-engine for sequential yc processing . . . . . . . . . . . . . . . ...

Page 5

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide appendix b: programmer guide introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 conventions . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 6

Video scaler v4.0 user guide www.Xilinx.Com ug805 march 1, 2011.

Page 7: Schedule of Figures

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide schedule of figures chapter 1: introduction chapter 2: overview chapter 3: implementation figure 3-1: high level view of the functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 figure 3-2: simplified top l...

Page 8

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide chapter 9: performance appendix a: use cases figure a-1: format down-scaling. Example 720p to 640x480, hsf = 2 20 x 1280/640; vsf = 2 20 x 720/480 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 figure a-2...

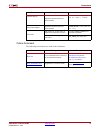

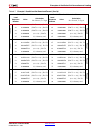

Page 9: Schedule of Tables

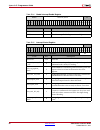

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide schedule of tables chapter 1: introduction table 1-1: nomenclature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 chapter 2: overview chapter 3: implementation chapter 4:...

Page 10

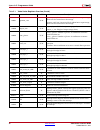

Ug805 march 1, 2011 www.Xilinx.Com video scaler v4.0 user guide appendix a: use cases appendix b: programmer guide table b-1: video scaler registers overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 table b-2: control register . . . . . . . . . . . . . . . . . ....

Page 11: About This Guide

Video scaler v4.0 user guide www.Xilinx.Com 11 ug805 march 1, 2011 preface about this guide the logicore™ ip video scaler v4.0 user guide provides information about generating the video scaler core, customizing and simulating the core using the provided example design, and running the design files t...

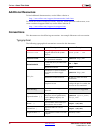

Page 12: Additional Resources

12 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 preface: about this guide additional resources to find additional documentation, see the xilinx website at: http://www.Xilinx.Com/support/documentation/index.Htm . To search the answer database of silicon, software, and ip questions ...

Page 13

Video scaler v4.0 user guide www.Xilinx.Com 13 ug805 march 1, 2011 conventions online document the following conventions are used in this document: vertical ellipsis . . . Repetitive material that has been omitted iob #1: name = qout’ iob #2: name = clkin’ . . . Horizontal ellipsis . . . Repetitive ...

Page 14

14 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 preface: about this guide.

Page 15: Introduction

Video scaler v4.0 user guide www.Xilinx.Com 15 ug805 march 1, 2011 chapter 1 introduction this chapter introduces the video scaler core and provides related information, including recommended design experience, additional resources, technical support, and submitting feedback to xilinx. See www.Xilin...

Page 16: Providing Feedback

16 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 1: introduction providing feedback xilinx welcomes comments and suggestions about the video scaler core and the documentation supplied with the core. Core for comments or suggestions about the video scaler core, submit a webc...

Page 17

Video scaler v4.0 user guide www.Xilinx.Com 17 ug805 march 1, 2011 nomenclature coefficient bank a group of coefficients that will be applied to one video component (y or c) in one dimension (h or v) for a conversion of one frame. It includes all phases. For an n-tap, m-phase filter, a coefficient b...

Page 18

18 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 1: introduction.

Page 19: Overview

Video scaler v4.0 user guide www.Xilinx.Com 19 ug805 march 1, 2011 chapter 2 overview video scaling is the process of converting an input color image of dimensions x in pixels by y in lines to an output color image of dimensions x out pixels by y out lines. Within predefined limits, the xilinx video...

Page 20

20 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 2: overview.

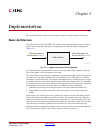

Page 21: Implementation

Video scaler v4.0 user guide www.Xilinx.Com 21 ug805 march 1, 2011 chapter 3 implementation this section elaborates on the internal structure in the core, and describes interfacing. Basic architecture the xilinx video scaler logicore™ ip converts a specified rectangular area of an input digital vide...

Page 22: I/o Buffering, Clock Domains

22 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 3: implementation some observations (not exclusively true for all conversions): • generally, when up-scaling, or dealing with high definition (hd) rates, it is simplest to use an input-side frame buffer. This does depend upon...

Page 23: Data Source: Live Video

Video scaler v4.0 user guide www.Xilinx.Com 23 ug805 march 1, 2011 chapter 4 video i/o interface and timing core generator™ software provides two interface options for provision of the video data into the video scaler core. 1. Live – standard format video signal, along with synchronization signals t...

Page 24

24 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 4: video i/o interface and timing valid video data is written into the input line buffer using active_video_in as a write- enable. This is shown in figure 4-1 for the 8-bit 4:2:2 case the active_video_in signal must remain in...

Page 25

Video scaler v4.0 user guide www.Xilinx.Com 25 ug805 march 1, 2011 data source: live video hblank_in input the horizontal blanking input signal hblank_in is generally used as a line-based reset. It must be provided to the scaler core in the same clock domain as the video data ( video_in_clk ). The h...

Page 26

26 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 4: video i/o interface and timing specified in the core generator/edk gui. Figure 4-3 is a screen shot from simulation, showing the relationship between vblank_in , hblank_in and frame_rst . The line count shown is an interna...

Page 27: Data Source: Memory

Video scaler v4.0 user guide www.Xilinx.Com 27 ug805 march 1, 2011 data source: memory data source: memory this mode is primarily intended for use with a memory controller with rectangular access capability such as the vfbc port on the mpmc. The vfbc port must be configured to provide the amount of ...

Page 28

28 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 4: video i/o interface and timing output data and timing signals although driving the scaler input using a direct standard video feed is supported, the equivalent cannot be said for the scaler output. Because of the bursty na...

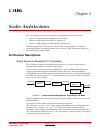

Page 29: Scaler Architectures

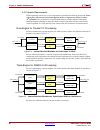

Video scaler v4.0 user guide www.Xilinx.Com 29 ug805 march 1, 2011 chapter 5 scaler architectures the scaler supports the following possible arrangements of the internal filters. • option 1: single-engine for sequential yc processing • option 2: dual engine for parallel yc processing • option 3: tri...

Page 30

30 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 5: scaler architectures 4:2:0 special requirements when operating with 4:2:0, it is also important to include the following restriction: when scaling 4:2:0, the vertical scale factor applied at the vsf input must not be less ...

Page 31: Gui Operation

Video scaler v4.0 user guide www.Xilinx.Com 31 ug805 march 1, 2011 gui operation gui operation when the chroma format is specified as 4:4:4, the triple-engine parallel architecture is always selected. Otherwise, selection between the yc sequential or parallel options may be achieved automatically (y...

Page 32

32 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 5: scaler architectures the information tab (see figure 5-5 ) in the core generator gui (not available in edk gui) shows the estimated maximum achievable frame-rate given the above information, using a similar calculation as ...

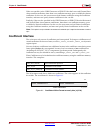

Page 33: Control Interface

Video scaler v4.0 user guide www.Xilinx.Com 33 ug805 march 1, 2011 chapter 6 control interface there are three control interface options available in core generator™ software: edk pcore, gpp or constant. The interface types differ primarily in the method of delivery of the user-defined control value...

Page 34

34 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 6: control interface hence, up-scaling is achieved using a shrink-factor value less than one. Down-scaling is achieved with a shrink-factor greater than one. You may wish to work this calculation backwards. For a desired scal...

Page 35: Constant (Fixed) Mode

Video scaler v4.0 user guide www.Xilinx.Com 35 ug805 march 1, 2011 constant (fixed) mode constant (fixed) mode when using this mode, the values are fixed at compile time. The user system does not need to drive any of the parameters. The core generator gui prompts you to specify: • coefficient file (...

Page 36: Edk Pcore Interface

36 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 6: control interface edk pcore interface in contrast to gpp mode and constant mode control interfaces, when you select this control interface option in core generator, no netlist is created. Instead, a database is generated c...

Page 37: Interrupts

Video scaler v4.0 user guide www.Xilinx.Com 37 ug805 march 1, 2011 interrupts 2. Copy the /pcores/axi_scaler_v4_00_a sub-directory from the core generator database to the /pcores directory in your edk project repository. All vhdl files are encrypted. Do not attempt to modify these files . Parameter ...

Page 38

38 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 6: control interface inside the pcore wrapper, an interrupt controller (xilinx interrupt control logicore™ ( ds516 )) collates these interrupts into one interrupt on the axi4-lite bus. The microprocessor must then read the in...

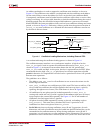

Page 39: Scaler Aperture

Video scaler v4.0 user guide www.Xilinx.Com 39 ug805 march 1, 2011 chapter 7 scaler aperture this section explains how to define the scaler aperture using the appropriate dynamic control registers. The aperture is defined relative to the input timing signals. Input aperture definition it is vital to...

Page 40: Cropping

40 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 7: scaler aperture pixel 0 is defined as the first active pixel after the rising edge of active_video_in . This is indicated in figure 7-2 . The value 128 is used as the default value in video_data_in during blanking. In this...

Page 41: Coefficients

Video scaler v4.0 user guide www.Xilinx.Com 41 ug805 march 1, 2011 chapter 8 coefficients this section describes the coefficients used by both the vertical and horizontal filter portions of the scaler, in terms of number, range, formatting and download procedures. Coefficient table one single size-c...

Page 42: Coefficient Interface

42 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients if the user specifies in the core generator or edk gui that the luma and chroma filters share common coefficients, then there is no coefficient memory space available for chroma coefficients. In this case, the...

Page 43

Video scaler v4.0 user guide www.Xilinx.Com 43 ug805 march 1, 2011 coefficient interface an address-multiplexer is used to support the coefficient write interface as shown in figure 8-2 . The coefficient write-address is multiplexed with the coefficient read-address for the vertical filter to create...

Page 44

44 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients case, for a 12h-tap x 12v-tap 64-phase filter, you need to write 6 times per phase. If the user has specified separate h and v coefficients, this is a total of 768 write operations per set. • for yc4:2:2 or yc...

Page 45

Video scaler v4.0 user guide www.Xilinx.Com 45 ug805 march 1, 2011 examples of coefficient set generation and loading beyond the scope of this document. Refer to answer record 35262 and filter coefficient calculations for more information on coefficient generation for the video scaler. % subsample a...

Page 46

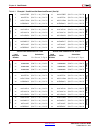

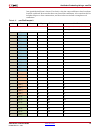

46 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients phase 1 5 0x058cfbef (ph1 t1 21 0x058cfbef (ph1 t1 phase 1 6 0x1457f749 (ph1 t3 22 0x1457f749 (ph1 t3 7 0xf3cc3d04 (ph1 t5 23 0xf3cc3d04 (ph1 t5 8 0xfb4e06c8 (ph1 t7 24 0xfb4e06c8 (ph1 t7 phase 2 9 0x08d8f9af ...

Page 47

Video scaler v4.0 user guide www.Xilinx.Com 47 ug805 march 1, 2011 examples of coefficient set generation and loading example 2: num_h_taps = num_v_taps = 8; max_phases = 5, 6, 7 or 8 ; num_h_phases = num_v_phases = 4 if the max_phases parameter is greater than the number of phases in the set being ...

Page 48

48 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients phase 5 21 0x00000000 n/a dummy coef 53 0x00000000 n/a dummy coef phase 5 22 0x00000000 n/a dummy coef 54 0x00000000 n/a dummy coef 23 0x00000000 n/a dummy coef 55 0x00000000 n/a dummy coef 24 0x00000000 n/a d...

Page 49

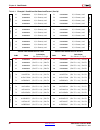

Video scaler v4.0 user guide www.Xilinx.Com 49 ug805 march 1, 2011 examples of coefficient set generation and loading example 3: num_h_taps = 9; num_v_taps = 7 ; max_phases = num_h_phases = num_v_phases = 4 now consider the case where the number of taps in the horizontal dimension is different to th...

Page 50

50 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients the resulting coefficient file for download is shown in table 8-7 . Table 8-6: example 7-tap coefficients phase tap 0 tap 1 tap 2 tap 3 tap 4 tap 5 tap 6 0 0x0000 0x0000 0x0000 0x4000 0x0000 0x0000 0x0000 1 0x...

Page 51

Video scaler v4.0 user guide www.Xilinx.Com 51 ug805 march 1, 2011 examples of coefficient set generation and loading vertical filter coefficients for luma vertical filter coefficients for chroma load sequence number value calculation ph= phase #, t= tap # load sequence number value calculation ph= ...

Page 52

52 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients coefficient preloading using a .Coe file to preload the scaler with coefficients (mandatory when in constant mode), you must specify, using the core generator gui or the edk gui, a .Coe file that contains the ...

Page 53

Video scaler v4.0 user guide www.Xilinx.Com 53 ug805 march 1, 2011 coefficient preloading using a .Coe file within each “bin,” four further levels of granularity can be observed. In order of decreasing size of granularity, these levels are: • number of taps defined • number of phases defined • phase...

Page 54

54 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients • user setting for "separate h/v coefficients" the simplest method is to specify an intermediate value num_banks : num_banks=4; if (separate h/v coefficients = 0) then num_banks := num_banks/2; end; if (separa...

Page 55

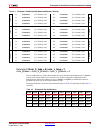

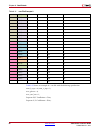

Video scaler v4.0 user guide www.Xilinx.Com 55 ug805 march 1, 2011 coefficient preloading using a .Coe file both signed decimal and 16-bit binary forms are shown. Table 8-10: .Coe file example 1 phase tap file line-number line text (signed decimal form) line text (16-bit binary form) n/a n/a 1 memor...

Page 56

56 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients table 8-11 shows an example of a .Coe file with the following specification: num_h_taps = 12, num_v_taps = 12; max_phases = 4; max_coef_sets = 2; separate h/v coefficients = true; separate y/c coefficients = t...

Page 57

Video scaler v4.0 user guide www.Xilinx.Com 57 ug805 march 1, 2011 coefficient preloading using a .Coe file just signed decimal form is shown. For clarity's sake, the same coefficient values have been used for each bank. Be aware that these are not realistic coefficients. Also note that this list in...

Page 58

58 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients table 8-12 shows an example of a .Coe file with the following specification: num_h_taps = 4, num_v_taps = 3; max_phases = 4; max_coef_sets = 1; separate h/v coefficients = true; separate y/c coefficients = fal...

Page 59

Video scaler v4.0 user guide www.Xilinx.Com 59 ug805 march 1, 2011 coefficient preloading using a .Coe file just signed decimal form is shown. Table 8-12: .Coe file example 3 bank phase tap file line- number line text notes n/a 1 memory_initialization_radix=10; 2 memory_initialization_vector= 0 (h) ...

Page 60: Coefficient Readback

60 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 8: coefficients coefficient readback for coefficient verification purposes, a feature of the video scaler allows the user to read back coefficients in the active coefficient memory. Dedicated connections are included to facil...

Page 61: Performance

Video scaler v4.0 user guide www.Xilinx.Com 61 ug805 march 1, 2011 chapter 9 performance the target maximum clock frequencies for all scaler input clocks are shown in table 9-1 . It is very important to ensure that the clock rate available supports worst-case conversions. This chapter includes detai...

Page 62: Live Video Mode

62 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 9: performance how do you establish whether or not the scaler will meet the application requirements? The approach taken is to calculate the minimum clock frequency required to make the intended conversions possible . Definit...

Page 63

Video scaler v4.0 user guide www.Xilinx.Com 63 ug805 march 1, 2011 live video mode • cyclesperoutputline – this is the number of cycles the scaler requires to generate one output line, of multiple components. The final calculation depends upon the chroma format and the filter configuration (yc4:2:2 ...

Page 64

64 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 9: performance we modify this to include the chroma components. Yc case is shown in this example. Cyclesrequiredperoutputline=2*max(output_h_size,subjwidth)+3*processingover headpercomponent • maxvholdsperinputaperture – this...

Page 65

Video scaler v4.0 user guide www.Xilinx.Com 65 ug805 march 1, 2011 live video mode example 2: up-scaling 640x480 60 hz yc4:2:2 to 800x600 assuming 30 khz line rate vertical scale ratio = 1.25 horizontal scale ratio = 1.25 flinein = 30000 single-engine implementation cyclesrequiredperoutputline = 2*8...

Page 66

66 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 9: performance example 5: down-scaling 800x600 60hz yc4:2:2 to 640x480 assuming 30 khz line rate vertical scale ratio = 0.8 horizontal scale ratio = 0.8 flinein = 30000 single-engine implementation cyclesrequiredperoutputline...

Page 67: Memory Mode

Video scaler v4.0 user guide www.Xilinx.Com 67 ug805 march 1, 2011 memory mode example 8: down-scaling 720p/60 yc4:2:2 to 640x480 45 khz line rate vertical scale ratio = 0.6667 horizontal scale ratio = 0.5 flinein = 45000 single-engine implementation cyclesrequiredperoutputline = 2*1280 + 150 (appro...

Page 68

68 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 9: performance • cyclesperoutputframe – this is the number of cycles the scaler requires to generate one output frame, of multiple components. The final calculation depends upon the chroma format (and, for yc4:2:2 only, the f...

Page 69

Video scaler v4.0 user guide www.Xilinx.Com 69 ug805 march 1, 2011 memory mode example 10: converting 720p yc4:2:2 to 1080i/60 (1920x540) vertical scale ratio = 0.75 horizontal scale ratio = 1.5 fframein = 60 cyclesperoutputframe = (1920*2 + 150)*540 + 10000 (approximately) = 2164600 minf'clk' = 60 ...

Page 70

70 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 chapter 9: performance.

Page 71: Use Cases

Video scaler v4.0 user guide www.Xilinx.Com 71 ug805 march 1, 2011 appendix a use cases typical uses some scenarios for scaler usage are shown in figure a-1 through figure a-5 . In particular, usage of the following dynamic parameter values are illustrated: • aperture_start_line • aperture_end_line ...

Page 72

72 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix a: use cases x-ref target - figure a-2 figure a-2: format up-scaling. Example 640x480 to 720p, hsf = 2 20 x 640/1280; 2 20 x vsf = 480/720 x-ref target - figure a-3 figure a-3: zoom (up-scaling), hsf = 2 20 x 480/1280; vsf =...

Page 73

Video scaler v4.0 user guide www.Xilinx.Com 73 ug805 march 1, 2011 typical uses x-ref target - figure a-5 figure a-5: zoom (up-scaling) reading from external memory, hsf = 2 20 x 480/1280; vsf = 2 20 x 270/720 a pert u re_ s t a rt_line = 0 a pert u re_ s t a rt_pixel = 0 12 8 0 4 8 0 270 720 a pert...

Page 74

74 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix a: use cases.

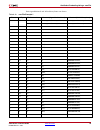

Page 75: Programmer Guide

Video scaler v4.0 user guide www.Xilinx.Com 75 ug805 march 1, 2011 appendix b programmer guide introduction this appendix provides a description of how to program and control the data flow for the video scaler hardware pcore. The information is sufficient for the development of a software driver (ap...

Page 76

76 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide 0x001c aperture_vert r/w aperture_start_line: location of first subject line in input image, relative to first active line in that image aperture_end_line: location of final subject line in input image, r...

Page 77

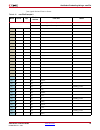

Video scaler v4.0 user guide www.Xilinx.Com 77 ug805 march 1, 2011 register definitions table b-2: control register 0x0000 control r/w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 0 9 0 8 0 7 0 6 0 5 0 4 0 3 0 2 0 1 0 0 reserved enable name bits description...

Page 78

78 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide error_code2 23:16 error codes to be defined error_code1 15:8 error codes to be defined error_code0 7:0 error codes to be defined table b-5: status_done register 0x000c status_done r/w 3 1 3 0 2 9 2 8 2 7 ...

Page 79

Video scaler v4.0 user guide www.Xilinx.Com 79 ug805 march 1, 2011 register definitions reserved 31:24 reserved vsf_int 23:20 vertical shrink factor integer vsf_frac 19:0 vertical shrink factor fractional table b-8: aperture_horz register 0x0018 aperture_horz r/w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 ...

Page 80

80 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide reserved 15:11 reserved output_h_size 12:0 number of pixels in output image table b-11: num_phases register 0x0024 num_phases r/w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 ...

Page 81

Video scaler v4.0 user guide www.Xilinx.Com 81 ug805 march 1, 2011 register definitions table b-14: start_vpa_y register 0x0030 start_hpa_c r/w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 0 9 0 8 0 7 0 6 0 5 0 4 0 3 0 2 0 1 0 0 reserved start_hpa_c name bi...

Page 82

82 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide name bits description reserved 31:4 reserved coef_write_set_addr 3:0 coefficient bank to write, address table b-18: coef_values register 0x0040 coef_values w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 ...

Page 83

Video scaler v4.0 user guide www.Xilinx.Com 83 ug805 march 1, 2011 register definitions table b-20: coefficient phase and tap read address register 0x0048 coef_mem_rd_addr r/w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 8 7 6 5 4 3 2 1 0 reserved phase r...

Page 84

84 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide table b-24: global interrupt enable register 0x021c software_reset w 3 1 3 0 2 9 2 8 2 7 2 6 2 5 2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7 1 6 1 5 1 4 1 3 1 2 1 1 1 0 0 9 0 8 0 7 0 6 0 5 0 4 0 3 0 2 0 1 0 0 reserve...

Page 85

Video scaler v4.0 user guide www.Xilinx.Com 85 ug805 march 1, 2011 register definitions filter coefficient calculations the values for the filter coefficients can be calculated with any standard digital filter tool. Matlab® software provides a tool box for establishing the filter coefficients once t...

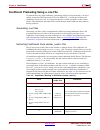

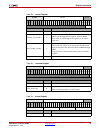

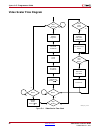

Page 86: Video Scaler Flow Diagram

86 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide video scaler flow diagram figure b-0: video scaler flow chart initi a lize regi s ter s s et lo a d coef b a nk lo a d coef s s et active coef b a nk en ab le video s c a ler control 0 1 3 di sab le s c a...

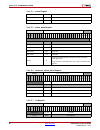

Page 87: System Timing Diagram

Video scaler v4.0 user guide www.Xilinx.Com 87 ug805 march 1, 2011 system timing diagram system timing diagram figure b-0: system timing diagram.

Page 88: Proposed Api Function Calls

88 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide proposed api function calls the following functions are proposed for lo, l1, l2 api. L0 api function calls #define xscaler_enable(instanceptr) #define xscaler_disable(instanceptr) #define xscaler_reset(in...

Page 89

Video scaler v4.0 user guide www.Xilinx.Com 89 ug805 march 1, 2011 proposed api function calls l1 api function calls #define xscaler_calccoeffs(coeffs, scale, taps, phases, coeff_precision) • software function, no registers written #define xscaler_writecoeffvalues(instanceptr, coeffs, coeff_bank) • ...

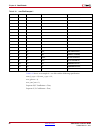

Page 90: Example Settings

90 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide • in a downsize operation, the input image size is not changing on a frame basis and the output resolution is changing. • calls xscaler_calcscalefactors , xscaler_setscalervalues every frame to perform th...

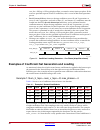

Page 91

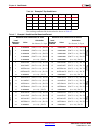

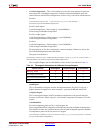

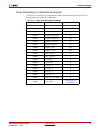

Video scaler v4.0 user guide www.Xilinx.Com 91 ug805 march 1, 2011 example settings down sample by 2 in horizontal and vertical table b-28 is an example of scaling down a 1280 x 720 resolution image by a factor of 2 horizontally and vertically to 640x 360. Table b-28: down sample register settings a...

Page 92

92 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix b: programmer guide.

Page 93: System Level Design

Video scaler v4.0 user guide www.Xilinx.Com 93 ug805 march 1, 2011 appendix c system level design introduction this appendix provides an example system that includes the video scaler core. Important system level aspects when designing with the video scaler are highlighted, including: • video scaler ...

Page 94: Control Buses

94 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix c: system level design • the on-screen display (osd) block aligns the data read from memory with the timing signals and presents it as a standard-format video data stream. It also alpha- blends multiple layers of information...

Page 95: Vdma1 Configuration

Video scaler v4.0 user guide www.Xilinx.Com 95 ug805 march 1, 2011 vdma1 configuration vdma1 configuration vdma1 is bidirectional, used for reading the original frames from memory, and writing the scaled frame back to memory. The system operates using a genlock mechanism. A second rotational 5-frame...

Page 96: Cropping From Memory

96 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix c: system level design scaler write-port • for the port that feeds from the video scaler out to the memory, ensure that there is a fifo of a size equal to or greater than the maximum line length anticipated to be output by t...

Page 97

Video scaler v4.0 user guide www.Xilinx.Com 97 ug805 march 1, 2011 edk mhs file text port m_wd_frame_ptr_out = vdma_0_xil_wd_mgenlock port vdma_wcmd_clk = vid_in_clk port vdma_wd_clk = vid_in_clk port vdma_rcmd_clk = vid_in_clk port vdma_rd_clk = vid_in_clk end begin timebase parameter instance = ti...

Page 98

98 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix c: system level design parameter hw_ver = 1.01.A parameter c_mpmc_baseaddr = 0x10000000 parameter c_mpmc_highaddr = 0x1fffffff parameter c_use_fsync = 1 parameter c_dma_type = 1 parameter c_gen_reset = 1 parameter c_data_wid...

Page 99

Video scaler v4.0 user guide www.Xilinx.Com 99 ug805 march 1, 2011 edk mhs file text bus_interface debug = microblaze_0_mdm_bus bus_interface dlmb = dlmb bus_interface ilmb = ilmb port mb_reset = mb_reset port interrupt = xps_intc_0_irq end begin plb_v46 parameter instance = mb_plb parameter hw_ver ...

Page 100

100 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix c: system level design parameter hw_ver = 6.03.A parameter c_num_ports = 6 parameter c_mmcm_ext_loc = mmcm_adv_x0y9 parameter c_mem_type = ddr3 parameter c_mem_partno = mt4jsf6464hy-1g1 parameter c_mem_odt_type = 1 paramete...

Page 101

Video scaler v4.0 user guide www.Xilinx.Com 101 ug805 march 1, 2011 edk mhs file text port ddr3_bankaddr = fpga_0_ddr3_sdram_ddr3_bankaddr_pin port ddr3_addr = fpga_0_ddr3_sdram_ddr3_addr_pin port ddr3_dq = fpga_0_ddr3_sdram_ddr3_dq_pin port ddr3_dm = fpga_0_ddr3_sdram_ddr3_dm_pin port ddr3_reset_n ...

Page 102

102 www.Xilinx.Com video scaler v4.0 user guide ug805 march 1, 2011 appendix c: system level design bus_interface splb = mb_plb port intr = vdma_0_ip2intc_irpt & vdma_1_ip2intc_irpt & osd_0_ip2intc_irpt & scaler_0_ip2intc_irpt & vdma_2_ip2intc_irpt & timebase_1_ip2intc_irpt & rs232_uart_1_interrupt ...