- DL manuals

- Xilinx

- Computer Hardware

- MicroBlaze

- Reference Manual

Xilinx MicroBlaze Reference Manual - Lhui

208

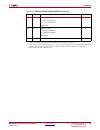

MicroBlaze Processor Reference Guide

UG081 (v14.7)

Chapter 5:

MicroBlaze Instruction Set Architecture

lhui

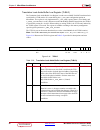

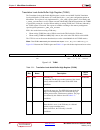

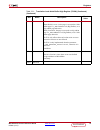

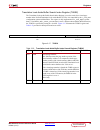

Load Halfword Unsigned Immediate

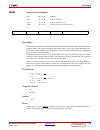

Description

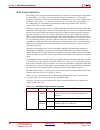

Loads a halfword (16 bits) from the halfword aligned memory location that results from adding the

contents of register rA and the value in IMM, sign-extended to 32 bits. The data is placed in the least

significant halfword of register rD and the most significant halfword in rD is cleared.

A data TLB miss exception occurs if virtual protected mode is enabled, and a valid translation entry

corresponding to the address is not found in the TLB. A data storage exception occurs if access is

prevented by a no-access-allowed zone protection. This only applies to accesses with user mode and

virtual protected mode enabled. An unaligned data access exception occurs if the least significant bit

in the address is not zero.

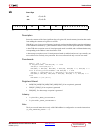

Pseudocode

Addr

←

(rA) + sext(IMM)

if TLB_Miss(Addr) and MSR[VM] = 1 then

ESR[EC]

←

10010;ESR[S]

←

0

MSR[UMS]

←

MSR[UM]; MSR[VMS]

←

MSR[VM]; MSR[UM]

←

0; MSR[VM]

←

0

else if Access_Protected(Addr) and MSR[UM] = 1 and MSR[VM] = 1 then

ESR[EC]

←

10000;ESR[S]

←

0; ESR[DIZ]

←

1

MSR[UMS]

←

MSR[UM]; MSR[VMS]

←

MSR[VM]; MSR[UM]

←

0; MSR[VM]

←

0

else if Addr[31]

≠

0 then

ESR[EC]

←

00001; ESR[W]

←

0; ESR[S]

←

0; ESR[Rx]

←

rD

else

(rD)[16:31]

←

Mem(Addr)

(rD)[0:15]

←

0

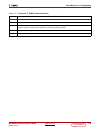

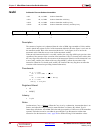

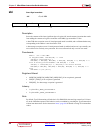

Registers Altered

•

rD, unless an exception is generated, in which case the register is unchanged

•

MSR[UM], MSR[VM], MSR[UMS], MSR[VMS], if a TLB miss exception or a data storage

exception is generated

•

ESR[EC], ESR[S], if an exception is generated

•

ESR[DIZ], if a data storage exception is generated

•

ESR[W], ESR[Rx], if an unaligned data access exception is generated

Latency

•

1 cycle with

C_AREA_OPTIMIZED=0

•

2 cycles with

C_AREA_OPTIMIZED=1

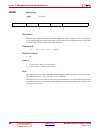

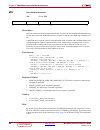

Note

By default, Type B Instructions will take the 16-bit IMM field value and sign extend it to 32 bits to

use as the immediate operand. This behavior can be overridden by preceding the Type B instruction

with an imm instruction. See the instruction

for details on using 32-bit immediate

values.

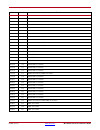

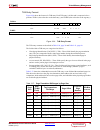

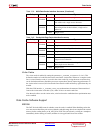

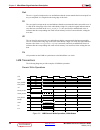

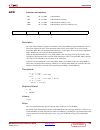

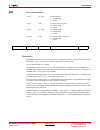

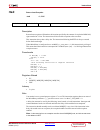

lhui

rD, rA, IMM

1 1 1 0 0 1

rD

rA

IMM

0

6

11

16

31

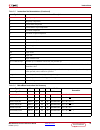

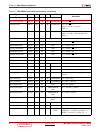

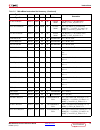

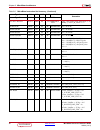

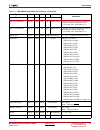

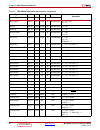

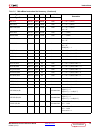

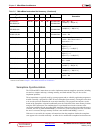

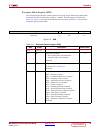

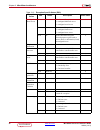

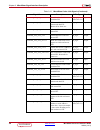

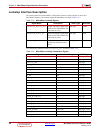

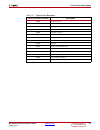

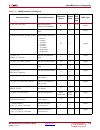

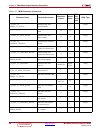

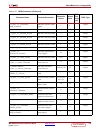

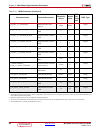

Summary of MicroBlaze

Page 1

Microblaze processor reference guide embedded development kit edk 14.7 ug081 (v14.7).

Page 2: Revision History

Microblaze processor reference guide www.Xilinx.Com ug081 (v14.7) notice of disclaimer the information disclosed to you hereunder (the “materials”) is provided solely for the selection and use of xilinx products. To the maximum extent permitted by applicable law: (1) materials are made available "as...

Page 3

Ug081 (v14.7) www.Xilinx.Com microblaze processor reference guide 07/24/06 6.1 minor corrections for edk 8.2 sp1 release 08/21/06 6.2 minor corrections for edk 8.2 sp2 release 08/29/06 6.3 minor corrections for edk 8.2 sp2 release 09/15/06 7.0 xilinx edk 9.1 release 02/22/07 7.1 minor corrections fo...

Page 4

Microblaze processor reference guide www.Xilinx.Com ug081 (v14.7).

Page 5: Table of Contents

Microblaze processor reference guide www.Xilinx.Com 5 ug081 (v14.7) revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 chapter 1: introduction guide contents . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

Microblaze processor reference guide www.Xilinx.Com 6 ug081 (v14.7) register usage conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152 stack convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 7: Introduction

Microblaze processor reference guide www.Xilinx.Com 7 ug081 (v14.7) chapter 1 introduction the microblaze™ processor reference guide provides information about the 32-bit soft processor, microblaze, which is part of the embedded processor development kit (edk). The document is intended as a guide to...

Page 8

8 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 1: introduction send feedback.

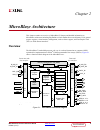

Page 9: Microblaze Architecture

Microblaze processor reference guide www.Xilinx.Com 9 ug081 (v14.7) chapter 2 microblaze architecture this chapter contains an overview of microblaze™ features and detailed information on microblaze architecture including big-endian or little-endian bit-reversed format, 32-bit general purpose regist...

Page 10

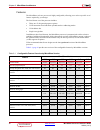

10 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture features the microblaze soft core processor is highly configurable, allowing you to select a specific set of features required by your design. The fixed feature set of the processor includes: • th...

Page 11

Microblaze processor reference guide www.Xilinx.Com 11 ug081 (v14.7) overview hardware exception support option option option option option option pattern compare instructions option option option option option option floating point unit (fpu) option option option option option option disable hardwa...

Page 12

12 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture configurable cache data widths - option option option option option count leading zeros instruction - option option option option option memory barrier instruction - yes yes yes yes yes stack over...

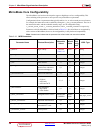

Page 13: Data Types and Endianness

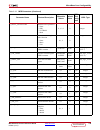

Microblaze processor reference guide www.Xilinx.Com 13 ug081 (v14.7) data types and endianness data types and endianness microblaze uses big-endian or little-endian format to represent data, depending on the parameter c_endianness . The hardware supported data types for microblaze are word, half wor...

Page 14: Instructions

14 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture instructions instruction summary all microblaze instructions are 32 bits and are defined as either type a or type b. Type a instructions have up to two source register operands and one destination...

Page 15

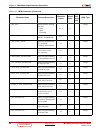

Microblaze processor reference guide www.Xilinx.Com 15 ug081 (v14.7) instructions = equality comparison != inequality comparison > greater than comparison >= greater than or equal comparison less than comparison less than or equal comparison + arithmetic add * arithmetic multiply / arithmetic divide...

Page 16

16 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture rsubkc rd,ra,rb 000111 rd ra rb 00000000000 rd := rb + ra + c cmp rd,ra,rb 000101 rd ra rb 00000000001 rd := rb + ra + 1 rd[0] := 0 if (rb >= ra) else rd[0] := 1 cmpu rd,ra,rb 000101 rd ra rb 0000...

Page 17

Microblaze processor reference guide www.Xilinx.Com 17 ug081 (v14.7) instructions tna putd ra,rb 010011 00000 ra rb 0 n 0 ta 0 00000 fsl rb[28:31] := ra (data write) msr[c] := fsl_m_full if n = 1 tne c a getd rd,rb 010011 rd 00000 rb 0 n 1 tae 00000 rd := fsl rb[28:31] (control read) msr[fsl] := 1 i...

Page 18

18 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture tn c a put ra,fslx 011011 00000 ra 1 n 1 ta 0000000 & fslx fslx := ra (control write, blocking if n = 0) msr[c] := fsl x _m_full if n = 1 or rd,ra,rb 100000 rd ra rb 00000000000 rd := ra or rb and...

Page 19

Microblaze processor reference guide www.Xilinx.Com 19 ug081 (v14.7) instructions wdc.Flush ra,rb 100100 00000 ra rb 00001110100 cache line is flushed, writing stored data to memory, and then cleared. Used when c_dcache_use_writeback = 1. Wdc.Clear ra,rb 100100 00000 ra rb 00001110110 cache line wit...

Page 20

20 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture brld rd,rb 100110 rd 10100 rb 00000000000 pc := pc + rb rd := pc bra rb 100110 00000 01000 rb 00000000000 pc := rb brad rb 100110 00000 11000 rb 00000000000 pc := rb brald rd,rb 100110 rd 11100 rb...

Page 21

Microblaze processor reference guide www.Xilinx.Com 21 ug081 (v14.7) instructions bri imm 101110 00000 00000 imm pc := pc + s(imm) brid imm 101110 00000 10000 imm pc := pc + s(imm) brlid rd,imm 101110 rd 10100 imm pc := pc + s(imm) rd := pc brai imm 101110 00000 01000 imm pc := s(imm) braid imm 1011...

Page 22

22 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture semaphore synchronization the lwx and swx. Instructions are used to implement common semaphore operations, including test and set, compare and swap, exchange memory, and fetch and add. They are al...

Page 23

Microblaze processor reference guide www.Xilinx.Com 23 ug081 (v14.7) instructions the read and the update. Other devices can read from the semaphore location during the operation. For a semaphore operation to work properly, the lwx instruction must be paired with an swx instruction, and both must sp...

Page 24

24 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture self-modifying code when using self-modifying code software must ensure that the modified instructions have been written to memory prior to fetching them for execution. There are several aspects t...

Page 25: Registers

Microblaze processor reference guide www.Xilinx.Com 25 ug081 (v14.7) registers registers microblaze has an orthogonal instruction set architecture. It has thirty-two 32-bit general purpose registers and up to eighteen 32-bit special purpose registers, depending on configured options. General purpose...

Page 26

26 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture special purpose registers program counter (pc) the program counter (pc) is the 32-bit address of the execution instruction. It can be read with an mfs instruction, but it cannot be written with an...

Page 27

Microblaze processor reference guide www.Xilinx.Com 27 ug081 (v14.7) registers table 2-9: machine status register (msr) bits name description reset value 0 cc arithmetic carry copy copy of the arithmetic carry (bit 29). Cc is always the same as bit c. 0 1:16 reserved 17 vms virtual protected mode sa...

Page 28

28 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture 23 ee exception enable 0 = hardware exceptions disabled 1 1 = hardware exceptions enabled only available if configured with exception support ( c_*_exception or c_use_mmu > 0 ) read/write 0 24 dce...

Page 29

Microblaze processor reference guide www.Xilinx.Com 29 ug081 (v14.7) registers 29 c arithmetic carry 0 = no carry (borrow) 1 = carry (no borrow) read/write 0 30 ie interrupt enable 0 = interrupts disabled 1 = interrupts enabled read/write 0 31 - reserved 0 1. The mmu exceptions (data storage excepti...

Page 30

30 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture exception address register (ear) the exception address register stores the full load/store address that caused the exception for the following: • an unaligned access exception that means the unali...

Page 31

Microblaze processor reference guide www.Xilinx.Com 31 ug081 (v14.7) registers exception status register (esr) the exception status register contains status bits for the processor. When read with the mfs instruction, the esr is specified by setting sa = 0x0005. The esr register is illustrated in fig...

Page 32

32 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture table 2-12: exception specific status (ess) exception cause bits name description reset value unaligned data access 20 w word access exception 0 = unaligned halfword access 1 = unaligned word acce...

Page 33

Microblaze processor reference guide www.Xilinx.Com 33 ug081 (v14.7) registers branch target register (btr) the branch target register only exists if the microblaze processor is configured to use exceptions. The register stores the branch target address for all delay slot branch instructions execute...

Page 34

34 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture floating point status register (fsr) the floating point status register contains status bits for the floating point unit. It can be read with an mfs, and written with an mts instruction. When read...

Page 35

Microblaze processor reference guide www.Xilinx.Com 35 ug081 (v14.7) registers stack low register (slr) the stack low register stores the stack low limit use to detect stack overflow. When the address of a load or store instruction using the stack pointer (register r1) as ra is less than the stack l...

Page 36

36 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture process identifier register (pid) the process identifier register is used to uniquely identify a software process during mmu address translation. It is controlled by the c_use_mmu configuration op...

Page 37

Microblaze processor reference guide www.Xilinx.Com 37 ug081 (v14.7) registers zone protection register (zpr) the zone protection register is used to override mmu memory protection defined in tlb entries. It is controlled by the c_use_mmu configuration option on microblaze. The register is only impl...

Page 38

38 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture translation look-aside buffer low register (tlblo) the translation look-aside buffer low register is used to access mmu unified translation look- aside buffer (utlb) entries. It is controlled by t...

Page 39

Microblaze processor reference guide www.Xilinx.Com 39 ug081 (v14.7) registers 23 wr writable when bit is set to 1, the page is writable and store instructions can be used to store data at addresses within the page. When bit is cleared to 0, the page is read-only (not writable). Attempts to store da...

Page 40

40 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture translation look-aside buffer high register (tlbhi) the translation look-aside buffer high register is used to access mmu unified translation look-aside buffer (utlb) entries. It is controlled by ...

Page 41

Microblaze processor reference guide www.Xilinx.Com 41 ug081 (v14.7) registers 26 e endian when this bit is set to 1, a the page is accessed as a little endian page if c_endianness is 0 (big endian), or as a big endian page otherwise. When cleared to 0, the page is accessed as a big endian page if c...

Page 42

42 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture translation look-aside buffer index register (tlbx) the translation look-aside buffer index register is used as an index to the unified translation look-aside buffer (utlb) when accessing the tlbl...

Page 43

Microblaze processor reference guide www.Xilinx.Com 43 ug081 (v14.7) registers translation look-aside buffer search index register (tlbsx) the translation look-aside buffer search index register is used to search for a virtual page number in the unified translation look-aside buffer (utlb). It is co...

Page 44

44 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture processor version register (pvr) the processor version register is controlled by the c_pvr configuration option on microblaze. • when c_pvr is set to 0 (none) the processor does not implement any ...

Page 45

Microblaze processor reference guide www.Xilinx.Com 45 ug081 (v14.7) registers table 2-25: processor version register 1 (pvr1) bits name description value 0:31 usr2 user configured value 2 c_pvr_user2 table 2-26: processor version register 2 (pvr2) bits name description value 0 daxi data side axi4 o...

Page 46

46 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture 20 fpu use fpu c_use_fpu > 0 (none) 21 mul64 use 64-bit hardware multiplier c_use_hw_mul = 2 (mul64) 22 fpu2 use floating point conversion and square root instructions c_use_fpu = 2 (extended) 23 ...

Page 47

Microblaze processor reference guide www.Xilinx.Com 47 ug081 (v14.7) registers 20:24 fsl number of stream links c_fsl_links 25:28 reserved 29:31 btc_size branch target cache size c_branch_target_cache_size table 2-28: processor version register 4 (pvr4) bits name description value 0 icu use instruct...

Page 48

48 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture 11:15 dcbs the base two logarithm of the data cache byte size log2(c_dcache_byte_size) 16 dau the data cache is used for all memory accesses within the cacheable range c_dcache_always_used 17 dwb ...

Page 49

Microblaze processor reference guide www.Xilinx.Com 49 ug081 (v14.7) registers table 2-34: processor version register 10 (pvr10) bits name description value 0:7 arch target architecture: defined by parameter c_family 0x6 0x7 0x8 0x9 0xa 0xb 0xc 0xd 0xe 0xf 0x10 0x11 0x12 = = = = = = = = = = = = = sp...

Page 50

50 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture table 2-36: processor version register 12 (pvr12) bits name description value 0:31 vectors location of microblaze vectors c_base_vectors send feedback.

Page 51: Pipeline Architecture

Microblaze processor reference guide www.Xilinx.Com 51 ug081 (v14.7) pipeline architecture pipeline architecture microblaze instruction execution is pipelined. For most instructions, each stage takes one clock cycle to complete. Consequently, the number of clock cycles necessary for a specific instr...

Page 52

52 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture delay slots when executing a taken branch with delay slot, only the fetch pipeline stage in microblaze is flushed. The instruction in the decode stage (branch delay slot) is allowed to complete. T...

Page 53: Memory Architecture

Microblaze processor reference guide www.Xilinx.Com 53 ug081 (v14.7) memory architecture memory architecture microblaze is implemented with a harvard memory architecture; instruction and data accesses are done in separate address spaces. Each address space has a 32-bit range (that is, handles up to ...

Page 54: Privileged Instructions

54 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture privileged instructions the following microblaze instructions are privileged: • get , getd,put,putd (except when explicitly allowed) • wic , wdc • mts • msrclr , msrset (except when only the c bit...

Page 55: Virtual-Memory Management

Microblaze processor reference guide www.Xilinx.Com 55 ug081 (v14.7) virtual-memory management virtual-memory management programs running on microblaze use effective addresses to access a flat 4 gb address space. The processor can interpret this address space in one of two ways, depending on the tra...

Page 56

56 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture straightforward than a virtual-mode memory manager. Real mode is often an appropriate solution for memory management in simple embedded environments, when access-protection is necessary, but virtu...

Page 57

Microblaze processor reference guide www.Xilinx.Com 57 ug081 (v14.7) virtual-memory management system software can use the pid to uniquely identify software processes (tasks, subroutines, threads) running on the processor. Independently compiled processes can operate in effective- address regions th...

Page 58

58 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture the microblaze tlb is physically implemented as three separate tlbs: • unified tlb—the utlb contains 64 entries and is pseudo-associative. Instruction-page and data-page translation can be stored ...

Page 59

Microblaze processor reference guide www.Xilinx.Com 59 ug081 (v14.7) virtual-memory management tlb entry format figure 2-20 shows the format of a tlb entry. Each tlb entry is 68 bits and is composed of two portions: tlblo (also referred to as the data entry), and tlbhi (also referred to as the tag e...

Page 60

60 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture tlb access when the mmu translates a virtual address (the combination of pid and effective address) into a physical address, it first examines the appropriate shadow tlb for the page translation e...

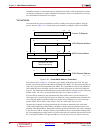

Page 61

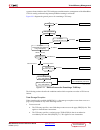

Microblaze processor reference guide www.Xilinx.Com 61 ug081 (v14.7) virtual-memory management system software initializes the utlb with page-translation entries, management of the microblaze utlb is usually performed using interrupt handlers running in real mode. Figure 2-21 diagrams the general pr...

Page 62

62 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture • from privileged mode: ♦ the tlb entry specifies a read-only page (tlblo[wr]=0) that is not otherwise overridden by the zone field (zpr[zn]‚ 10 and zpr[zn]‚ 11). This applies to store instruction...

Page 63

Microblaze processor reference guide www.Xilinx.Com 63 ug081 (v14.7) virtual-memory management a tlb entry with tid=0x00 represents a process-independent translation. Pages that are accessed globally by all processes should be assigned a tid value of 0x00. • execution—the processor executes instruct...

Page 64

64 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture individual utlb entries are invalidated using the mts instruction to clear the valid bit in the tag portion of a tlb entry (tlbhi[v]). When c_fault_tolerant is set to 1, the utlb block ram is prot...

Page 65

Microblaze processor reference guide www.Xilinx.Com 65 ug081 (v14.7) reset, interrupts, exceptions, and break reset, interrupts, exceptions, and break microblaze supports reset, interrupt, user exception, break, and hardware exceptions. The following section describes the execution flow associated w...

Page 66

66 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture equivalent pseudocode pc ← c_base_vectors + 0x00000000 msr ← c_reset_msr (see “microblaze core configurability” in chapter 3 ) ear ← 0; esr ← 0; fsr ← 0 pid ← 0; zpr ← 0; tlbx ← 0 reservation ← 0 ...

Page 67

Microblaze processor reference guide www.Xilinx.Com 67 ug081 (v14.7) reset, interrupts, exceptions, and break • unaligned exception • data bus exception • divide exception • fpu exception • stream exception exception causes • stream exception the stream exception (fsl or axi) is caused by executing ...

Page 68

68 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture ♦ the data side local memory (dlmb) can only cause instruction bus exception when c_fault_tolerant is set to 1, and either an uncorrectable error occurs in the lmb memory, as indicated by the due ...

Page 69

Microblaze processor reference guide www.Xilinx.Com 69 ug081 (v14.7) reset, interrupts, exceptions, and break equivalent pseudocode esr[ds] ← exception in delay slot if esr[ds] then btr ← branch target pc if mmu exception then if branch preceded by imm then r17 ← pc - 8 else r17 ← pc - 4 else r17 ← ...

Page 70

70 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture software breaks to perform a software break, use the brk and brki instructions. Refer to chapter 5, microblaze instruction set architecture for detailed information on software breaks. As a specia...

Page 71

Microblaze processor reference guide www.Xilinx.Com 71 ug081 (v14.7) reset, interrupts, exceptions, and break the address of each fast interrupt handler must be passed to the interrupt controller when initializing the interrupt system. When a particular interrupt occurs, this address is supplied by ...

Page 72: Instruction Cache

72 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture instruction cache overview microblaze can be used with an optional instruction cache for improved performance when executing code that resides outside the lmb address range. The instruction cache ...

Page 73

Microblaze processor reference guide www.Xilinx.Com 73 ug081 (v14.7) instruction cache instruction cache operation for every instruction fetched, the instruction cache detects if the instruction address belongs to the cacheable segment. If the address is non-cacheable, the cache controller ignores t...

Page 74: Data Cache

74 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture victim cache the victim cache is enabled by setting the parameter c_icache_victims to 2, 4 or 8. This defines the number of cache lines that can be stored in the victim cache. Whenever a cache lin...

Page 75

Microblaze processor reference guide www.Xilinx.Com 75 ug081 (v14.7) data cache general data cache functionality when the data cache is used, the memory address space is split into two segments: a cacheable segment and a non-cacheable segment. The cacheable area is determined by two parameters: c_dc...

Page 76

76 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture data cache operation the caching policy used by the microblaze data cache, write-back or write-through, is determined by the parameter c_dcache_use_writeback . When this parameter is set, a write-...

Page 77

Microblaze processor reference guide www.Xilinx.Com 77 ug081 (v14.7) data cache victim cache the victim cache is enabled by setting the parameter c_dcache_victims to 2, 4 or 8. This defines the number of cache lines that can be stored in the victim cache. Whenever a complete cache line is evicted fr...

Page 78

78 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture the contents of the cache are preserved when the cache is disabled. Wdc instruction the optional wdc instruction ( c_allow_dcache_wr=1 ) is used to invalidate or flush cache lines in the data cach...

Page 79: Floating Point Unit (Fpu)

Microblaze processor reference guide www.Xilinx.Com 79 ug081 (v14.7) floating point unit (fpu) floating point unit (fpu) overview the microblaze floating point unit is based on the ieee 754-1985 standard : • uses ieee 754 single precision floating point format, including definitions for infinity, no...

Page 80

80 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture for practical purposes only 3 and 5 are useful, while the others all represent either an error or numbers that can no longer be represented with full precision in a 32 bit format. Rounding the mic...

Page 81

Microblaze processor reference guide www.Xilinx.Com 81 ug081 (v14.7) floating point unit (fpu) software support the edk compiler system, based on gcc, provides support for the floating point unit compliant with the microblaze api. Compiler flags are automatically added to the gcc command line based ...

Page 82

82 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture float sum, t; int i; sum = 0.0f; for (i = 1; i t = (float)i; sum += t * t; } the above code requires a cast from an integer to a float on each loop iteration. This can be rewritten as: float sum, ...

Page 83: Stream Link Interfaces

Microblaze processor reference guide www.Xilinx.Com 83 ug081 (v14.7) stream link interfaces stream link interfaces microblaze can be configured with up to 16 fast simplex link (fsl) or axi4-stream interfaces, each consisting of one input and one output port. The channels are dedicated uni-directiona...

Page 84: Debug and Trace

84 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture debug and trace debug overview microblaze features a debug interface to support jtag based software debugging tools (commonly known as bdm or background debug mode debuggers) like the xilinx micro...

Page 85: Fault Tolerance

Microblaze processor reference guide www.Xilinx.Com 85 ug081 (v14.7) fault tolerance fault tolerance the fault tolerance features included in microblaze, enabled with c_fault_tolerant , provide error detection for internal block rams, and support for error detection and correction (ecc) in lmb block...

Page 86

86 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture the lmb bram interface controller v3.00.A or later provides the lmb ecc implementation. For details, including performance and resource utilization, see the logicore ip lmb bram interface controll...

Page 87

Microblaze processor reference guide www.Xilinx.Com 87 ug081 (v14.7) fault tolerance software support scrubbing to ensure that bit errors are not accumulated in block rams, they must be periodically scrubbed. The standalone bsp provides the function microblaze_scrub() to perform scrubbing of the ent...

Page 88

88 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture return xst_failure; } /* * start the interrupt controller such that interrupts are enabled for * all devices that cause interrupts, specifying real mode so that the * timer counter can cause inter...

Page 89

Microblaze processor reference guide www.Xilinx.Com 89 ug081 (v14.7) fault tolerance the self-test example can be found in the standalone bsp bram driver source code, typically in the subdirectory microblaze_0/libsrc/bram_v3_00_a/src/xbram_selftest.C . Scrubbing scrubbing methods scrubbing is perfor...

Page 90

90 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture small this system should be used when it is necessary to monitor error frequency, but there is no need for testing of the ecc function. It is a minimal system with correctable error counter regist...

Page 91: Lockstep Operation

Microblaze processor reference guide www.Xilinx.Com 91 ug081 (v14.7) lockstep operation lockstep operation microblaze is able to operate in a lockstep configuration, where two or more identical microblaze cores execute the same program. By comparing the outputs of the cores, any tampering attempts, ...

Page 92

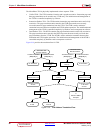

92 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture . Error detection the error detection use case requires that all transient and permanent faults are detected. This is essential in fail safe and fault tolerant applications, where redundancy is ut...

Page 93

Microblaze processor reference guide www.Xilinx.Com 93 ug081 (v14.7) lockstep operation figure 2-27: lockstep error detection application bram controller bram controller ilmb dlmb bram microblaze debug module microblaze slave debug c_lockstep_slave = 1 microblaze master debug c_lockstep_slave = 0 er...

Page 94

94 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 2: microblaze architecture send feedback.

Page 95: Overview

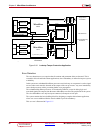

Microblaze processor reference guide www.Xilinx.Com 95 ug081 (v14.7) chapter 3 microblaze signal interface description this chapter describes the types of signal interfaces that can be used to connect microblaze™. Overview the microblaze core is organized as a harvard architecture with separate bus ...

Page 96: Microblaze I/o Overview

96 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description microblaze i/o overview the core interfaces shown in figure 3-1 and the following table 3-1 are defined as follows: m_axi_dp: peripheral data interface, axi4-lite or axi4 interface...

Page 97

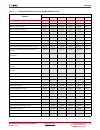

Microblaze processor reference guide www.Xilinx.Com 97 ug081 (v14.7) microblaze i/o overview table 3-1: summary of microblaze core i/o signal interface i/o description m_axi_dp_awid m_axi_dp o master write address id m_axi_dp_awaddr m_axi_dp o master write address m_axi_dp_awlen m_axi_dp o master bu...

Page 98

98 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description m_axi_dp_rid m_axi_dp i slave read id tag m_axi_dp_rdata m_axi_dp i slave read data m_axi_dp_rresp m_axi_dp i slave read response m_axi_dp_rlast m_axi_dp i slave read last m_axi_dp...

Page 99

Microblaze processor reference guide www.Xilinx.Com 99 ug081 (v14.7) microblaze i/o overview m_axi_ip_arcache m_axi_ip o master cache type m_axi_ip_arprot m_axi_ip o master protection type m_axi_ip_arqos m_axi_ip o master quality of service m_axi_ip_arvalid m_axi_ip o master read address valid m_axi...

Page 100

100 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description m_axi_dc_bid m_axi_dc i slave response id m_axi_dc_bvalid m_axi_dc i slave write response valid m_axi_dc_bready m_axi_dc o master response ready m_axi_dc_buser m_axi_dc i slave wr...

Page 101

Microblaze processor reference guide www.Xilinx.Com 101 ug081 (v14.7) microblaze i/o overview m_axi_dc_acready m_ace_dc o master snoop ready m_axi_dc_crready m_ace_dc i slave snoop response ready m_axi_dc_crvalid m_ace_dc o master snoop response valid m_axi_dc_crresp m_ace_dc o master snoop response...

Page 102

102 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description m_axi_ic_bready m_axi_ic o master response ready m_axi_ic_buser m_axi_ic i slave write response user signals m_axi_ic_wack m_ace_ic o slave write acknowledge m_axi_ic_arid m_axi_i...

Page 103

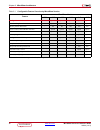

Microblaze processor reference guide www.Xilinx.Com 103 ug081 (v14.7) microblaze i/o overview m_axi_ic_crvalid m_ace_ic o master snoop response valid m_axi_ic_crresp m_ace_ic o master snoop response m_axi_ic_cdvalid m_ace_ic o master snoop data valid m_axi_ic_cdready m_ace_ic i slave snoop data read...

Page 104

104 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description dplb_maddrack dplb i data interface plb address acknowledge dplb_mrdbterm dplb i data interface plb terminate read burst indicator dplb_mrddack dplb i data interface plb read data...

Page 105

Microblaze processor reference guide www.Xilinx.Com 105 ug081 (v14.7) microblaze i/o overview iplb_mwrerr iplb i instruction interface plb slave write error indicator iplb_mirq iplb i instruction interface plb slave interrupt indicator iplb_mwrbterm iplb i instruction interface plb terminate write b...

Page 106

106 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description iready ilmb i instruction interface lmb data ready iwait ilmb i instruction interface lmb data wait ice ilmb i instruction interface lmb correctable error iue ilmb i instruction i...

Page 107

Microblaze processor reference guide www.Xilinx.Com 107 ug081 (v14.7) microblaze i/o overview reset 2 core i core reset, active high. Should be held for at least 1 clk clock cycle. Mb_reset 2 core i core reset, active high. Should be held for at least 1 clk clock cycle. Clk core i clock 3 ext_brk co...

Page 108

108 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description axi4 and ace interface description memory mapped interfaces peripheral interfaces the microblaze axi4 memory mapped peripheral interfaces are implemented as 32-bit masters. Each o...

Page 109

Microblaze processor reference guide www.Xilinx.Com 109 ug081 (v14.7) axi4 and ace interface description interface parameters and signals the relationship between microblaze parameter settings and axi4 interface behavior for tool- assigned parameters is summarized in table 3-2 . Table 3-2: axi memor...

Page 110

110 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description values for access permissions, memory types, quality of service and shareability domain are defined in table 3-3 . Table 3-3: axi interface signal definitions interface signal des...

Page 111

Microblaze processor reference guide www.Xilinx.Com 111 ug081 (v14.7) processor local bus (plb) interface description please refer to the amba ® axi and ace protocol specification, arm ihi 0022e document for details. Stream interfaces the microblaze axi4-stream interfaces (m0_axis..M15_axis, s0_axis...

Page 112

112 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description local memory bus (lmb) interface description the lmb is a synchronous bus used primarily to access on-chip block ram. It uses a minimum number of control signals and a simple prot...

Page 113

Microblaze processor reference guide www.Xilinx.Com 113 ug081 (v14.7) local memory bus (lmb) interface description : data_write[0:31] the write data bus is an output from the core and contains the data that is written to memory. It is valid only when as is high. Only the byte lanes specified by byte...

Page 114

114 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description wait the wait signal is an input to the core and indicates that the current transfer has been accepted, but not yet completed. It is sampled on the rising edge of the clock. Ce th...

Page 115

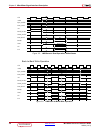

Microblaze processor reference guide www.Xilinx.Com 115 ug081 (v14.7) local memory bus (lmb) interface description generic read operations figure 3-3: lmb generic write operation, n wait states clk addr byte_enable data_write as read_strobe write_strobe data_read ready wait ce ue a0 be0 d0 don’t car...

Page 116

116 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description back-to-back write operation figure 3-5: lmb generic read operation, n wait states clk addr byte_enable data_write as read_strobe write_strobe data_read ready wait ce ue a0 d0 don...

Page 117

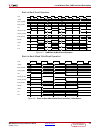

Microblaze processor reference guide www.Xilinx.Com 117 ug081 (v14.7) local memory bus (lmb) interface description back-to-back read operation back-to-back mixed write/read operation figure 3-7: lmb back-to-back read operation figure 3-8: back-to-back mixed write/read operation, 0 wait states clk ad...

Page 118

118 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description figure 3-9: back-to-back mixed write/read operation, n wait states clk addr byte_enable data_write as read_strobe write_strobe data_read ready wait ce ue a0 a1 a2 don’t care d0 be...

Page 119

Microblaze processor reference guide www.Xilinx.Com 119 ug081 (v14.7) local memory bus (lmb) interface description read and write data steering the microblaze data-side bus interface performs the read steering and write steering required to support the following transfers: • byte, halfword, and word...

Page 120

120 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description note: other masters may have more restrictive requirements for byte lane placement than those allowed by microblaze. Slave devices are typically attached “left-justified” with byt...

Page 121

Microblaze processor reference guide www.Xilinx.Com 121 ug081 (v14.7) fast simplex link (fsl) interface description fast simplex link (fsl) interface description the fast simplex link bus provides a point-to-point communication channel between an output fifo and an input fifo. For more information o...

Page 122

122 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description fsl transactions fsl bus write operation a write to the fsl bus is performed by microblaze using one of the put or putd instructions. A write operation transfers the register cont...

Page 123

Microblaze processor reference guide www.Xilinx.Com 123 ug081 (v14.7) xilinx cachelink (xcl) interface description xilinx cachelink (xcl) interface description xilinx cachelink (xcl) is a high performance solution for external memory accesses. The microblaze cachelink interface is designed to connec...

Page 124

124 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description icache_fsl_in_data read data from i-side return read data fsl std_logic_ vector (0 to 31) input icache_fsl_in_control fsl control-bit from i-side return read data fsl. Reserved fo...

Page 125

Microblaze processor reference guide www.Xilinx.Com 125 ug081 (v14.7) xilinx cachelink (xcl) interface description cachelink transactions all individual cachelink accesses follow the fsl fifo based transaction protocol: • access information is encoded over the fsl data and control signals (e.G. Dcac...

Page 126

126 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description • linear fetch is used by the ixcl2 and dxcl2 protocol, selected when c_icache_interface = 1 (ixcl2) and c_dcache_interface = 1 (dxcl2), respectively. The address output on the ca...

Page 127

Microblaze processor reference guide www.Xilinx.Com 127 ug081 (v14.7) xilinx cachelink (xcl) interface description with the dxcl2 protocol (linear fetch): 4. Store words from dcache_fsl_in_data to the cache 5. Forward the requested word to the execution unit in order to resume execution 6. Store rem...

Page 128

128 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description lockstep interface description the lockstep interface on microblaze is designed to connect a master and one or more slave microblaze instances. The lockstep signals on microblaze ...

Page 129

Microblaze processor reference guide www.Xilinx.Com 129 ug081 (v14.7) lockstep interface description iplb_m_size 198 to 201 std_logic_vector iplb_m_tattribute 202 to 217 std_logic_vector iplb_m_type 218 to 220 std_logic_vector iplb_m_wrdbus 1 221 to 348 std_logic_vector dplb_m_abort 349 std_logic dp...

Page 130

130 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description m_axi_ip_awcache 712 to 715 std_logic_vector m_axi_ip_awprot 716 to 718 std_logic_vector m_axi_ip_awqos 719 to 722 std_logic_vector m_axi_ip_awvalid 723 std_logic m_axi_ip_wdata 7...

Page 131

Microblaze processor reference guide www.Xilinx.Com 131 ug081 (v14.7) lockstep interface description m_axi_dp_arsize 962 to 964 std_logic_vector m_axi_dp_arburst 965 to 966 std_logic_vector m_axi_dp_arlock 967 std_logic m_axi_dp_arcache 968 to 971 std_logic_vector m_axi_dp_arprot 972 to 974 std_logi...

Page 132

132 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description m_axi_ic_wack 2784 std_logic m_axi_ic_arid 2785 std_logic_vector m_axi_ic_araddr 2786 to 2907 std_logic_vector m_axi_ic_arlen 2818 to 2825 std_logic_vector m_axi_ic_arsize 2826 to...

Page 133

Microblaze processor reference guide www.Xilinx.Com 133 ug081 (v14.7) lockstep interface description m_axi_dc_wlast 3515 std_logic m_axi_dc_wvalid 3516 std_logic m_axi_dc_wuser 3517 std_logic m_axi_dc_bready 3518 std_logic m_axi_dc_wack 2 3519 std_logic m_axi_dc_arid 3520 std_logic m_axi_dc_araddr 3...

Page 134

134 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description trace_data_address 3737 to 3768 std_logic_vector trace_data_write_value 3769 to 3800 std_logic_vector trace_data_byte_enable 3801 to 3804 std_logic_vector trace_data_access 3805 s...

Page 135: Debug Interface Description

Microblaze processor reference guide www.Xilinx.Com 135 ug081 (v14.7) debug interface description debug interface description the debug interface on microblaze is designed to work with the xilinx microprocessor debug module (mdm) ip core. The mdm is controlled by the xilinx microprocessor debugger (...

Page 136

136 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description trace_new_reg_value 1 destination register update value std_logic_vector (0 to 31) output trace_exception_taken 1 instruction result in taken exception std_logic output trace_exce...

Page 137

Microblaze processor reference guide www.Xilinx.Com 137 ug081 (v14.7) trace interface description table 3-17: type of trace exception trace_exception_kind [0:4] description 00000 stream exception 1 1. Added for microblaze v7.00 00001 unaligned exception 00010 illegal opcode exception 00011 instructi...

Page 138

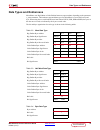

138 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description microblaze core configurability the microblaze core has been developed to support a high degree of user configurability. This allows tailoring of the processor to meet specific co...

Page 139

Microblaze processor reference guide www.Xilinx.Com 139 ug081 (v14.7) microblaze core configurability c_avoid_primitives disallow fpga primitives 0 = none 1 = srl 2 = lutram 3 = both 0, 1, 2, 3 0 integer c_pvr processor version register mode selection 0 = none 1 = basic 2 = full 0, 1, 2 0 integer c_...

Page 140

140 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description c_use_fpu include hardware floating point unit 0 = none 1 = basic 2 = extended 0, 1, 2 0 integer c_use_msr_instr enable use of instructions: msrset and msrclr 0, 1 1 integer c_use...

Page 141

Microblaze processor reference guide www.Xilinx.Com 141 ug081 (v14.7) microblaze core configurability c_ecc_use_ce_exception generate bus error exceptions for correctable errors 0,1 0 integer c_use_stack_protection generate exception for stack overflow or stack underflow 0,1 0 integer c_debug_enable...

Page 142

142 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description c_icache_always_used instruction cache interface used for all memory accesses in the cacheable range 0, 1 0 integer c_icache_interface instruction cache cachelink interface protoc...

Page 143

Microblaze processor reference guide www.Xilinx.Com 143 ug081 (v14.7) microblaze core configurability c_dcache_line_len data cache line length 4, 8 4 integer c_dcache_always_used data cache interface used for all accesses in the cacheable range 0, 1 0 integer c_dcache_interface data cache cachelink ...

Page 144

144 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description c_iplb_dwidth instruction side plb data width 32 32 integer c_iplb_native_dwidth instruction side plb native data width 32 32 integer c_iplb_burst_en instruction side plb burst en...

Page 145

Microblaze processor reference guide www.Xilinx.Com 145 ug081 (v14.7) microblaze core configurability c_use_ext_nm_brk enable external non- maskable break handling 0,1 0 yes integer c_use_branch_target_cache 5 enable branch target cache 0,1 0 integer c_branch_target_cache_size 5 branch target cache ...

Page 146

146 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description c_m_axi_ip_ thread_id_width instruction side axi thread id width 1 1 integer c_m_axi_ip_data_width instruction side axi data width 32 32 integer c_m_axi_ip_addr_width instruction ...

Page 147

Microblaze processor reference guide www.Xilinx.Com 147 ug081 (v14.7) microblaze core configurability c_m_axi_dc_supports_ user_signals data cache axi user signal support 1 1 integer c_m_axi_dc_protocol data cache axi protocol axi4 axi4 string c_m_axi_dc_awuser_width data cache axi user width 5 5 in...

Page 148

148 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description c_m_axi_ic_protocol instruction cache axi protocol axi4 axi4 string c_m_axi_ic_awuser_width instruction cache axi user width 5 5 integer c_m_axi_ic_aruser_width instruction cache ...

Page 149

Microblaze processor reference guide www.Xilinx.Com 149 ug081 (v14.7) microblaze core configurability table 3-19: parameter c_family allowable values allowable values artix aartix7 artix7 artix7l qartix7 qartix7l kintex kintex7 kintex7l qkintex7 qkintex7l spartan aspartan3 aspartan3a aspartan3adsp a...

Page 150

150 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 3: microblaze signal interface description send feedback.

Page 151: Data Types

Microblaze processor reference guide www.Xilinx.Com 151 ug081 (v14.7) chapter 4 microblaze application binary interface this chapter describes microblaze™ application binary interface (abi), which is important for developing software in assembly language for the soft processor. The microblaze gnu co...

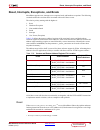

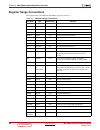

Page 152: Register Usage Conventions

152 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 4: microblaze application binary interface register usage conventions the register usage convention for microblaze is given in table 4-2 . Table 4-2: register usage conventions register type enforcement purpose r0 dedicate...

Page 153: Stack Convention

Microblaze processor reference guide www.Xilinx.Com 153 ug081 (v14.7) stack convention the architecture for microblaze defines 32 general purpose registers (gprs). These registers are classified as volatile, non-volatile, and dedicated. • the volatile registers (also known as caller-save) are used a...

Page 154

154 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 4: microblaze application binary interface table 4-3: stack convention consider an example where func1 calls func2, which in turn calls func3. The stack representation at different instances is depicted in figure 4-1 . Aft...

Page 155: Memory Model

Microblaze processor reference guide www.Xilinx.Com 155 ug081 (v14.7) memory model calling convention the caller function passes parameters to the callee function using either the registers (r5 through r10) or on its own stack frame. The callee uses the stack area of the caller to store the paramete...

Page 156

156 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 4: microblaze application binary interface interrupt and exception handling microblaze assumes certain address locations for handling interrupts and exceptions as indicated in table 4-4 . At these locations, code is writte...

Page 157

Microblaze processor reference guide www.Xilinx.Com 157 ug081 (v14.7) interrupt and exception handling in the current microblaze system, there are dummy routines for interrupt and user exception handling, which you can change. In order to override these routines and link your own interrupt and excep...

Page 158

158 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 4: microblaze application binary interface send feedback.

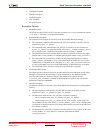

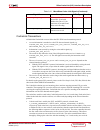

Page 159: Notation

Microblaze processor reference guide www.Xilinx.Com 159 ug081 (v14.7) chapter 5 microblaze instruction set architecture this chapter provides a detailed guide to the instruction set architecture of microblaze™. Notation the symbols used throughout this chapter are defined in table 5-1 . Table 5-1: s...

Page 160

160 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture sext( x ) sign-extend x mem( x ) memory location at address x fslx stream interface x (fsl or axi) lsw( x ) least significant word of x isdnz( x ) floating point: true if x is den...

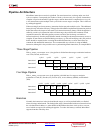

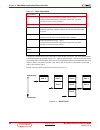

Page 161: Formats

Microblaze processor reference guide www.Xilinx.Com 161 ug081 (v14.7) formats formats microblaze uses two instruction formats: type a and type b. Type a type a is used for register-register instructions. It contains the opcode, one destination and two source registers. Type b type b is used for regi...

Page 162: Add

162 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture add arithmetic add description the sum of the contents of registers ra and rb, is placed into register rd. Bit 3 of the instruction (labeled as k in the figure) is set to one for ...

Page 163: Addi

Microblaze processor reference guide www.Xilinx.Com 163 ug081 (v14.7) instructions addi arithmetic add immediate description the sum of the contents of registers ra and the value in the imm field, sign-extended to 32 bits, is placed into register rd. Bit 3 of the instruction (labeled as k in the fig...

Page 164: and

164 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture and logical and description the contents of register ra are anded with the contents of register rb; the result is placed into register rd. Pseudocode (rd) ← (ra) ∧ (rb) registers ...

Page 165: Andi

Microblaze processor reference guide www.Xilinx.Com 165 ug081 (v14.7) instructions andi logial and with immediate description the contents of register ra are anded with the value of the imm field, sign-extended to 32 bits; the result is placed into register rd. Pseudocode (rd) ← (ra) ∧ sext(imm) reg...

Page 166: Andn

166 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture andn logical and not description the contents of register ra are anded with the logical complement of the contents of register rb; the result is placed into register rd. Pseudocod...

Page 167: Andni

Microblaze processor reference guide www.Xilinx.Com 167 ug081 (v14.7) instructions andni logical and not with immediate description the imm field is sign-extended to 32 bits. The contents of register ra are anded with the logical complement of the extended imm field; the result is placed into regist...

Page 168: Beq

168 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture beq branch if equal description branch if ra is equal to 0, to the instruction located in the offset value of rb. The target of the branch will be the instruction at address pc + ...

Page 169: Beqi

Microblaze processor reference guide www.Xilinx.Com 169 ug081 (v14.7) instructions beqi branch immediate if equal description branch if ra is equal to 0, to the instruction located in the offset value of imm. The target of the branch will be the instruction at address pc + imm. The mnemonic beqid wi...

Page 170: Bge

170 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture bge branch if greater or equal description branch if ra is greater or equal to 0, to the instruction located in the offset value of rb. The target of the branch will be the instru...

Page 171: Bgei

Microblaze processor reference guide www.Xilinx.Com 171 ug081 (v14.7) instructions bgei branch immediate if greater or equal description branch if ra is greater or equal to 0, to the instruction located in the offset value of imm. The target of the branch will be the instruction at address pc + imm....

Page 172: Bgt

172 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture bgt branch if greater than description branch if ra is greater than 0, to the instruction located in the offset value of rb. The target of the branch will be the instruction at ad...

Page 173: Bgti

Microblaze processor reference guide www.Xilinx.Com 173 ug081 (v14.7) instructions bgti branch immediate if greater than description branch if ra is greater than 0, to the instruction located in the offset value of imm. The target of the branch will be the instruction at address pc + imm. The mnemon...

Page 174: Ble

174 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture ble branch if less or equal description branch if ra is less or equal to 0, to the instruction located in the offset value of rb. The target of the branch will be the instruction ...

Page 175: Blei

Microblaze processor reference guide www.Xilinx.Com 175 ug081 (v14.7) instructions blei branch immediate if less or equal description branch if ra is less or equal to 0, to the instruction located in the offset value of imm. The target of the branch will be the instruction at address pc + imm. The m...

Page 176: Blt

176 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture blt branch if less than description branch if ra is less than 0, to the instruction located in the offset value of rb. The target of the branch will be the instruction at address ...

Page 177: Blti

Microblaze processor reference guide www.Xilinx.Com 177 ug081 (v14.7) instructions blti branch immediate if less than description branch if ra is less than 0, to the instruction located in the offset value of imm. The target of the branch will be the instruction at address pc + imm. The mnemonic blt...

Page 178: Bne

178 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture bne branch if not equal description branch if ra not equal to 0, to the instruction located in the offset value of rb. The target of the branch will be the instruction at address ...

Page 179: Bnei

Microblaze processor reference guide www.Xilinx.Com 179 ug081 (v14.7) instructions bnei branch immediate if not equal description branch if ra not equal to 0, to the instruction located in the offset value of imm. The target of the branch will be the instruction at address pc + imm. The mnemonic bne...

Page 180

180 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture br unconditional branch description branch to the instruction located at address determined by rb. The mnemonics brld and brald will set the l bit. If the l bit is set, linking wi...

Page 181

Microblaze processor reference guide www.Xilinx.Com 181 ug081 (v14.7) instructions note the instructions brl and bral are not available. A delay slot must not be used by the following: imm, branch, or break instructions. Interrupts and external hardware breaks are deferred until after the delay slot...

Page 182: Bri

182 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture bri unconditional branch immediate description branch to the instruction located at address determined by imm, sign-extended to 32 bits. The mnemonics brlid and bralid will set th...

Page 183

Microblaze processor reference guide www.Xilinx.Com 183 ug081 (v14.7) instructions registers altered • rd • pc • msr[um], msr[vm] latency • 1 cycle (if successful branch prediction occurs) • 2 cycles (if the d bit is set) • 3 cycles (if the d bit is not set, or a branch prediction mispredict occurs)...

Page 184: Brk

184 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture brk break description branch and link to the instruction located at address value in rb. The current value of pc will be stored in rd. The bip flag in the msr will be set, and the...

Page 185: Brki

Microblaze processor reference guide www.Xilinx.Com 185 ug081 (v14.7) instructions brki break immediate description branch and link to the instruction located at address value in imm, sign-extended to 32 bits. The current value of pc will be stored in rd. The bip flag in the msr will be set, and the...

Page 186

186 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture bs barrel shift description shifts the contents of register ra by the amount specified in register rb and puts the result in register rd. The mnemonic bsll sets the s bit (side bi...

Page 187: Bsi

Microblaze processor reference guide www.Xilinx.Com 187 ug081 (v14.7) instructions bsi barrel shift immediate description shifts the contents of register ra by the amount specified by imm and puts the result in register rd. The mnemonic bsll sets the s bit (side bit). If the s bit is set, the barrel...

Page 188: Clz

188 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture clz count leading zeros description this instruction counts the number of leading zeros in register ra starting from the most significant bit. The result is a number between 0 and...

Page 189: Cmp

Microblaze processor reference guide www.Xilinx.Com 189 ug081 (v14.7) instructions cmp integer compare description the contents of register ra is subtracted from the contents of register rb and the result is placed into register rd. The msb bit of rd is adjusted to shown true relation between ra and...

Page 190: Fadd

190 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture fadd floating point arithmetic add description the floating point sum of registers ra and rb, is placed into register rd. Pseudocode if isdnz(ra) or isdnz(rb) then (rd) ← 0xffc000...

Page 191: Frsub

Microblaze processor reference guide www.Xilinx.Com 191 ug081 (v14.7) instructions frsub reverse floating point arithmetic subtraction description the floating point value in ra is subtracted from the floating point value in rb and the result is placed into register rd. Pseudocode if isdnz(ra) or is...

Page 192: Fmul

192 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture fmul floating point arithmetic multiplication description the floating point value in ra is multiplied with the floating point value in rb and the result is placed into register r...

Page 193: Fdiv

Microblaze processor reference guide www.Xilinx.Com 193 ug081 (v14.7) instructions fdiv floating point arithmetic division description the floating point value in rb is divided by the floating point value in ra and the result is placed into register rd. Pseudocode if isdnz(ra) or isdnz(rb) then (rd)...

Page 194: Fcmp

194 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture fcmp floating point number comparison description the floating point value in rb is compared with the floating point value in ra and the comparison result is placed into register ...

Page 195

Microblaze processor reference guide www.Xilinx.Com 195 ug081 (v14.7) instructions table 5-2: floating point comparison operation comparison type operand relationship description opsel (rb) > (ra) (rb) (rb) = (ra) issignan(ra) or issignan(rb) isquietnan(ra) or isquietnan(rb) unordered 000 (rd) ← 0 (...

Page 196: Flt

196 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture flt floating point convert integer to float description converts the signed integer in register ra to floating point and puts the result in register rd. This is a 32-bit rounding ...

Page 197: Fint

Microblaze processor reference guide www.Xilinx.Com 197 ug081 (v14.7) instructions fint floating point convert float to integer description converts the floating point number in register ra to a signed integer and puts the result in register rd. This is a 32-bit signed conversion that will produce a...

Page 198: Fsqrt

198 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture fsqrt floating point arithmetic square root description performs a floating point square root on the value in ra and puts the result in register rd. Pseudocode if isdnz(ra) then (...

Page 199: Get

Microblaze processor reference guide www.Xilinx.Com 199 ug081 (v14.7) instructions get get from stream interface description microblaze will read from the link x interface and place the result in register rd. If the available number of links set by c_fsl_links is less than or equal to fslx, link 0 i...

Page 201: Getd

Microblaze processor reference guide www.Xilinx.Com 201 ug081 (v14.7) instructions getd get from stream interface dynamic description microblaze will read from the interface defined by the four least significant bits in rb and place the result in register rd. If the available number of links set by ...

Page 203: Idiv

Microblaze processor reference guide www.Xilinx.Com 203 ug081 (v14.7) instructions idiv integer divide description the contents of register rb is divided by the contents of register ra and the result is placed into register rd. If the u bit is set, ra and rb are considered unsigned values. If the u ...

Page 204: Imm

204 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture imm immediate description the instruction imm loads the imm value into a temporary register. It also locks this value so it can be used by the following instruction and form a 32-...

Page 205: Lbu

Microblaze processor reference guide www.Xilinx.Com 205 ug081 (v14.7) instructions lbu load byte unsigned description loads a byte (8 bits) from the memory location that results from adding the contents of registers ra and rb. The data is placed in the least significant byte of register rd and the o...

Page 206: Lbui

206 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture lbui load byte unsigned immediate description loads a byte (8 bits) from the memory location that results from adding the contents of register ra with the value in imm, sign-exten...

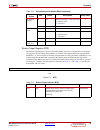

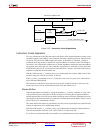

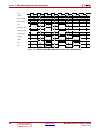

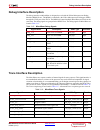

Page 207: Lhu

Microblaze processor reference guide www.Xilinx.Com 207 ug081 (v14.7) instructions lhu load halfword unsigned description loads a halfword (16 bits) from the halfword aligned memory location that results from adding the contents of registers ra and rb. The data is placed in the least significant hal...

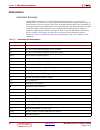

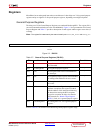

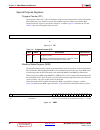

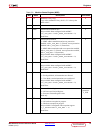

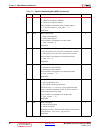

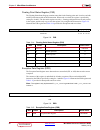

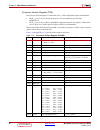

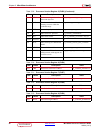

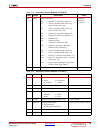

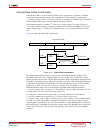

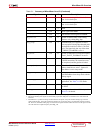

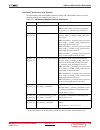

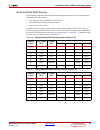

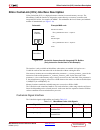

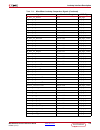

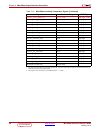

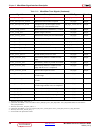

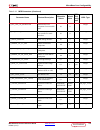

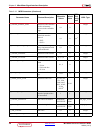

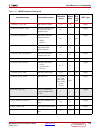

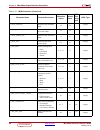

Page 208: Lhui

208 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture lhui load halfword unsigned immediate description loads a halfword (16 bits) from the halfword aligned memory location that results from adding the contents of register ra and the...

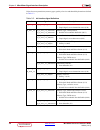

Page 209

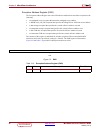

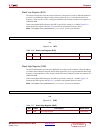

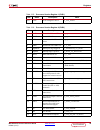

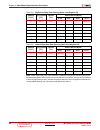

Microblaze processor reference guide www.Xilinx.Com 209 ug081 (v14.7) instructions lw load word description loads a word (32 bits) from the word aligned memory location that results from adding the contents of registers ra and rb. The data is placed in register rd. If the r bit is set, the bytes in ...

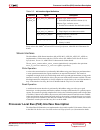

Page 210: Lwi

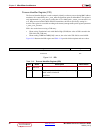

210 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture lwi load word immediate description loads a word (32 bits) from the word aligned memory location that results from adding the contents of register ra and the value imm, sign-exten...

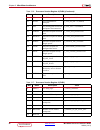

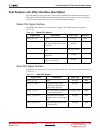

Page 211: Lwx

Microblaze processor reference guide www.Xilinx.Com 211 ug081 (v14.7) instructions lwx load word exclusive description loads a word (32 bits) from the word aligned memory location that results from adding the contents of registers ra and rb. The data is placed in register rd, and the reservation bit...

Page 212

212 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture registers altered • rd and msr[c], unless an exception is generated, in which case they are unchanged • msr[um], msr[vm], msr[ums], msr[vms], if a tlb miss exception or a data sto...

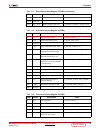

Page 213: Mbar

Microblaze processor reference guide www.Xilinx.Com 213 ug081 (v14.7) instructions mbar memory barrier description this instruction ensures that outstanding memory accesses on memory interfaces are completed before any subsequent instructions are executed. This is necessary to guarantee that self-mo...

Page 214: Mfs

214 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture mfs move from special purpose register description copies the contents of the special purpose register rs into register rd. The special purpose registers tlblo and tlbhi are used ...

Page 215

Microblaze processor reference guide www.Xilinx.Com 215 ug081 (v14.7) instructions the value read from fsr may not include effects of the immediately preceding instruction (dependent on pipeline stall behavior). An instruction that does not affect fsr must precede the mfs instruction to guarantee co...

Page 216: Msrclr

216 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture msrclr read msr and clear bits in msr description copies the contents of the special purpose register msr into register rd. Bit positions in the imm value that are 1 are cleared i...

Page 217: Msrset

Microblaze processor reference guide www.Xilinx.Com 217 ug081 (v14.7) instructions msrset read msr and set bits in msr description copies the contents of the special purpose register msr into register rd. Bit positions in the imm value that are 1 are set in the msr. Bit positions that are 0 in the i...

Page 218

218 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture when setting msr[vm] the instruction must always be followed by a synchronizing branch instruction, for example bri 4. Send feedback.

Page 219: Mts

Microblaze processor reference guide www.Xilinx.Com 219 ug081 (v14.7) instructions mts move to special purpose register description copies the contents of register rd into the special purpose register rs. The special purpose registers tlblo and tlbhi are used to copy to the unified tlb entry indexed...

Page 220

220 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture to refer to special purpose registers in assembly language, use rmsr for msr, rfsr for fsr, rslr for slr, rshr for shr, rpid for pid, rzpr for zpr, rtlblo for tlblo, rtlbhi for tl...

Page 221: Mul

Microblaze processor reference guide www.Xilinx.Com 221 ug081 (v14.7) instructions mul multiply description multiplies the contents of registers ra and rb and puts the result in register rd. This is a 32-bit by 32-bit multiplication that will produce a 64-bit result. The least significant word of th...

Page 222: Mulh

222 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture mulh multiply high description multiplies the contents of registers ra and rb and puts the result in register rd. This is a 32-bit by 32-bit signed multiplication that will produc...

Page 223: Mulhu

Microblaze processor reference guide www.Xilinx.Com 223 ug081 (v14.7) instructions mulhu multiply high unsigned description multiplies the contents of registers ra and rb and puts the result in register rd. This is a 32-bit by 32-bit unsigned multiplication that will produce a 64-bit unsigned result...

Page 224: Mulhsu

224 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture mulhsu multiply high signed unsigned description multiplies the contents of registers ra and rb and puts the result in register rd. This is a 32-bit signed by 32-bit unsigned mult...

Page 225: Muli

Microblaze processor reference guide www.Xilinx.Com 225 ug081 (v14.7) instructions muli multiply immediate description multiplies the contents of registers ra and the value imm, sign-extended to 32 bits; and puts the result in register rd. This is a 32-bit by 32-bit multiplication that will produce ...

Page 226

226 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture or logical or description the contents of register ra are ored with the contents of register rb; the result is placed into register rd. Pseudocode (rd) ← (ra) ∨ (rb) registers alt...

Page 227: Ori

Microblaze processor reference guide www.Xilinx.Com 227 ug081 (v14.7) instructions ori logical or with immediate description the contents of register ra are ored with the extended imm field, sign-extended to 32 bits; the result is placed into register rd. Pseudocode (rd) ← (ra) ∨ sext(imm) registers...

Page 228: Pcmpbf

228 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture pcmpbf pattern compare byte find description the contents of register ra is bytewise compared with the contents in register rb. • rd is loaded with the position of the first match...

Page 229: Pcmpeq

Microblaze processor reference guide www.Xilinx.Com 229 ug081 (v14.7) instructions pcmpeq pattern compare equal description the contents of register ra is compared with the contents in register rb. • rd is loaded with 1 if they match, and 0 if not pseudocode if (rb) = (ra) then (rd) ← 1 else (rd) ← ...

Page 230: Pcmpne

230 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture pcmpne pattern compare not equal description the contents of register ra is compared with the contents in register rb. • rd is loaded with 0 if they match, and 1 if not pseudocode...

Page 231: Put

Microblaze processor reference guide www.Xilinx.Com 231 ug081 (v14.7) instructions put put to stream interface description microblaze will write the value from register ra to the link x interface. If the available number of links set by c_fsl_links is less than or equal to fslx, link 0 is used. The ...

Page 233: Putd

Microblaze processor reference guide www.Xilinx.Com 233 ug081 (v14.7) instructions putd put to stream interface dynamic description microblaze will write the value from register ra to the link interface defined by the four least significant bits in rb. If the available number of links set by c_fsl_l...

Page 235: Rsub

Microblaze processor reference guide www.Xilinx.Com 235 ug081 (v14.7) instructions rsub arithmetic reverse subtract description the contents of register ra is subtracted from the contents of register rb and the result is placed into register rd. Bit 3 of the instruction (labeled as k in the figure) ...

Page 236: Rsubi

236 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture rsubi arithmetic reverse subtract immediate description the contents of register ra is subtracted from the value of imm, sign-extended to 32 bits, and the result is placed into re...

Page 237: Rtbd

Microblaze processor reference guide www.Xilinx.Com 237 ug081 (v14.7) instructions rtbd return from break rn from interrupt description return from break will branch to the location specified by the contents of ra plus the imm field, sign-extended to 32 bits. It will also enable breaks after executi...

Page 238: Rtid

238 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture rtid return from interrupt rn from interrupt description return from interrupt will branch to the location specified by the contents of ra plus the imm field, sign-extended to 32 ...

Page 239: Rted

Microblaze processor reference guide www.Xilinx.Com 239 ug081 (v14.7) instructions rted return from exception description return from exception will branch to the location specified by the contents of ra plus the imm field, sign-extended to 32 bits. The instruction will also enable exceptions after ...

Page 240: Rtsd

240 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture rtsd return from subroutine description return from subroutine will branch to the location specified by the contents of ra plus the imm field, sign-extended to 32 bits. This instr...

Page 241

Microblaze processor reference guide www.Xilinx.Com 241 ug081 (v14.7) instructions sb store byte description stores the contents of the least significant byte of register rd, into the memory location that results from adding the contents of registers ra and rb. If the r bit is set, a byte reversed m...

Page 242: Sbi

242 www.Xilinx.Com microblaze processor reference guide ug081 (v14.7) chapter 5: microblaze instruction set architecture sbi store byte immediate description stores the contents of the least significant byte of register rd, into the memory location that results from adding the contents of register r...

Page 243: Sext16