- DL manuals

- Xilinx

- Computer Hardware

- ML605

- User Manual

Xilinx ML605 User Manual

Summary of ML605

Page 1

User guide [optional] ug534 (v1.2.1) january 21, 2010 [optional] ml605 hardware user guide ug534 (v1.2.1) january 21, 2010

Page 2: Revision History

Ml605 hardware user guide www.Xilinx.Com ug534 (v1.2.1) january 21, 2010 xilinx is disclosing this user guide, manual, release note, and/or specification (the "documentation") to you solely for use in the development of designs to operate with xilinx hardware devices. You may not reproduce, distribu...

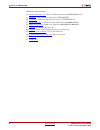

Page 3: Table of Contents

Ml605 hardware user guide www.Xilinx.Com 3 ug534 (v1.2.1) january 21, 2010 preface: about this guide guide contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 additional documentation . . . . . . . . . . . . . . . . ....

Page 4

4 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 fpga_prog_b pushbutton sw4 (active-low) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 sysace_reset_b pushbutton sw3 (active-low) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 system ace cf comp...

Page 5: About This Guide

Ml605 hardware user guide www.Xilinx.Com 5 ug534 (v1.2.1) january 21, 2010 preface about this guide this manual accompanies the virtex®-6 fpga ml605 evaluation board and contains information about the ml605 hardware and software tools. Guide contents this manual contains the following chapters: • ch...

Page 6

6 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 preface: about this guide • virtex-6 fpga memory resources user guide the functionality of the block ram and fifo are described in this user guide. • virtex-6 fpga selectio resources user guide this guide describes the select...

Page 7: Ml605 Evaluation Board

Ml605 hardware user guide www.Xilinx.Com 7 ug534 (v1.2.1) january 21, 2010 chapter 1 ml605 evaluation board overview the ml605 board enables hardware and software developers to create or evaluate designs targeting the virtex®-6 xc6vlx240t-1ffg1156 fpga. The ml605 provides board features common to ma...

Page 8

8 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board features the ml605 provides the following features: • 1. Virtex-6 xc6vlx240t-1ffg1156 fpga • 2. 512 mb ddr3 memory sodimm • 3. 128 mb platform flash xl • 4. 32 mb linear bpi flash • 5. System...

Page 9

Ml605 hardware user guide www.Xilinx.Com 9 ug534 (v1.2.1) january 21, 2010 overview • 16. Status leds ♦ ethernet status ♦ fpga init ♦ fpga done ♦ system ace cf status • 17. User i/o ♦ user led group 1 - gpio (8) ♦ user led group 2 - directional (5) ♦ user pushbuttons - directional (5) ♦ cpu reset pu...

Page 10: Related Xilinx Documents

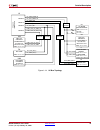

10 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board block diagram figure 1-1 shows a high-level block diagram of the ml605 and its peripherals. Related xilinx documents prior to using the ml605 evaluation board, users should be familiar with ...

Page 11: Detailed Description

Ml605 hardware user guide www.Xilinx.Com 11 ug534 (v1.2.1) january 21, 2010 detailed description detailed description figure 1-2 shows a board photo with numbered features corresponding to table 1-1 and the section headings in this document. The numbered features in figure 1-2 correlate to the featu...

Page 12

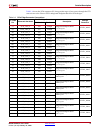

12 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 7 clock generation 200 mhz osc, oscillator socket, sma connectors 30 a. 200 mhz oscillator (on backside) epson 200 mhz 2.5v lvds osc 30 b. Oscillator socket, single- ended mmd components 66 ...

Page 13

Ml605 hardware user guide www.Xilinx.Com 13 ug534 (v1.2.1) january 21, 2010 detailed description 1. Virtex-6 xc6vlx240t-1ffg1156 fpga a virtex-6 xc6vlx240t-1ffg1156 fpga is installed on the embedded development board. Keep-out areas and drill holes are defined around the fpga to support an ironwood ...

Page 14

14 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board the ml605 supports master bpi-up, jtag, and slave selectmap. These are selected by setting m[2:0] options 010, 101 and 110 shown in table 1-2 . For an overview on configuring the fpga, see “...

Page 15

Ml605 hardware user guide www.Xilinx.Com 15 ug534 (v1.2.1) january 21, 2010 detailed description references see the xilinx virtex-6 fpga documentation for more information at http://www.Xilinx.Com/support/documentation/virtex-6.Htm . 2. 512 mb ddr3 memory sodimm a 512mb ddr3 sodimm is provided as a ...

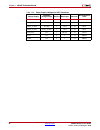

Page 16

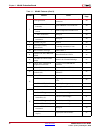

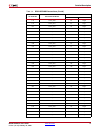

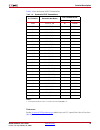

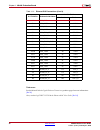

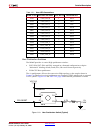

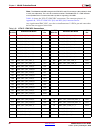

16 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board a15 ddr3_a6 90 a6 b15 ddr3_a7 86 a7 g15 ddr3_a8 89 a8 f15 ddr3_a9 85 a9 m16 ddr3_a10 107 a10/ap m15 ddr3_a11 84 a11 h15 ddr3_a12 83 a12_bc_n j15 ddr3_a13 119 a13 d15 ddr3_a14 80 a14 c15 ddr3...

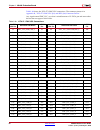

Page 17

Ml605 hardware user guide www.Xilinx.Com 17 ug534 (v1.2.1) january 21, 2010 detailed description g12 ddr3_d20 40 dq20 g13 ddr3_d21 42 dq21 f14 ddr3_d22 50 dq22 h14 ddr3_d23 52 dq23 c19 ddr3_d24 57 dq24 g20 ddr3_d25 59 dq25 e19 ddr3_d26 67 dq26 f20 ddr3_d27 69 dq27 a20 ddr3_d28 56 dq28 a21 ddr3_d29 5...

Page 18

18 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board e24 ddr3_d54 174 dq54 g25 ddr3_d55 176 dq55 f28 ddr3_d56 181 dq56 b31 ddr3_d57 183 dq57 h29 ddr3_d58 191 dq58 h28 ddr3_d59 193 dq59 b30 ddr3_d60 180 dq60 a30 ddr3_d61 182 dq61 e29 ddr3_d62 1...

Page 19

Ml605 hardware user guide www.Xilinx.Com 19 ug534 (v1.2.1) january 21, 2010 detailed description the memory interface generator (mig) tool guidelines specify a set of u1 fpga “no connect” pins. These should be added to the ucf as config prohibit pins as follows: config prohibit = h22; config prohibi...

Page 20

20 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 3. 128 mb platform flash xl a 128 mb xilinx xcf128x-ftg64c platform flash xl device is used with an onboard 47 mhz oscillator (x4) to configure the fpga in less than 100 ms from power valid ...

Page 21

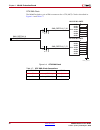

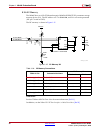

Ml605 hardware user guide www.Xilinx.Com 21 ug534 (v1.2.1) january 21, 2010 detailed description ml605 flash boot options the ml605 has two parallel wired flash memory devices as shown in figure 1-3 . At ml605 power-up, before fpga configuration, dip switch s2 switch 2 selects which flash device, u4...

Page 22

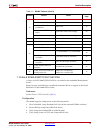

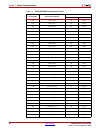

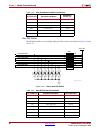

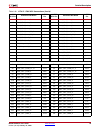

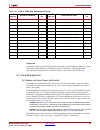

22 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board af24 flash_d0 34 dq0 f2 dq00 af25 flash_d1 36 dq1 e2 dq01 w24 flash_d2 39 dq2 g3 dq02 v24 flash_d3 41 dq3 e4 dq03 h24 flash_d4 47 dq4 e5 dq04 h25 flash_d5 49 dq5 g5 dq05 p24 flash_d6 51 dq6 ...

Page 23

Ml605 hardware user guide www.Xilinx.Com 23 ug534 (v1.2.1) january 21, 2010 detailed description fpga design considerations for the configuration flash after fpga configuration, the fpga design can disable the configuration flash or access the configuration flash to read/write code or data. When the...

Page 24

24 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 5. System ace cf and compactflash connector the xilinx system ace compactflash (cf) configuration controller allows a type i or type ii compactflash card to program the fpga through the jtag...

Page 25

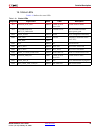

Ml605 hardware user guide www.Xilinx.Com 25 ug534 (v1.2.1) january 21, 2010 detailed description table 1-6 lists the system ace cf connections. References see the system ace cf product page and the system ace compactflash solution data sheet. [ref 18] table 1-6: system ace cf connections u1 fpga pin...

Page 26

26 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 6. Usb jtag jtag configuration is provided through onboard usb-to-jtag configuration logic where a computer host accesses the ml605 jtag chain through a type-a (computer host side) to type-m...

Page 27

Ml605 hardware user guide www.Xilinx.Com 27 ug534 (v1.2.1) january 21, 2010 detailed description the jtag chain can be used to program the fpga and access the fpga for hardware and software debug. The jtag connector (usb mini-b j22) allows a host computer to download bitstreams to the fpga using the...

Page 28

28 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board x-ref target - figure 1-7 figure 1-7: ml605 oscillator socket pin 1 location identifiers silkscreened outline has beveled corner ug534_07_092109 socket has notch in crossbar.

Page 29

Ml605 hardware user guide www.Xilinx.Com 29 ug534 (v1.2.1) january 21, 2010 detailed description sma connectors (differential) a high-precision clock signal can be provided to the fpga using differential clock signals through the onboard 50-ohm sma connectors j58(p)/j55(n). X-ref target - figure 1-8...

Page 30

30 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board gtx sma clock the ml605 includes a pair of sma connectors for a gtx (mgt) clock as described in figure 1-9 and table 1-7 . X-ref target - figure 1-9 figure 1-9: gtx sma clock ug534_09_081309...

Page 31

Ml605 hardware user guide www.Xilinx.Com 31 ug534 (v1.2.1) january 21, 2010 detailed description 8. Multi-gigabit transceivers (gtx mgts) the ml605 provides access to 20 mgts. • eight (8) of the mgts are wired to the pcie x8 endpoint (p1) edge connector fingers • eight (8) of the mgts are wired to t...

Page 32

32 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 9. Pci express endpoint connectivity the 8-lane pcie edge connector performs data transfers at the rate of 2.5 gt/s for a gen1 application and 5.0 gt/s for a gen2 application. The virtex fpg...

Page 33

Ml605 hardware user guide www.Xilinx.Com 33 ug534 (v1.2.1) january 21, 2010 detailed description table 1-8 shows the pcie connector (p1) that provides up to 8-lane access through the gtx transceivers to the virtex-6 fpga integrated endpoint block for pcie designs. Table 1-8: pcie edge connector conn...

Page 34

34 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board the pcie interface obtains its power from the dc power supply provided with the ml605 or through the 12v atx power supply connector. The pcie edge connector is not used for any power connect...

Page 35

Ml605 hardware user guide www.Xilinx.Com 35 ug534 (v1.2.1) january 21, 2010 detailed description references see the following websites for more virtex-6 fpga integrated endpoint block for pci express information: • http://www.Xilinx.Com/products/ipcenter/v6_pci_express_block.Htm • http://www.Xilinx....

Page 36

36 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 11. 10/100/1000 tri-speed ethernet phy the ml605 utilizes the onboard marvell alaska phy device (88e1111) for ethernet communications at 10, 100, or 1000 mb/s. The board supports mii, gmii, ...

Page 37

Ml605 hardware user guide www.Xilinx.Com 37 ug534 (v1.2.1) january 21, 2010 detailed description sgmii gtx transceiver clock generation an integrated circuit systems ics844021i chip generates a high-quality, low-jitter, 125- mhz lvds clock from an inexpensive 25-mhz crystal oscillator. This clock is...

Page 38

38 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board references see the marvell alaska gigabit ethernet transceivers product page for more information. [ref 28] also, see the logicore™ ip tri-mode ethernet mac user guide. [ref 19] am12 phy_rxd...

Page 39

Ml605 hardware user guide www.Xilinx.Com 39 ug534 (v1.2.1) january 21, 2010 detailed description 12. Usb-to-uart bridge the ml605 contains a silicon labs cp2103gm usb-to-uart bridge device (u34) which allows connection to a host computer with a usb cable. The usb cable is supplied in this evaluation...

Page 40

40 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 13. Usb controller the ml605 provides usb support via a cypress cy7c67300 ez-host™ programmable embedded usb host and peripheral controller (u81). The host port is a usb type-a connector (j5...

Page 41

Ml605 hardware user guide www.Xilinx.Com 41 ug534 (v1.2.1) january 21, 2010 detailed description 14. Dvi codec the ml605 features a dvi connector (p3) to support an external video monitor. The dvi circuitry utilizes a chrontel ch7301c (u38) capable of 1600 x 1200 resolution with 24-bit color. The vi...

Page 42

42 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 15. Iic bus the ml605 implements four iic bus interfaces at the fpga. The "main" iic bus hosts four items: • fpga u1 bank 34 "main" iic interface • 8kb nv memory u6 • fmc hpc connector j64 •...

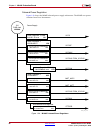

Page 43

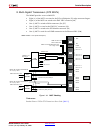

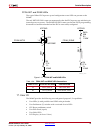

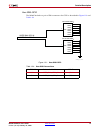

Ml605 hardware user guide www.Xilinx.Com 43 ug534 (v1.2.1) january 21, 2010 detailed description x-ref target - figure 1-14 figure 1-14: iic bus topology u1 j63 p3 u38 bank 34 iic_sda_main_ls iic_scl_main_ls iic_sda_sfp iic_scl_sfp iic_sda_dvi iic_scl_dvi fmc_lpc_iic_sda_ls fmc_lpc_iic_scl_ls fmc_lp...

Page 44

44 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 8 kb nv memory the ml605 hosts an 8 kb st microelectronics m24c08-wdw6tp iic parameter storage memory device (u6). The iic address of u7 is 0b1010100, and u6 is not write protected (wp pin 7...

Page 45

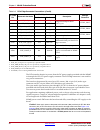

Ml605 hardware user guide www.Xilinx.Com 45 ug534 (v1.2.1) january 21, 2010 detailed description 16. Status leds table 1-19 defines the status leds. Table 1-19: status leds designator signal name color label description ds1 sysace_stat_led green system ace cf status led system ace cf status ds2 ti_p...

Page 46

46 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board ethernet phy status leds the ethernet phy status leds are mounted to be visible when the ml605 board is installed into a pc motherboard. They are mounted in right-angle, plastic housings and...

Page 47

Ml605 hardware user guide www.Xilinx.Com 47 ug534 (v1.2.1) january 21, 2010 detailed description fpga init and done leds the typical xilinx fpga power up and configuration status leds are present on the ml605. The red init led ds31 comes on momentarily after the fpga powers up and during its interna...

Page 48

48 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board user leds the ml605 provides two groups of active-high leds as described in figure 1-18 and table 1-21 . Note: see “user pushbutton switches,” page 49 for more details about the leds. X-ref ...

Page 49

Ml605 hardware user guide www.Xilinx.Com 49 ug534 (v1.2.1) january 21, 2010 detailed description user pushbutton switches the ml605 provides six active-high pushbutton switches: • sw5, sw6, sw7, sw8 and sw9, arranged in a diamond configuration to depict “directional” headings north, south, east, wes...

Page 50

50 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board user dip switch the ml605 includes an active-high eight pole dip switch as described in figure 1-20 and table 1-23 . Table 1-22: user pushbutton switch connections u1 fpga pin schematic net ...

Page 51

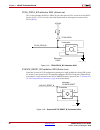

Ml605 hardware user guide www.Xilinx.Com 51 ug534 (v1.2.1) january 21, 2010 detailed description user sma gpio the ml605 includes an pair of sma connectors for gpio as described in figure 1-21 and table 1-24 . X-ref target - figure 1-21 figure 1-21: user sma gpio ug534_21_072109 user sma gpio n j56 ...

Page 52

52 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board lcd display (16 character x 2 lines) the ml605 board has a 16-character x 2-line lcd (display tech s162d ba bc, installed onto j41 2x7 header) on the board to display text information. Poten...

Page 53

Ml605 hardware user guide www.Xilinx.Com 53 ug534 (v1.2.1) january 21, 2010 detailed description 18. Switches the ml605 evaluation board includes the following switches: • power on/off slide switch sw2 • fpga_prog_b sw4 (active-low) • sysace_reset_b sw3 (active-low) • system ace cf compactflash imag...

Page 54

54 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board fpga_prog_b pushbutton sw4 (active-low) this switch grounds the fpga's prog_b pin when pressed. This action clears the fpga. See the virtex-6 fpga data sheet for more information on clearing...

Page 55

Ml605 hardware user guide www.Xilinx.Com 55 ug534 (v1.2.1) january 21, 2010 detailed description system ace cf compactflash image select dip switch s1 system ace cf compactflash (cf) image select dip switch s1, switches 1–3, select which cf resident bitstream image is downloaded to the fpga ( figure...

Page 56

56 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board mode, osc enable, boot eeprom select, and addr select dip switch s2 dip switch s2 is a multi-purpose selector switch ( figure 1-27 and table 1-27, page 57 ). Fpga mode: s2 switches 3, 4, and...

Page 57

Ml605 hardware user guide www.Xilinx.Com 57 ug534 (v1.2.1) january 21, 2010 detailed description see “3. 128 mb platform flash xl,” page 20 and “4. 32 mb linear bpi flash,” page 20 for details. 19. Vita 57.1 fmc hpc connector the ml605 implements both the high pin count (hpc, j64) and low pin count ...

Page 58

58 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board note: the ml605 board vadj voltage for the fmc hpc and lpc connectors (j64 and j63) is fixed at 2.5v (non-adjustable). The 2.5v rail cannot be turned off. The ml605 vita 57.1 fmc interfaces ...

Page 59

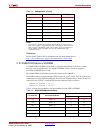

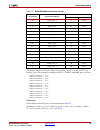

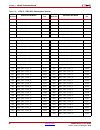

Ml605 hardware user guide www.Xilinx.Com 59 ug534 (v1.2.1) january 21, 2010 detailed description c14 fmc_hpc_la10_p am20 d14 fmc_hpc_la09_p am18 c15 fmc_hpc_la10_n al20 d15 fmc_hpc_la09_n al18 c18 fmc_hpc_la14_p an19 d17 fmc_hpc_la13_p ap19 c19 fmc_hpc_la14_n an20 d18 fmc_hpc_la13_n an18 c22 fmc_hpc...

Page 60

60 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board e28 fmc_hpc_hb09_n ak34 f28 fmc_hpc_hb08_p ak33 e30 fmc_hpc_hb13_p ah33 f29 fmc_hpc_hb08_n ak32 e31 fmc_hpc_hb13_n ah32 f31 fmc_hpc_hb12_p aj31 e33 fmc_hpc_hb19_p al31 f32 fmc_hpc_hb12_n aj3...

Page 61

Ml605 hardware user guide www.Xilinx.Com 61 ug534 (v1.2.1) january 21, 2010 detailed description j2 fmc_hpc_clk3_m2c_p (2) u84.6 k4 fmc_hpc_clk2_m2c_p (2) u83.6 j3 fmc_hpc_clk3_m2c_n (2) u84.7 k5 fmc_hpc_clk2_m2c_n (2) u83.7 j6 fmc_hpc_ha03_p aa25 k7 fmc_hpc_ha02_p ab25 j7 fmc_hpc_ha03_n y26 k8 fmc_...

Page 62

62 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board table 1-29: power supply voltages for hpc connector voltage supply allowable voltage range no pins max amps tolerance max capacitive load vadj fixed 2.5v 4 4 +/- 5% 1000 uf vio_b_m2c 0-vadj ...

Page 63

Ml605 hardware user guide www.Xilinx.Com 63 ug534 (v1.2.1) january 21, 2010 detailed description 20. Vita 57.1 fmc lpc connector the ml605 implements both the high pin count (hpc, j64) and low pin count (lpc, j63) connector options of vita 57.1.1 fmc specification. This section discusses the fmc lpc...

Page 64

64 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board table 1-30 shows the vita 57.1 fmc lpc connections. The connector pinout is in appendix b, “vita 57.1 fmc lpc (j63) and hpc (j64) connector pinout.” any signal named fmc_lpc_xxxx that is wir...

Page 65

Ml605 hardware user guide www.Xilinx.Com 65 ug534 (v1.2.1) january 21, 2010 detailed description references see the data sheet for the rohs compliant fmc hpc samtec searay connector (carrier side socket asp-134486-01; module side plug asp-134488-01), and the high-speed characterization report for th...

Page 66

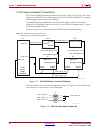

66 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board onboard power regulation figure 1-28 shows the ml605 onboard power supply architecture. The ml605 uses power solutions from texas instruments. X-ref target - figure 1-28 figure 1-28: ml605 o...

Page 67

Ml605 hardware user guide www.Xilinx.Com 67 ug534 (v1.2.1) january 21, 2010 detailed description voltage and current monitoring and control are available for selected power rails through texas instruments’ fusion digital power™ graphical user interface (gui). Both onboard ti power controllers are wi...

Page 68

68 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board 22. System monitor the system monitor provides information regarding the fpga on-chip temperature and power supply conditions via jtag and an internal fpga interface. The system monitor can ...

Page 69

Ml605 hardware user guide www.Xilinx.Com 69 ug534 (v1.2.1) january 21, 2010 detailed description system monitor header (j35) figure 1-30 shows the pinout for the system monitor 12-pin header. The header provides user access to the analog power supply (a vdd ) and the 1.25v reference shown in figure ...

Page 70

70 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board ml605 board power monitor in addition to monitoring the fpga core supply power consumption, two auxiliary analog input channels (of the 16 that are available) are used to implement a power m...

Page 71

Ml605 hardware user guide www.Xilinx.Com 71 ug534 (v1.2.1) january 21, 2010 detailed description fan controller in highly demanding situations, active thermal management in the form of a heat sink and fan may be required. In order to support this, drive circuitry for an external fan has been provide...

Page 72

72 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board fpga power supply margining the pmbus (iic), which provides access to the 2 x udc9240 power controllers, can also be accessed via fpga i/o in addition to a dedicated header (j3), see figure ...

Page 73: Configuration Options

Ml605 hardware user guide www.Xilinx.Com 73 ug534 (v1.2.1) january 21, 2010 configuration options configuration options the fpga on the ml605 evaluation board can be configured by the following methods: • “3. 128 mb platform flash xl,” page 20 • “4. 32 mb linear bpi flash,” page 20 • “5. System ace ...

Page 74

74 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 chapter 1: ml605 evaluation board.

Page 75

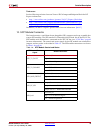

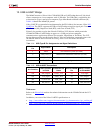

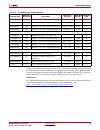

Ml605 hardware user guide www.Xilinx.Com 75 ug534 (v1.2.1) january 21, 2010 appendix a default switch and jumper settings table a-1: default switch settings refdes function/type default sw2 board power slide-switch off sw1 user gpio 8-pole dip switch 8 off 7 off 6 off 5 off 4 off 3 off 2 off 1 off s...

Page 76

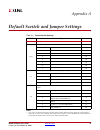

76 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix a: default switch and jumper settings table a-2: default jumper settings jumper refdes function default j69 system ace cf error led enable jump 1-2 gmii: j66 pins 1-2: gmii/mii to cu pins 2-3: sgmii to cu, no clk ju...

Page 77: Connector Pinout

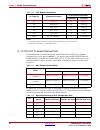

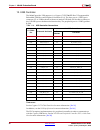

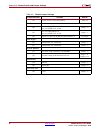

Ml605 hardware user guide www.Xilinx.Com 77 ug534 (v1.2.1) january 21, 2010 appendix b vita 57.1 fmc lpc (j63) and hpc (j64) connector pinout figure b-1 shows the pinout of the fmc lpc connector. Pins marked nc are not connected. X-ref target - figure b-1 figure b-1: fmc lpc connector pinout k j h g...

Page 78

78 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix b: vita 57.1 fmc lpc (j63) and hpc (j64) connector pinout figure b-2 shows the pinout of the fmc hpc connector. X-ref target - figure b-2 figure b-2: fmc hpc connector pinout kjh g f e d c b a 1 vr ef _b _m 2c gn d ...

Page 79: Ml605 Master Ucf

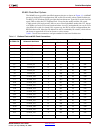

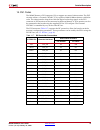

Ml605 hardware user guide www.Xilinx.Com 79 ug534 (v1.2.1) january 21, 2010 appendix c ml605 master ucf the ucf template is provided for designs that target the ml605. Net names provided in the constraints below correlate with net names on the ml605 rev. D schematic. On identifying the appropriate p...

Page 80

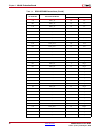

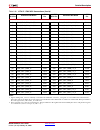

80 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix c: ml605 master ucf net "ddr3_d8" loc = "m13"; ## 21 on j1 net "ddr3_d9" loc = "j14"; ## 23 on j1 net "ddr3_d10" loc = "b13"; ## 33 on j1 net "ddr3_d11" loc = "b12"; ## 35 on j1 net "ddr3_d12" loc = "g10"; ## 22 on ...

Page 81

Ml605 hardware user guide www.Xilinx.Com 81 ug534 (v1.2.1) january 21, 2010 net "ddr3_dqs0_p" loc = "d12"; ## 12 on j1 net "ddr3_dqs1_n" loc = "j12"; ## 27 on j1 net "ddr3_dqs1_p" loc = "h12"; ## 29 on j1 net "ddr3_dqs2_n" loc = "a14"; ## 45 on j1 net "ddr3_dqs2_p" loc = "a13"; ## 47 on j1 net "ddr3...

Page 82

82 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix c: ml605 master ucf net "flash_a21" loc = "af9"; ## 10 on u4, a8 on u27 net "flash_a22" loc = "al9"; ## 9 on u4, g1 on u27 net "flash_a23" loc = "aa23"; ## 26 on u4 net "flash_d0" loc = "af24"; ## 34 on u4 (thru ser...

Page 83

Ml605 hardware user guide www.Xilinx.Com 83 ug534 (v1.2.1) january 21, 2010 net "fmc_hpc_dp6_m2c_n" loc = "am6"; ## b17 on j64 net "fmc_hpc_dp6_m2c_p" loc = "am5"; ## b16 on j64 net "fmc_hpc_dp7_c2m_n" loc = "ap2"; ## b33 on j64 net "fmc_hpc_dp7_c2m_p" loc = "ap1"; ## b32 on j64 net "fmc_hpc_dp7_m2c...

Page 84

84 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix c: ml605 master ucf net "fmc_hpc_hb03_p" loc = "al30"; ## e21 on j64 net "fmc_hpc_hb04_n" loc = "al33"; ## f26 on j64 net "fmc_hpc_hb04_p" loc = "am33"; ## f25 on j64 net "fmc_hpc_hb05_n" loc = "an34"; ## e25 on j64...

Page 85

Ml605 hardware user guide www.Xilinx.Com 85 ug534 (v1.2.1) january 21, 2010 net "fmc_hpc_la16_n" loc = "an23"; ## g19 on j64 net "fmc_hpc_la16_p" loc = "ap22"; ## g18 on j64 net "fmc_hpc_la17_cc_n" loc = "am27"; ## d21 on j64 net "fmc_hpc_la17_cc_p" loc = "an27"; ## d20 on j64 net "fmc_hpc_la18_cc_n...

Page 86

86 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix c: ml605 master ucf net "fmc_lpc_la07_n" loc = "h32"; ## h14 on j63 net "fmc_lpc_la07_p" loc = "g32"; ## h13 on j63 net "fmc_lpc_la08_n" loc = "k29"; ## g13 on j63 net "fmc_lpc_la08_p" loc = "j30"; ## g12 on j63 net...

Page 87

Ml605 hardware user guide www.Xilinx.Com 87 ug534 (v1.2.1) january 21, 2010 net "fpga_m0" loc = "u8"; ## 3 on s2 dip switch (active-high) net "fpga_m1" loc = "w8"; ## 4 on s2 dip switch (active-high) net "fpga_m2" loc = "v8"; ## 4 on s2 dip switch (active-high) net "fpga_prog_b" loc = "l8"; ## 1 on ...

Page 88

88 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix c: ml605 master ucf net "pcie_rx2_n" loc = "l4"; ## b24 on p1 net "pcie_rx2_p" loc = "l3"; ## b23 on p1 net "pcie_rx3_n" loc = "n4"; ## b28 on p1 net "pcie_rx3_p" loc = "n3"; ## b27 on p1 net "pcie_rx4_n" loc = "r4"...

Page 89

Ml605 hardware user guide www.Xilinx.Com 89 ug534 (v1.2.1) january 21, 2010 net "pmbus_data_ls" loc = "ab10"; ## 2 on q17 ## net "sfp_los" loc = "v23"; ## 8 on p4 net "sfp_rx_n" loc = "e4"; ## 12 on p4 net "sfp_rx_p" loc = "e3"; ## 13 on p4 net "sfp_tx_disable_fpga" loc = "ap12"; ## 1 on q22 net "sf...

Page 90

90 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix c: ml605 master ucf net "usb_d6_ls" loc = "v27"; ## 2 on u31 net "usb_d7_ls" loc = "u25"; ## 12 on u30 net "usb_d8_ls" loc = "y28"; ## 14 on u29 net "usb_d9_ls" loc = "w32"; ## 8 on u29 net "usb_d10_ls" loc = "w31";...

Page 91: References

Ml605 hardware user guide www.Xilinx.Com 91 ug534 (v1.2.1) january 21, 2010 appendix d references this section provides references to documentation supporting virtex-6 fpgas, tools, and ip. For additional information, see www.Xilinx.Com/support/documentation/index.Htm . Documents supporting the ml60...

Page 92

92 www.Xilinx.Com ml605 hardware user guide ug534 (v1.2.1) january 21, 2010 appendix d: references additional documentation: 22. Micron technology, inc. , ddr3 sodimm specification (mt4jsf6464hy-1g1) 23. Winbond , serial flash memory data sheet ( w25q64vsfig) 24. Numonyx , embedded flash memory data...