[guide subtitle] [optional] ug518 (v1.1) august 19, 2009 [optional] sp601 hardware user guide ug518 (v1.1) august 19, 2009.

Sp601 hardware user guide www.Xilinx.Com ug518 (v1.1) august 19, 2009 xilinx is disclosing this user guide, manual, release note, and/or specification (the "documentation") to you solely for use in the development of designs to operate with xilinx hardware devices. You may not reproduce, distribute,...

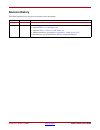

Ug518 (v1.1) august 19, 2009 www.Xilinx.Com sp601 hardware user guide revision history the following table shows the revision history for this document. Date version revision 07/15/2009 1.0 initial xilinx release. 08/19/2009 1.1 • added appendix c, “vita 57.1 fmc connections.” • updated figure 1-18 ...

Sp601 hardware user guide www.Xilinx.Com ug518 (v1.1) august 19, 2009.

Sp601 hardware user guide www.Xilinx.Com 5 ug518 (v1.1) august 19, 2009 preface: about this guide guide contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 additional resources . . . . . . . . . . . . . . . . . . . . ...

6 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 appendix a: references appendix b: default jumper and switch settings appendix c: vita 57.1 fmc connections appendix d: sp601 master ucf.

Sp601 hardware user guide www.Xilinx.Com 7 ug518 (v1.1) august 19, 2009 preface about this guide this manual accompanies the spartan®-6 fpga sp601 evaluation board and contains information about the sp601 hardware and software tools. Guide contents this manual contains the following chapters: • chap...

8 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 preface: about this guide online document the following conventions are used in this document: italic font variables in a syntax statement for which you must supply values ngdbuild design_name references to other manuals see the...

Sp601 hardware user guide www.Xilinx.Com 9 ug518 (v1.1) august 19, 2009 chapter 1 sp601 evaluation board overview the sp601 board enables hardware and software developers to create or evaluate designs targeting the spartan®-6 xc6slx16-2csg324 fpga. The sp601 provides board features for evaluating th...

10 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board features the sp601 board provides the following features: • 1. Spartan-6 xc6slx16-2csg324 fpga • 2. 128 mb ddr2 component memory • 3. Spi x4 flash • 4. Linear flash bpi • 5. 10/100/1000 tri-spe...

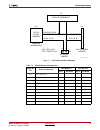

Sp601 hardware user guide www.Xilinx.Com 11 ug518 (v1.1) august 19, 2009 related xilinx documents block diagram figure 1-1 shows a high-level block diagram of the sp601 and its peripherals. Related xilinx documents prior to using the sp601 evaluation board, users should be familiar with xilinx resou...

12 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board detailed description figure 1-2 shows a board photo with numbered features corresponding to table 1-1 and the section headings in this document. The numbered features in figure 1-2 correlate to...

Sp601 hardware user guide www.Xilinx.Com 13 ug518 (v1.1) august 19, 2009 detailed description 1. Spartan-6 xc6slx16-2csg 3 24 fpga a xilinx spartan-6 xc6slx16-2csg324 fpga is installed on the embedded development board. Configuration the sp601 supports configuration in the following modes: • master ...

14 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board references see the xilinx spartan-6 fpga documentation for more information at http://www.Xilinx.Com/support/documentation/spartan-6.Htm . 2. 128 mb ddr2 component memory there are 128 mb of dd...

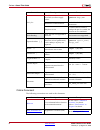

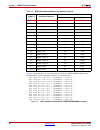

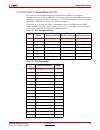

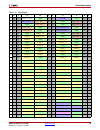

Sp601 hardware user guide www.Xilinx.Com 15 ug518 (v1.1) august 19, 2009 detailed description table 1-5 shows the connections and pin numbers for the ddr2 component memory. Table 1-5: ddr2 component memory connections fpga u1 schematic netname memory u2 pin number name j7 ddr2_a0 m8 a0 j6 ddr2_a1 m3...

16 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board figure 1-3 provides the user constraints file (ucf) for the ddr2 sdram address pins, including the i/o pin assignment and the i/o standard used. F2 ddr2_ba0 l2 ba0 f1 ddr2_ba1 l3 ba1 e1 ddr2_ba...

Sp601 hardware user guide www.Xilinx.Com 17 ug518 (v1.1) august 19, 2009 detailed description figure 1-4 provides the ucf constraints for the ddr2 sdram data pins, including the i/o pin assignment and i/o standard used. Figure 1-5 provides the ucf constraints for the ddr2 sdram control pins, includi...

18 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board 3 . Spi x4 flash the xilinx spartan-6 fpga hosts a spi interface which is visible to the xilinx impact configuration tool. The spi memory device operates at 3.0v; the spartan-6 fpga i/os are 3....

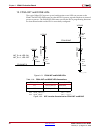

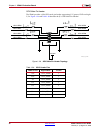

Sp601 hardware user guide www.Xilinx.Com 19 ug518 (v1.1) august 19, 2009 detailed description x-ref target - figure 1-7 figure 1-7: spi flash interface topology table 1-6: spi x4 memory connections fpga u1 pin schematic netname spi mem u17 spi hdr j12 pin # pin name pin # pin name v2 fpga_prog_b 1 v...

20 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board figure 1-8 provides the ucf constraints for the spi serial flash prom. References see the winbond serial flash specifications for more information at http://www.Winbond- usa.Com/hq/enu/producta...

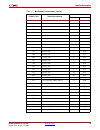

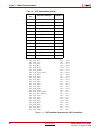

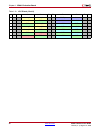

Sp601 hardware user guide www.Xilinx.Com 21 ug518 (v1.1) august 19, 2009 detailed description h16 flash_a6 23 a6 h15 flash_a7 22 a7 h14 flash_a8 20 a8 h13 flash_a9 19 a9 f18 flash_a10 18 a10 f17 flash_a11 17 a11 k13 flash_a12 13 a12 k12 flash_a13 12 a13 e18 flash_a14 11 a14 e16 flash_a15 10 a15 g13 ...

22 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board note: memory u10 pin 56 address a24 is not connected on the 16 mb device. It is made available for larger density devices. References see the numonyx flash memory specifications for more inform...

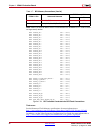

Sp601 hardware user guide www.Xilinx.Com 23 ug518 (v1.1) august 19, 2009 detailed description 5. 10/100/1000 tri-speed ethernet phy the sp601 uses the onboard marvell alaska phy device (88e1111) for ethernet communications at 10, 100, or 1000 mb/s. The board supports a gmii/mii interface from the fp...

24 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board p18 phy_rxd7 120 a9 phy_txc_gtxclk 14 b9 phy_txclk 10 a8 phy_txer 13 b8 phy_txctl_txen 16 f8 phy_txd0 18 g8 phy_txd1 19 a6 phy_txd2 20 b6 phy_txd3 24 e6 phy_txd4 25 f7 phy_txd5 26 a5 phy_txd6 2...

Sp601 hardware user guide www.Xilinx.Com 25 ug518 (v1.1) august 19, 2009 detailed description references see the marvell alaska gigabit ethernet transceiver product page for more information at http://www.Marvell.Com/products/transceivers/alaska_gigabit/index.Jsp . Also, see the xilinx tri-mode ethe...

26 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board references technical information on the silicon labs cp2103gm and the vcp drivers can be found on their website at https://www.Silabs.Com/pages/default.Aspx . In addition, see some of the xilin...

Sp601 hardware user guide www.Xilinx.Com 27 ug518 (v1.1) august 19, 2009 detailed description 8-kb nv memory the sp601 hosts a 8-kb st microelectronics m24c08-wdw6tp iic parameter storage memory device (u7). The iic address of u7 is 0b1010100, and u7 is not write protected (wp pin 7 is tied to gnd)....

28 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board oscillator socket (single-ended, 2.5v or 3 . 3 v) one populated single-ended clock socket (x2) is provided for user applications. The option of 3.3v or 2.5v power may be selected via a 0 ohm re...

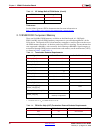

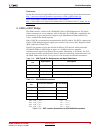

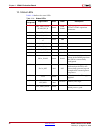

Sp601 hardware user guide www.Xilinx.Com 29 ug518 (v1.1) august 19, 2009 detailed description table 1-13: lpc pinout k j h g f e d c b a 1 nc nc vref_a_m2c gnd nc nc pg_c2m gnd nc nc 2 nc nc prsnt_m2c_l clk1_m2c_p nc nc gnd dp0_c2m_p nc nc 3 nc nc gnd clk1_m2c_n nc nc gnd dp0_c2m_n nc nc 4 nc nc clk...

30 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board 34 nc nc la30_p la31_n nc nc trst_l ga0 nc nc 35 nc nc la30_n gnd nc nc ga1 12p0v nc nc 36 nc nc gnd la33_p nc nc 3p3v gnd nc nc 37 nc nc la32_p la33_n nc nc gnd 12p0v nc nc 38 nc nc la32_n gnd...

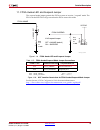

Sp601 hardware user guide www.Xilinx.Com 31 ug518 (v1.1) august 19, 2009 detailed description x-ref target - figure 1-18 net "fmc_clk0_m2c_n" loc = "a10"; net "fmc_clk0_m2c_p" loc = "c10"; net "fmc_clk1_m2c_n" loc = "v9"; net "fmc_clk1_m2c_p" loc = "t9"; net "fmc_la00_cc_n" loc = "c9"; net "fmc_la00...

32 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board 10. Status leds table 1-14 defines the status leds. Table 1-14: status leds reference designator signal name color label description ds1 fmc_pwr_good_ flash_rst_b green pwr good indicates power...

Sp601 hardware user guide www.Xilinx.Com 33 ug518 (v1.1) august 19, 2009 detailed description 11. Fpga awake led and suspend jumper the suspend mode jumper permits the fpga to enter an inactive, "suspend" mode. The fpga awake led ds8 will go out when the fpga enters this mode. See the spartan-6 fpga...

34 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board 12. Fpga init and done leds the typical xilinx fpga power up and configuration status leds are present on the sp601. The init led ds10 comes on after the fpga powers up and completes its intern...

Sp601 hardware user guide www.Xilinx.Com 35 ug518 (v1.1) august 19, 2009 detailed description 1 3 . User i/o the sp601 provides the following user and general purpose i/o capabilities: • user leds • user dip switch • pushbutton switches • cpu reset pushbutton switch • gpio male pin header note: all ...

36 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board user dip switch the sp601 includes an active high four pole dip switch, as described in figure 1-24 and table 1-18 . Ds13 gpio_led_2 green c4 ds14 gpio_led_3 green a4 table 1-17: user leds (con...

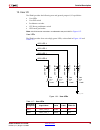

Sp601 hardware user guide www.Xilinx.Com 37 ug518 (v1.1) august 19, 2009 detailed description user pushbutton switches the sp601 provides five active high pushbutton switches: sw6, sw4, sw5, sw7 and sw9. The five pushbuttons all have the same topology as the sample shown in figure 1-25 . Four pushbu...

38 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board gpio male pin header the sp601 provides a 2x6 gpio male pin header supporting 3.3v power, gnd and eight i/os. Figure 1-26 and table 1-20 describe the j13 gpio male pin header. X-ref target - fi...

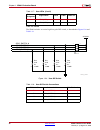

Sp601 hardware user guide www.Xilinx.Com 39 ug518 (v1.1) august 19, 2009 detailed description x-ref target - figure 1-27 net "gpio_led_0" loc = "e13"; net "gpio_led_1" loc = "c14"; net "gpio_led_2" loc = "c4"; net "gpio_led_3" loc = "a4"; net "gpio_switch_0" loc = "d14"; net "gpio_switch_1" loc = "e...

40 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board 14. Fpga_prog_b pushbutton switch the sp601 provides one dedicated, active low fpga_prog_b pushbutton switch, as shown in figure 1-28 . Power management ac adapter and 5v input power jack/switc...

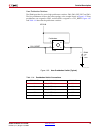

Sp601 hardware user guide www.Xilinx.Com 41 ug518 (v1.1) august 19, 2009 power management the sp601 uses power solutions from ltc. An estimate of the current draw on the various power supply rails is shown in table 1-22 . X-ref target - figure 1- 3 0 figure 1-30: power supply 5v pwr j a ck d ua l s ...

42 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board configuration options the fpga on the sp601 evaluation board can be configured by the following methods: • “3. Spi x4 flash,” page 18 • “4. Linear flash bpi,” page 20 • “jtag configuration,” pa...

Sp601 hardware user guide www.Xilinx.Com 43 ug518 (v1.1) august 19, 2009 configuration options the jtag chain can be used to program the fpga and access the fpga for hardware and software debug. The jtag connector (usb mini-b j10) allows a host computer to download bitstreams to the fpga using the i...

44 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 chapter 1: sp601 evaluation board.

Sp601 hardware user guide www.Xilinx.Com 45 ug518 (v1.1) august 19, 2009 appendix a references this section provides references to documentation supporting spartan-6 fpgas, tools, and ip. For additional information, see www.Xilinx.Com/support/documentation/index.Htm . Documents supporting the sp601 ...

46 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 appendix a: references.

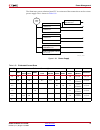

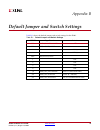

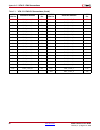

Sp601 hardware user guide www.Xilinx.Com 47 ug518 (v1.1) august 19, 2009 appendix b default jumper and switch settings table b-1 shows the default jumper and switch settings for the sp601. Table b-1: default jumper and switch settings refdes type/function default sw1 slide, power on-off off sw2 dip,...

48 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 appendix b: default jumper and switch settings.

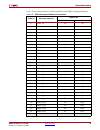

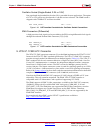

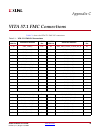

Sp601 hardware user guide www.Xilinx.Com 49 ug518 (v1.1) august 19, 2009 appendix c vita 57.1 fmc connections table c-1 shows the vita 57.1 fmc lpc connections. Table c-1: vita 57.1 fmc lpc connections j1 fmc lpc pin schematic netname u1 fpga pin j1 fmc lpc pin schematic netname u1 fpga pin c10 fmc_...

50 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 appendix c: vita 57.1 fmc connections g13 fmc_la08_n e11 h13 fmc_la07_p e7 g15 fmc_la12_p d6 h14 fmc_la07_n e8 g16 fmc_la12_n c6 h16 fmc_la11_p b12 g18 fmc_la16_p c7 h17 fmc_la11_n a12 g19 fmc_la16_n a7 h19 fmc_la15_p g9 g21 fm...

Sp601 hardware user guide www.Xilinx.Com 51 ug518 (v1.1) august 19, 2009 appendix d sp601 master ucf the ucf template is provided for designs that target the sp601. Net names provided in the constraints below correlate with net names on the sp601 rev. C schematic. On identifying the appropriate pins...

52 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 appendix d: sp601 master ucf net "ddr2_ldqs_p" loc = "l4"; net "ddr2_odt" loc = "k6"; net "ddr2_ras_b" loc = "l5"; net "ddr2_udm" loc = "k4"; net "ddr2_udqs_n" loc = "p1"; net "ddr2_udqs_p" loc = "p2"; net "ddr2_we_b" loc = "e3...

Sp601 hardware user guide www.Xilinx.Com 53 ug518 (v1.1) august 19, 2009 net "fmc_la07_p" loc = "e7"; net "fmc_la08_n" loc = "e11"; net "fmc_la08_p" loc = "f11"; net "fmc_la09_n" loc = "f10"; net "fmc_la09_p" loc = "g11"; net "fmc_la10_n" loc = "c8"; net "fmc_la10_p" loc = "d8"; net "fmc_la11_n" loc...

54 www.Xilinx.Com sp601 hardware user guide ug518 (v1.1) august 19, 2009 appendix d: sp601 master ucf net "fpga_cmp_mosi" loc = "v16"; net "fpga_d0_din_miso_miso1" loc = "r13"; net "fpga_d1_miso2" loc = "t14"; net "fpga_d2_miso3" loc = "v14"; net "fpga_done" loc = "v17"; net "fpga_hswapen" loc = "d4...

Sp601 hardware user guide www.Xilinx.Com 55 ug518 (v1.1) august 19, 2009 net "phy_txctl_txen" loc = "b8"; net "phy_txc_gtxclk" loc = "a9"; net "phy_txd0" loc = "f8"; net "phy_txd1" loc = "g8"; net "phy_txd2" loc = "a6"; net "phy_txd3" loc = "b6"; net "phy_txd4" loc = "e6"; net "phy_txd5" loc = "f7";...