- DL manuals

- Xilinx

- Microcontrollers

- VCU1525

- User manual

Xilinx VCU1525 User manual

Summary of VCU1525

Page 1

Vcu1525 reconfigurable acceleration platform user guide ug1268 (v1.0) november 13, 2017.

Page 2: Revision History

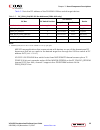

Vcu1525 acceleration platform user guide 2 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com revision history the following table shows the revision history for this document. Date version revision 11/13/2017 1.0 initial xilinx release. Send feedback.

Page 3

Vcu1525 acceleration platform user guide 3 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com table of contents revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 chapter 1: introduction overview . . ...

Page 4

Vcu1525 acceleration platform user guide 4 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com board management controller voltage measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44 vccint regulator circuit . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5: Overview

Vcu1525 acceleration platform user guide 5 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 1 introduction overview the vcu1525 reconfigurable acceleration platform is a peripheral component interconnect express (pcie®) gen3 x16 compliant board featuring the xilinx® virtex® ultrascale+™ xcvu9p...

Page 6

Vcu1525 acceleration platform user guide 6 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 1: introduction figure 1-2 shows the vcu1525 passive cooling configuration (data center server applications). Caution! The vcu1525 board with passive cooling is designed to be installed into a data cent...

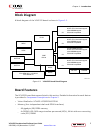

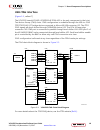

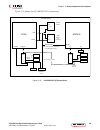

Page 7: Block Diagram

Vcu1525 acceleration platform user guide 7 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 1: introduction block diagram a block diagram of the vcu1525 board is shown in figure 1-3 . Board features the vcu1525 board features are listed in this section. Detailed information for each feature is...

Page 8

Vcu1525 acceleration platform user guide 8 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 1: introduction ° x4/x8 unregistered dual inline memory module (udimm) support • configuration options ° 1 gigabit (gb) quad serial peripheral interface (spi) flash memory ° micro-ab universal serial bu...

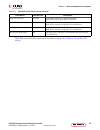

Page 9: Board Specifications

Vcu1525 acceleration platform user guide 9 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 1: introduction board specifications dimensions height: 4.2 inch (10.67 cm) thickness (±5%): 0.062 inch (0.157 cm) length: 9.13 inch (23.19 cm) note: a 3d model of this board is not available. Environme...

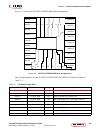

Page 10: Board Component Location

Vcu1525 acceleration platform user guide 10 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 2 board setup and configuration board component location figure 2-1 shows the location of components on the vcu1525 board. Each component shown is keyed to table 2-1 . Table 2-1 identifies the componen...

Page 11

Vcu1525 acceleration platform user guide 11 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 2: board setup and configuration caution! The vcu1525 board can be damaged by electrostatic discharge (esd). Follow standard esd prevention measures when handling the board. Table 2-1: vcu1525 board co...

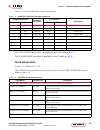

Page 12: Default Switch Settings

Vcu1525 acceleration platform user guide 12 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 2: board setup and configuration default switch settings default switch settings are listed in table 2-2 . Switch locations are shown in figure 2-1 . Table 2-3 shows other visible switch locations. Ins...

Page 13

Vcu1525 acceleration platform user guide 13 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 2: board setup and configuration at power up, the fpga is configured by the quad spi nor flash u17 device (micron mt25qu01gbba8e12-0sit) with the fpga_cclk operating at clock rate of 105 mhz (emcclk) u...

Page 14

Vcu1525 acceleration platform user guide 14 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 2: board setup and configuration the configuration circuit is shown in figure 2-2 . X-ref target - figure 2-2 figure 2-2: vcu1525 configuration circuit x19973-103017 send feedback.

Page 15: Overview

Vcu1525 acceleration platform user guide 15 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3 board component descriptions overview this chapter provides a detailed functional description of board components and features. Table 2-1 identifies the components, references the respective schemati...

Page 16

Vcu1525 acceleration platform user guide 16 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions figure 3-1 shows the xcvu9p-l2fsgd2104e bank arrangement. The voltages applied to the xcvu9p-l2fsgd2104e u13 fpga i/o banks are listed in table 3-1 . X-ref target - figu...

Page 17: Ddr4 Dimm Memory

Vcu1525 acceleration platform user guide 17 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions ddr4 dimm memory [ figure 2-1 , callout 2, 3, 4, 5] four independent dual-rank ddr4 interfaces are available on the vcu1525 board. The vcu1525 board is populated with fo...

Page 18

Vcu1525 acceleration platform user guide 18 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the default selected (bank 0 configuration) quad spi flash memory is u17. Each quad spi device provides 1 gb of nonvolatile storage. • part number: mt25qu01gbb8e12-0sit ...

Page 19: Usb Jtag Interface

Vcu1525 acceleration platform user guide 19 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions usb jtag interface [ figure 2-1 , callout 7] the vcu1525 board xcvu9p-l2fsgd2104e fpga u13 is the only component in the joint test action group (jtag) chain. Jtag config...

Page 20: Ft4232Hq Usb-Uart Interface

Vcu1525 acceleration platform user guide 20 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions ft4232hq usb-uart interface [ figure 2-1 , callout 7] the ft4232hq u27 quad usb-uart on the vcu1525 board provides two uart connections through the single micro-ab usb c...

Page 21

Vcu1525 acceleration platform user guide 21 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the channel bd uart connection from xcvu9p-l2fsgd2104e u13 bank 64 to the ft4232hq u27 device is level-shifted via q36 (tx) and q37 (rx). Table 3-2 shows the two uart ch...

Page 22: Clock Generation

Vcu1525 acceleration platform user guide 22 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions table 3-3 lists the usb switch circuit connections. The ftdi ft4232hq data sheet is available on the ftdi website [ref 6] . The ts3usb221rser data sheet is available on ...

Page 23

Vcu1525 acceleration platform user guide 23 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the fpga connections for each clock are listed in appendix a, master constraints file listing . User_si570_clock u43 (q0) silicon labs si53340 3.3v lvds clock buffer. Us...

Page 24

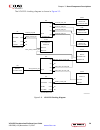

Vcu1525 acceleration platform user guide 24 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the vcu1525 clocking diagram is shown in figure 3-3 . X-ref target - figure 3-6 figure 3-6: vcu1525 clocking diagram u9 u44 bank 63 ddr4 c0 i/f ay37/ay38 gc qbc u13af xc...

Page 25: System Clock and Qsfp0 Clock

Vcu1525 acceleration platform user guide 25 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions system clock and qsfp0 clock [ figure 2-1 , callout 10] the system clock source is a silicon labs si5335a quad clock generator/buffer (u9). • clock generator: silicon la...

Page 26

Vcu1525 acceleration platform user guide 26 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the system and qsfp0 clock source si5335a u9 is shown in figure 3-6 . The 300 mhz clock buffer si53340 u44 is shown in figure 3-7 . X-ref target - figure 3-7 figure 3-7:...

Page 27: Qsfp1 Clock

Vcu1525 acceleration platform user guide 27 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions qsfp1 clock [ figure 2-1 , callout 11] the qsfp1 clock source is a silicon labs si5335a quad clock generator/buffer (u12). • clock generator: silicon labs si5335a-b06201...

Page 28

Vcu1525 acceleration platform user guide 28 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the qsfp1 si5335a u12 clock circuit is shown in figure 3-8 . Programmable mgt and user clock [ figure 2-1 , callout 12] the vcu1525 board has an si570 programmable low-j...

Page 29: Gty Transceivers

Vcu1525 acceleration platform user guide 29 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions three of the si53340 (u14) 1-to-4 lvds clock buffer outputs are used: • q0_p/n: user_si570_clock_p/n are wired to gpio and qsfp0/1 control i/o bank 64 gc input pins au19...

Page 30

Vcu1525 acceleration platform user guide 30 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions • four gty transceivers (bank 227) are wired to pcie edge connector cn1 lanes 3:0. The gty transceivers in the xcvu9p-l2fsgd2104e are grouped into four channels or quads...

Page 31

Vcu1525 acceleration platform user guide 31 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions figure 3-10 shows the gty assignments. The fpga connections for each quad are listed in appendix a, master constraints file listing . Pci express endpoint connectivity [...

Page 32

Vcu1525 acceleration platform user guide 32 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the xcvu9p-l2fsgd2104e fpga (-2 speed grade) included with the vcu1525 board supports up to gen3 x16 and gen4 x8. The pcie pex_refclk_p/n pair is input from the cn1 edge...

Page 33: I2C Bus

Vcu1525 acceleration platform user guide 33 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the qsfp+ connectors j7 and j9 i2c scl/sda are accessible through the tca9548 i2c switch u28 iic_main_scl/sda bus. See i2c bus . The qsfp+ connectors j7 and j9 i2c contr...

Page 34

Vcu1525 acceleration platform user guide 34 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the vcu1525 board i2c_fpga_sda/scl bus topology is shown in figure 3-13 . Important: pca9546 u28 reset_b pin 3 is connected to u13 fpga bank 64 pin bf19 via level-shifte...

Page 35

Vcu1525 acceleration platform user guide 35 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions table 3-5 lists the i2c address of the pca9546 u28 bus switch target devices. Msp432 user applications that communicate with devices on one of the downstream i2c buses m...

Page 36

Vcu1525 acceleration platform user guide 36 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the vcu1525 board i2c_fpga_sda/scl bus topology is shown in figure 3-14 . Table 3-6 lists the i2c address of the pca9546 u56 bus switch target devices. X-ref target - fi...

Page 37: Status Leds

Vcu1525 acceleration platform user guide 37 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions status leds the vcu1525 board is designed to operate with the heat sink and fan enclosure cover installed. Status light emitting diode (led) ds3 is a triple-stack led wh...

Page 38

Vcu1525 acceleration platform user guide 38 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions table 3-8 shows the msp432 key features. Table 3-8: key features of the msp432p401ripz device feature value flash (kb) 256 sram (kb) 64 adc14 (channels) 24 external, 2 i...

Page 39

Vcu1525 acceleration platform user guide 39 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions figure 3-15 shows the u19 msp432 i2c connectivity. X-ref target - figure 3-15 figure 3-15: u19 msp432 i2c connectivity fpga csn spix4 qspi1 spix4 csn csn sysmon msp432 s...

Page 40

Vcu1525 acceleration platform user guide 40 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions figure 3-16 shows the u19 msp432 circuit. See the schematic 0381795 (rev. D) sheet 24 for finer details [ref 7] . X-ref target - figure 3-16 figure 3-16: msp432 circuit ...

Page 41

Vcu1525 acceleration platform user guide 41 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions figure 3-17 shows the voltage and sense points monitored by the u19 msp432. See schematic 0381795 (rev. D) sheet 24 for finer details. [ref 7] . X-ref target - figure 3-...

Page 42: Vcu1525 Board Power System

Vcu1525 acceleration platform user guide 42 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions vcu1525 board power system the vcu1525 board hosts a linear technology based power system. Essential input power rails are sourced from the 16-lane pcie connector cn1 th...

Page 43

Vcu1525 acceleration platform user guide 43 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the vcu1525 board uses power regulators from linear technology to supply the core and auxiliary voltages. The v ccint 2-phase (of 6) regulator u41 is pmbus-compliant. Th...

Page 44

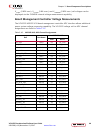

Vcu1525 acceleration platform user guide 44 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions v ccint (0.85v nom.), v ccaux (1.8v nom.), and v ccbram (0.85v nom.) rail voltages can be displayed via the sysmon internal voltage measurement capability. Board managem...

Page 45: Vccint Regulator Circuit

Vcu1525 acceleration platform user guide 45 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions each voltage listed in table 3-10 is scaled through a resistor attenuator network and the resulting scaled voltage is connected to the specified msp432 board management ...

Page 46

Vcu1525 acceleration platform user guide 46 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com chapter 3: board component descriptions the fan speed (pwm) versus the fpga die temperature algorithm along with the over temperature set point and fan failure alarm mechanisms are defined by user values progr...

Page 47: Overview

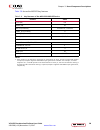

Vcu1525 acceleration platform user guide 47 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a master constraints file listing overview the master xilinx® design constraints (xdc) file template for the vcu1525 board provides for designs targeting the vcu1525 reconfigurable acceleration platfo...

Page 48

Vcu1525 acceleration platform user guide 48 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing # mgt_si570_clock set_property package_pin m10 [get_ports mgt_si570_clock0_c_n]; set_property iostandard lvds [get_ports mgt_si570_clock0_c_n]; set_property package_...

Page 49

Vcu1525 acceleration platform user guide 49 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin at35 [get_ports ddr4_c0_ba0]; set_property iostandard sstl12_dci [get_ports ddr4_c0_ba0]; set_property package_pin at34 [get_ports ddr4_c0_b...

Page 50

Vcu1525 acceleration platform user guide 50 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard pod12_dci [get_ports ddr4_c0_dq8]; set_property package_pin bf28 [get_ports ddr4_c0_dq9]; set_property iostandard pod12_dci [get_ports ddr4_c...

Page 51

Vcu1525 acceleration platform user guide 51 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin ar32 [get_ports ddr4_c0_dq38]; set_property iostandard pod12_dci [get_ports ddr4_c0_dq38]; set_property package_pin ar31 [get_ports ddr4_c0_...

Page 52

Vcu1525 acceleration platform user guide 52 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard pod12_dci [get_ports ddr4_c0_dq67]; set_property package_pin bf37 [get_ports ddr4_c0_dq68]; set_property iostandard pod12_dci [get_ports ddr4...

Page 53

Vcu1525 acceleration platform user guide 53 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin ba32 [get_ports ddr4_c0_dqs_t12]; set_property iostandard diff_pod12 [get_ports ddr4_c0_dqs_t12]; set_property package_pin ap31 [get_ports d...

Page 54

Vcu1525 acceleration platform user guide 54 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard sstl12_dci [get_ports ddr4_c1_adr17]; set_property package_pin au24 [get_ports ddr4_c1_ba0]; set_property iostandard sstl12_dci [get_ports dd...

Page 55

Vcu1525 acceleration platform user guide 55 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin au13 [get_ports ddr4_c1_dq8]; set_property iostandard pod12_dci [get_ports ddr4_c1_dq8]; set_property package_pin av13 [get_ports ddr4_c1_dq...

Page 56

Vcu1525 acceleration platform user guide 56 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard pod12_dci [get_ports ddr4_c1_dq37]; set_property package_pin bf14 [get_ports ddr4_c1_dq38]; set_property iostandard pod12_dci [get_ports ddr4...

Page 57

Vcu1525 acceleration platform user guide 57 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin be25 [get_ports ddr4_c1_dq67]; set_property iostandard pod12_dci [get_ports ddr4_c1_dq67]; set_property package_pin bd23 [get_ports ddr4_c1_...

Page 58

Vcu1525 acceleration platform user guide 58 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard diff_pod12 [get_ports ddr4_c1_dqs_c12]; set_property package_pin an14 [get_ports ddr4_c1_dqs_t12]; set_property iostandard diff_pod12 [get_po...

Page 59

Vcu1525 acceleration platform user guide 59 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin h32 [get_ports ddr4_c2_adr17]; set_property iostandard sstl12_dci [get_ports ddr4_c2_adr17]; set_property package_pin d33 [get_ports ddr4_c2...

Page 60

Vcu1525 acceleration platform user guide 60 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard pod12_dci [get_ports ddr4_c2_dq7]; set_property package_pin j28 [get_ports ddr4_c2_dq8]; set_property iostandard pod12_dci [get_ports ddr4_c2...

Page 61

Vcu1525 acceleration platform user guide 61 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin e37 [get_ports ddr4_c2_dq37]; set_property iostandard pod12_dci [get_ports ddr4_c2_dq37]; set_property package_pin f38 [get_ports ddr4_c2_dq...

Page 62

Vcu1525 acceleration platform user guide 62 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard pod12_dci [get_ports ddr4_c2_dq66]; set_property package_pin a38 [get_ports ddr4_c2_dq67]; set_property iostandard pod12_dci [get_ports ddr4_...

Page 63

Vcu1525 acceleration platform user guide 63 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin b29 [get_ports ddr4_c2_dqs_c12]; set_property iostandard diff_pod12 [get_ports ddr4_c2_dqs_c12]; set_property package_pin c29 [get_ports ddr...

Page 64

Vcu1525 acceleration platform user guide 64 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard sstl12_dci [get_ports ddr4_c3_adr16]; set_property package_pin g16 [get_ports ddr4_c3_adr17]; set_property iostandard sstl12_dci [get_ports d...

Page 65

Vcu1525 acceleration platform user guide 65 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin r21 [get_ports ddr4_c3_dq7]; set_property iostandard pod12_dci [get_ports ddr4_c3_dq7]; set_property package_pin j24 [get_ports ddr4_c3_dq8]...

Page 66

Vcu1525 acceleration platform user guide 66 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard pod12_dci [get_ports ddr4_c3_dq36]; set_property package_pin c22 [get_ports ddr4_c3_dq37]; set_property iostandard pod12_dci [get_ports ddr4_...

Page 67

Vcu1525 acceleration platform user guide 67 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin n13 [get_ports ddr4_c3_dq66]; set_property iostandard pod12_dci [get_ports ddr4_c3_dq66]; set_property package_pin n14 [get_ports ddr4_c3_dq...

Page 68

Vcu1525 acceleration platform user guide 68 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property iostandard diff_pod12 [get_ports ddr4_c3_dqs_t11]; set_property package_pin m17 [get_ports ddr4_c3_dqs_c12]; set_property iostandard diff_pod12 [get_por...

Page 69

Vcu1525 acceleration platform user guide 69 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing set_property package_pin au20 [get_ports qsfp1_fs1]; set_property iostandard lvcmos12 [get_ports qsfp1_fs1]; set_property package_pin av21 [get_ports qsfp1_intl_ls];...

Page 70

Vcu1525 acceleration platform user guide 70 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix a: master constraints file listing # pcie perst set_property package_pin bd21 [get_ports pcie_perst_ls]; set_property iostandard lvcmos12 [get_ports pcie_perst_ls]; # fpga-to-msp432 (u19) uart channel...

Page 71: Overview

Vcu1525 acceleration platform user guide 71 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix b regulatory and compliance information overview this product is designed and tested to conform to the european union directives and standards described in this section. Refer to the vcu1525 board mas...

Page 72: Safety

Vcu1525 acceleration platform user guide 72 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix b: regulatory and compliance information electromagnetic compatibility en 55022:2010, information technology equipment radio disturbance characteristics – limits and methods of measurement en 55024:20...

Page 73: Xilinx Resources

Vcu1525 acceleration platform user guide 73 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix c additional resources and legal notices xilinx resources for support resources such as answers, documentation, downloads, and forums, see xilinx support . Solution centers see the xilinx solution cen...

Page 74: References

Vcu1525 acceleration platform user guide 74 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix c: additional resources and legal notices references the most up to date information related to the vcu1525 board and its documentation is available on the following websites. Vcu1525 acceleration dev...

Page 75

Vcu1525 acceleration platform user guide 75 ug1268 (v1.0) november 13, 2017 www.Xilinx.Com appendix c: additional resources and legal notices 16. Sdx environments hardware platform development guide (ug1269) please read: important legal notices the information disclosed to you hereunder (the “materi...