- DL manuals

- Xilinx

- Computer Hardware

- Virtex-4 FX FPGA

- User manual

Xilinx Virtex-4 FX FPGA User manual

Summary of Virtex-4 FX FPGA

Page 1

R ml42x user guide virtex-4 fx fpga rocketio characterization platform ug087 (v1.3) may 30, 2008 p/n 0402349-02 www.Bdtic.Com/xilinx.

Page 2: Revision History

Ml42x user guide www.Xilinx.Com ug087 (v1.3) may 30, 2008 xilinx is disclosing this user guide, manual, release note, and/or specification (the "documentation") to you solely for use in the development of designs to operate with xilinx hardware devices. You may not reproduce, distribute, republish, ...

Page 3: Table of Contents

Ml42x user guide www.Xilinx.Com 3 ug087 (v1.3) may 30, 2008 preface: about this guide additional documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 additional support resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4: Www.Bdtic.Com/xilinx

4 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 r www.Bdtic.Com/xilinx.

Page 5: Schedule of Tables

Ml42x user guide www.Xilinx.Com 5 ug087 (v1.3) may 30, 2008 preface: about this guide ml42x rocketio characterization platform table 1: platforms, devices, and packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 table 2: onboard regulation . . . . . . . . . . . ...

Page 6: Www.Bdtic.Com/xilinx

6 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 r www.Bdtic.Com/xilinx.

Page 7: About This Guide

Ml42x user guide www.Xilinx.Com 7 ug087 (v1.3) may 30, 2008 r preface about this guide this document describes the features and operation of the virtex ® -4 fx fpga ml42x series of rocketio™ characterization platforms. Additional documentation information about the virtex-4 family of fpgas at http:/...

Page 8: Typographical Conventions

8 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 preface: about this guide r typographical conventions this document uses the following conventions. An example illustrates each convention. Online document the following conventions are used in this document: convention meaning or use examp...

Page 9: Package Contents

Ml42x user guide www.Xilinx.Com 9 ug087 (v1.3) may 30, 2008 r ml42x rocketio characterization platform package contents • virtex ® -4 fx fpga rocketio™ characterization platform (referred to as the ml42x platform) • user guide • sma-to-sma cable assemblies ♦ four 24-inch cables ♦ two 12-inch cables ...

Page 10: Related Documents

10 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 related documents r related documents prior to using the ml42x platforms, users should be familiar with xilinx resources. See “references,” page 30 for direct links to xilinx documentation. See the following locations for additional docume...

Page 11: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 11 ug087 (v1.3) may 30, 2008 introduction r figure 1 shows a block diagram of the board. Figure 1: virtex-4 fpga ml42x platform block diagram xgi xgi leds gp sws pb sw 3 pb sw 4 osc sma osc socket sma 2 x 1 sma 2 x1 right angle sma right angle sma right angle sma righ...

Page 12: Detailed Description

12 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r detailed description the ml423 platform, shown in figure 2 , is an example of the ml42x series described in this user guide. Each feature is detailed in the numbered sections that follow. Note: the image might not re...

Page 14: Www.Bdtic.Com/xilinx

14 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r mgt power supply module the mgt power supply module supplies all voltages shown in table 3 to the dut rocketio transceivers. This module plugs in on the right side of the board on header j12 for the ml421 platform, a...

Page 15: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 15 ug087 (v1.3) may 30, 2008 detailed description r 3. Oscillator sockets the ml42x platform has two crystal oscillator sockets, each wired for standard lvttl-type oscillators. These connect to the fpga clock pins shown in table 4 . The oscillator sockets accept both ...

Page 16: Www.Bdtic.Com/xilinx

16 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r 6. Differential sma global clocks two pairs of 100 Ω differentially routed sma connectors allow the user to connect to an external differential function generator. These connect to the global clock (gc) pins of the f...

Page 17: Www.Bdtic.Com/xilinx

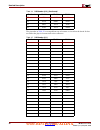

Ml42x user guide www.Xilinx.Com 17 ug087 (v1.3) may 30, 2008 detailed description r 9. User dip switches (active-high) there are 20 active-high dip switches, as shown in table 11 and table 12, page 18 , connected to user i/o pins on the fpga. These pins can be used to set control pins or any other p...

Page 18: Www.Bdtic.Com/xilinx

18 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r 10. User pushbutton switches (active-high) four active-high pushbutton switches, shown in table 13 , are connected to user i/o pins on the fpga. These switches can be used for any purpose that the user designates. 5 ...

Page 19: Www.Bdtic.Com/xilinx

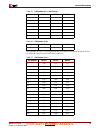

Ml42x user guide www.Xilinx.Com 19 ug087 (v1.3) may 30, 2008 detailed description r 11. Xilinx generic interface the xgi is an expansion interface for plug-in modules (for example, the superclock module) and provides the user access to the i/o pins listed in table 14 , table 15, page 20 , and table ...

Page 20: Www.Bdtic.Com/xilinx

20 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r the pin order in table 15 is arranged from top to bottom as viewed on the board. It does not reflect the physical connection to this connector. 57 ad16 am22 ar26 59 ac16 am21 ap26 61 ab15 al19 at24 63 aa15 al18 ar24 ...

Page 21: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 21 ug087 (v1.3) may 30, 2008 detailed description r the pin order in table 17 is arranged from top to bottom as viewed on the board. It does not reflect the physical connection to this connector. 26 vcc3 vcc3 vcc3 27 vcc3 vcc3 vcc3 28 nc nc nc 29 vcc5 vcc5 vcc5 30 vcc...

Page 22: Www.Bdtic.Com/xilinx

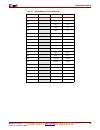

22 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r 12. Lvds header interface the lvds header interface allows the user to experiment with the lvds i/o pairs as shown in table 18, page 22 and table 19, page 24 . These i/o pins can also be used for any purpose designat...

Page 23: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 23 ug087 (v1.3) may 30, 2008 detailed description r 24 h10 d10 26 g7 e8 28 h7 f8 30 m12 e3 32 m11 f3 34 ab11 ah14 36 aa11 ah13 38 ad12 at15 40 ae12 au15 42 ag13 al13 44 ah13 am13 46 al8 an8 48 ak8 an7 50 al10 au10 52 am10 at10 54 aj12 ap11 56 ak12 ar11 58 ak13 ak11 60...

Page 24: Www.Bdtic.Com/xilinx

24 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r note: all remaining i/o pins are connected to external capacitors for i/o load testing. 13. Program switch (active-low) the active-low program switch, when pressed, grounds the program pin of the fpga. 14. Reset swit...

Page 25: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 25 ug087 (v1.3) may 30, 2008 detailed description r 17. System ace controller an onboard system ace controller allows the user to store multiple configuration files on a compactflash memory card. These configuration files can be used to program the fpga. 18. Configura...

Page 26: Www.Bdtic.Com/xilinx

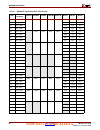

26 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r j65 rxn_102b x0y2 x0y4 x0y6 x0y6 x0y8 d26 k34 d39 j73 rxp_102b c26 j34 c39 j70 txn_102b a25 g34 a37 j69 txp_102b a24 f34 a36 j86 txn_103a x0y3 x0y5 x0y5 x0y7 n26 w34 n39 j75 txp_103a m26 v34 m39 j78 rxn_103a k26 t34 ...

Page 27: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 27 ug087 (v1.3) may 30, 2008 detailed description r j127 rxn_106b x0y0 x0y0 x0y0 ap17 aw21 j126 rxp_106b ap18 aw22 j128 txn_106b ap20 aw24 j125 txp_106b ap21 aw25 j110 txn_109a x1y1 x1y1 x1y1 ap10 aw13 j109 txp_109a ap9 aw12 j108 rxn_109a ap7 aw10 j107 rxp_109a ap6 aw...

Page 28: Www.Bdtic.Com/xilinx

28 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 detailed description r j35 rxn_112b x1y2 x1y4 x1y4 x1y6 ab1 aa1 v1 j38 rxp_112b aa1 y1 u1 j40 txn_112b w1 v1 r1 j39 txp_112b v1 u1 p1 j57 txn_113a x1y3 x1y5 x1y7 x1y7 x1y9 c1 a3 a5 j50 txp_113a b1 a4 a6 j54 rxn_113a a3 a6 a8 j53 rxp_113a a...

Page 29: Www.Bdtic.Com/xilinx

Ml42x user guide www.Xilinx.Com 29 ug087 (v1.3) may 30, 2008 detailed description r 20. Rs-232 port the rs-232 port pins are as shown in table 22 . The pins are set up in dte mode as shown in figure 3 . 21. External bias potentiometers (rterm) each virtex-4 fpga mgt column has two external pins that...

Page 30: References

30 www.Xilinx.Com ml42x user guide ug087 (v1.3) may 30, 2008 references r 22. System ace mpu port the 8-bit mpu port of the system ace controller implemented on the ml52x series boards and the port connection to the dut are shown in table 23 . For more information on the system ace mpu port see syst...