- DL manuals

- Xilinx

- Transceiver

- Virtex-4 RocketIO

- User Manual

Xilinx Virtex-4 RocketIO User Manual

Summary of Virtex-4 RocketIO

Page 1

R virtex-4 rocketio multi-gigabit transceiver user guide ug076 (v4.1) november 2, 2008.

Page 2

Virtex-4 rocketio mgt user guide www.Xilinx.Com ug076 (v4.1) november 2, 2008 xilinx is disclosing this user guide, manual, release note, and/or specification (the "documentation") to you solely for use in the development of designs to operate with xilinx hardware devices. You may not reproduce, dis...

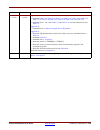

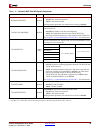

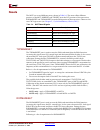

Page 3: Revision History

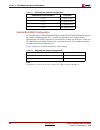

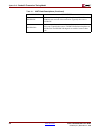

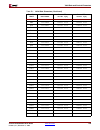

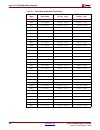

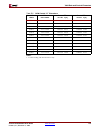

Ug076 (v4.1) november 2, 2008 www.Xilinx.Com virtex-4 rocketio mgt user guide revision history the following table shows the revision history for this document. Date version revision 03/01/05 1.0 xilinx initial release. 03/10/05 1.1 modified “power supply requirements” in chapter 6 and table 6-1, pa...

Page 4

Virtex-4 rocketio mgt user guide www.Xilinx.Com ug076 (v4.1) november 2, 2008 08/17/07 4.0 major revision. All material completely revised and updated. • general typographical edits. • added no data encoding and nrz signaling to “mgt features.” • removed 64b/66b encoding from preface, chapter 1 , ch...

Page 5

Ug076 (v4.1) november 2, 2008 www.Xilinx.Com virtex-4 rocketio mgt user guide 08/17/07 ( cont’d ) 4.0 ( cont’d ) • modified “10-bit alignment for 8b/10b encoded data.” • expanded sonet alignment sequence figure into figure 3-15 and figure 3-16 . • removed support of rxsync functionality in “rxslide....

Page 6

Virtex-4 rocketio mgt user guide www.Xilinx.Com ug076 (v4.1) november 2, 2008 08/17/07 ( cont’d ) 4.0 ( cont’d ) appendix c : • modified table c-2 to table c-6 , table c-8 to table c-11 , table c-13 to table c-15 , table c-17 to table c-20 , table c-23 , table c-24 , table c-26 , and table c-27 . • ...

Page 7: Section I:

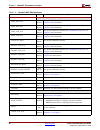

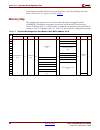

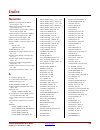

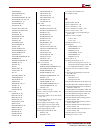

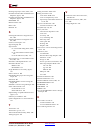

Virtex-4 rocketio mgt user guide www.Xilinx.Com 7 ug076 (v4.1) november 2, 2008 preface: about this guide mgt features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 user guide organization . . . . . . . . . . . . . . ...

Page 8

8 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r special clocking considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 rxclkstable and txclkstable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 9

Virtex-4 rocketio mgt user guide www.Xilinx.Com 9 ug076 (v4.1) november 2, 2008 r rxslide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123 clock correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 10

10 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r 32-bit example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159 16-bit transmission, hold crc, and residue of 8-bit example . . . . . . . . . . . ...

Page 11

Virtex-4 rocketio mgt user guide www.Xilinx.Com 11 ug076 (v4.1) november 2, 2008 r transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193 pcs data path latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 12: Section Ii:

12 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r restrictions on low latency buffer bypass modes . . . . . . . . . . . . . . . . . . . . . . . . . . 229 example of a reduced-latency system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230...

Page 13: Section Iii:

Virtex-4 rocketio mgt user guide www.Xilinx.Com 13 ug076 (v4.1) november 2, 2008 r microstrip/stripline bends . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252 bga packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 14

14 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r power supply filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328 other minor differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

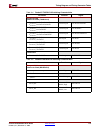

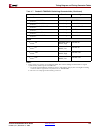

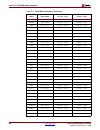

Page 15: Section I:

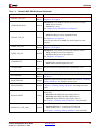

Virtex-4 rocketio mgt user guide www.Xilinx.Com 15 ug076 (v4.1) november 2, 2008 section i: fpga level design chapter 1: rocketio transceiver overview figure 1-1: rocketio multi-gigabit transceiver block diagram . . . . . . . . . . . . . . . . . . . . 36 chapter 2: clocking, timing, and resets figur...

Page 16

16 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r figure 3-2: receive architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102 figure 3-3: rx ring buffer half-full upon initialization . . . . . . . . . . . . . . ....

Page 17

Virtex-4 rocketio mgt user guide www.Xilinx.Com 17 ug076 (v4.1) november 2, 2008 r chapter 6: analog and board design considerations figure 6-1: mgt tile power and serial i/o pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164 figure 6-2: internal receiver ac coupling with ext...

Page 18: Section Ii:

18 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r figure 8-21: rx low latency buffer bypass mode: use model rx_2c . . . . . . . . . . . . . 227 figure 8-22: rxsync timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 19: Section Iii:

Virtex-4 rocketio mgt user guide www.Xilinx.Com 19 ug076 (v4.1) november 2, 2008 r figure 12-3: via structures for bga adjacent sio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262 figure 12-4: xenpak70 connector design example . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 20

20 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r.

Page 21: Section I:

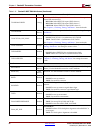

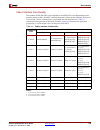

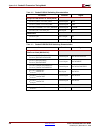

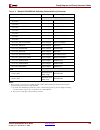

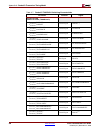

Virtex-4 rocketio mgt user guide www.Xilinx.Com 21 ug076 (v4.1) november 2, 2008 section i: fpga level design chapter 1: rocketio transceiver overview table 1-1: number of mgt cores per device type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 table 1-2: communications standards s...

Page 22

22 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r table 3-7: rxchariscomma truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114 table 3-8: deserializer comma detection bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 23

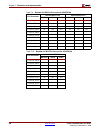

Virtex-4 rocketio mgt user guide www.Xilinx.Com 23 ug076 (v4.1) november 2, 2008 r table 6-4: selectio pin guidance for xc4vfx100/60/40-ff1152 . . . . . . . . . . . . . . . . . . . . 175 table 6-5: selectio pin guidance for xc4vfx140/100-ff1517 . . . . . . . . . . . . . . . . . . . . . 176 chapter 7...

Page 24: Section Ii:

24 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r section ii: board level design chapter 9: methodology overview chapter 10: pcb materials and traces chapter 11: design of transitions chapter 12: guidelines and examples table 12-1: model-derived loss for differential...

Page 25

Virtex-4 rocketio mgt user guide www.Xilinx.Com 25 ug076 (v4.1) november 2, 2008 r table c-12: dynamic reconfiguration port memory map: mgta address 72–76 . . . . 304 table c-13: dynamic reconfiguration port memory map: mgta address 77–7b . . . 305 table c-14: dynamic reconfiguration port memory map...

Page 26

26 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 r.

Page 27: About This Guide

Virtex-4 rocketio mgt user guide www.Xilinx.Com 27 ug076 (v4.1) november 2, 2008 r preface about this guide the virtex ® -4 rocketio™ mgt user guide provides the product designer with the detailed technical information needed to successfully implement the rocketio mgt in virtex-4 platform fpga desig...

Page 28: User Guide Organization

28 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 preface: about this guide r user guide organization this guide is organized as follows: section i: fpga level design • chapter 1, “rocketio transceiver overview” – mgt basic architecture and capabilities. Includes avail...

Page 29: Related Information

Virtex-4 rocketio mgt user guide www.Xilinx.Com 29 ug076 (v4.1) november 2, 2008 related information r related information for a complete menu of online information resources available on the xilinx website, visit http://www.Xilinx.Com/virtex4/ . For a comprehensive listing of available tutorials an...

Page 30

30 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 preface: about this guide r port and attribute names all input and output ports of the rocketio transceiver primitives are denoted in upper- case letters. Attributes of the rocketio transceiver can be denoted in upper-c...

Page 31

Virtex-4 rocketio mgt user guide www.Xilinx.Com 31 ug076 (v4.1) november 2, 2008 user guide conventions r typographical the following typographical conventions are used in this document: convention meaning or use example courier font messages and prompts that the system displays speed grade: - 100 c...

Page 32

32 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 preface: about this guide r.

Page 33: Section I:

R section i: fpga level design virtex-4 rocketio multi-gigabit transceiver.

Page 34

Virtex-4 rocketio mgt user guide www.Xilinx.Com ug076 (v4.1) november 2, 2008.

Page 35

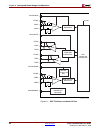

Virtex-4 rocketio mgt user guide www.Xilinx.Com 35 ug076 (v4.1) november 2, 2008 r chapter 1 rocketio transceiver overview basic architecture and capabilities the rocketio™ multi-gigabit transceiver (mgt) block diagram is illustrated in figure 1-1, page 36 . Depending on the device, a virtex®-4 fpga...

Page 36

36 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r figure 1-1: rocketio multi-gigabit transceiver block diagram 8 b/10b decoder fpga fabric fpga fabric multi-gigabit tran s ceiver core s eri a lizer rxp txp clock m a n a ger pa...

Page 37

Virtex-4 rocketio mgt user guide www.Xilinx.Com 37 ug076 (v4.1) november 2, 2008 basic architecture and capabilities r the rocketio mgt transceiver consists of the physical media attachment (pma) and physical coding sublayer (pcs). The pma contains the serializer/deserializer (serdes), tx and rx inp...

Page 38

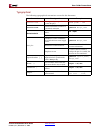

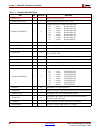

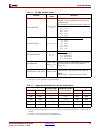

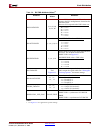

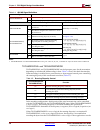

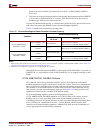

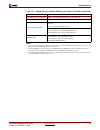

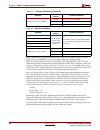

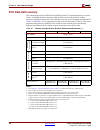

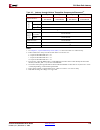

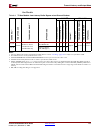

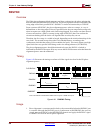

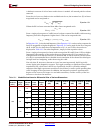

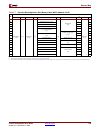

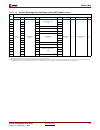

38 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r 2x fibre channel 2.125 8b/10b 212.5 2 106.25 1 212.50 1x fibre channel 1.0625 8b/10b 212.5 2 53.13 1 106.25 1000base-x 1.25 8b/10b 250.0 (5) 2 62.50 1 125.0 oc-12 0.622 none 15...

Page 39: Configuring The Rocketio Mgt

Virtex-4 rocketio mgt user guide www.Xilinx.Com 39 ug076 (v4.1) november 2, 2008 configuring the rocketio mgt r configuring the rocketio mgt there are two ways to configure a rocketio transceiver: 1. Static configuration. The transceiver is configured using a combination of port tie-offs and attribu...

Page 40

40 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r table 1-4: rocketio mgt crc ports port i/o port size definition rxcrcclk i 1 receiver crc logic clock. Rxcrcdatavalid i 1 signals that the rxcrcin data is valid. Rxcrcdatawidth...

Page 41

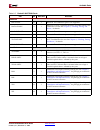

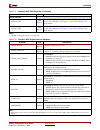

Virtex-4 rocketio mgt user guide www.Xilinx.Com 41 ug076 (v4.1) november 2, 2008 available ports r \ table 1-5: rocketio mgt pma ports port i/o port size definition calibration rxcalfail o 1 reserved. This calibration port is not supported. Rxclkstable i 1 when set to a logic 1, indicates the clocks...

Page 42

42 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r clocks/clock status rxlock o 1 when set to logic 1, indicates that the receiver is locked to the reference clock or locked to the input data. Logic 0 indicates the receiver is ...

Page 43

Virtex-4 rocketio mgt user guide www.Xilinx.Com 43 ug076 (v4.1) november 2, 2008 available ports r special signals rxsigdet o 1 when set to logic 1, indicates that an out-of-band (oob) signal has been detected. When proper differential signal input is being received, rxsigdet is logic 0. See chapter...

Page 44

44 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r 8b/10b rxcharisk o 8 if 8b/10b decoding is enabled, it indicates that the received data is a “k” character when asserted. (see table 1-15, page 60 for association with rx data....

Page 45

Virtex-4 rocketio mgt user guide www.Xilinx.Com 45 ug076 (v4.1) november 2, 2008 available ports r txcharisk i 8 if txenc8b10buse = 1 (8b/10b encoder enable), then txcharisk[7:0] signals the k-definition of the txdata byte in the corresponding byte lane. Txenc8b10buse i 1 if set to a logic 1, the 8b...

Page 46

46 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r txdatawidth i 2 indicates width of fpga parallel bus. (see table 3-1, page 104 .) txintdatawidth i 2 sets the internal mode of the transmit pcs: 2’b10 = 32-bit 2’b11 = 40-bit s...

Page 47

Virtex-4 rocketio mgt user guide www.Xilinx.Com 47 ug076 (v4.1) november 2, 2008 available ports r table 1-7: rocketio mgt general ports port i/o port size definition loopback i 2 selects the two loopback test modes. These modes are pcs parallel, and pre-driver serial loopback. See chapter 3, “pcs d...

Page 48: Attributes

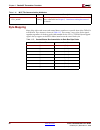

48 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r attributes an attribute is a control parameter used to configure the mgt. There are both primitive ports (traditional i/o ports for control and status) and attributes. Transcei...

Page 49

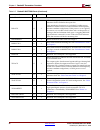

Virtex-4 rocketio mgt user guide www.Xilinx.Com 49 ug076 (v4.1) november 2, 2008 attributes r rxcrcinvertgen boolean false/true . Inverts the receiver crc clock. False : crc clock not inverted. True : crc clock inverted. During normal operation, this should always be set to false . Txcrcclockdouble ...

Page 50

50 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r table 1-11: rocketio mgt pma attributes attribute type description calibration fdet_hys_cal 3-bit binary sets up the calibration circuitry. See “calibration for the plls” in ch...

Page 51

Virtex-4 rocketio mgt user guide www.Xilinx.Com 51 ug076 (v4.1) november 2, 2008 attributes r txpost_tap_dac 5-bit binary transmitter post-cursor amplitude control. See “output swing and emphasis” in chapter 4 . Txhighsignalen boolean true/false . This attribute controls the line driver strength. Tr...

Page 52

52 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r txabpmaclksel string refclk1, refclk2, grefclk . Selects reference clock input for shared tile transmit pll. Refclk1 : select refclk1 input (drp value 00 ). Refclk2 : select re...

Page 53

Virtex-4 rocketio mgt user guide www.Xilinx.Com 53 ug076 (v4.1) november 2, 2008 attributes r rxcmadj 2-bit binary reserved. Use the rocketio wizard to set this attribute. Power_enable boolean true / false . True : powers up the pcs and digital receiver of the transceiver. False : powers down the pc...

Page 54

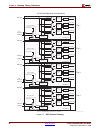

54 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r table 1-12: rocketio mgt pcs attributes attribute type description channel bonding cccb_arbitrator_disable boolean false/true . Determines if the clock correction/channel bondi...

Page 55

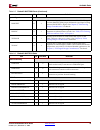

Virtex-4 rocketio mgt user guide www.Xilinx.Com 55 ug076 (v4.1) november 2, 2008 attributes r chan_bond_seq_1_mask 4-bit binary each bit of the mask determines if that particular sequence is detected regardless of its value. For example, if bit 0 is high, then chan_bond_seq_1_1 is matched regardless...

Page 56

56 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r clk_cor_seq_1_mask 4-bit binary each bit of the mask determines if that particular sequence is detected regardless of its value. For example, if bit 0 is high, then clk_cor_seq...

Page 57

Virtex-4 rocketio mgt user guide www.Xilinx.Com 57 ug076 (v4.1) november 2, 2008 attributes r mcomma_32b_value 32-bit hex these define minus-comma for the purpose of raising rxcommadet and realigning the serial bit stream byte boundary. This definition does not affect 8b/10b encoding or decoding. Re...

Page 58

58 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r clocks rxclk0_force_pmaclk boolean false/true . Determines if the pma rxclk0 or the rxusrclk is chosen as the source for the pcs rxclk in conjunction with rx_clock_divider and ...

Page 59

Virtex-4 rocketio mgt user guide www.Xilinx.Com 59 ug076 (v4.1) november 2, 2008 attributes r bypass controls rxdata_sel 2-bit binary selects which blocks are bypassed in the rx pcs data path. See “ports and attributes” in chapter 8, “low-latency design” for more details. Txdata_sel 2-bit binary sel...

Page 60: Byte Mapping

60 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 1: rocketio transceiver overview r byte mapping most of the 8-bit wide status and control buses correlate to a specific byte of the txdata or rxdata. This scheme is shown in table 1-15 . This creates a way to ti...

Page 61: Clocking, Timing, and Resets

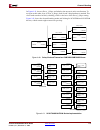

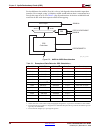

Virtex-4 rocketio mgt user guide www.Xilinx.Com 61 ug076 (v4.1) november 2, 2008 r chapter 2 clocking, timing, and resets clock distribution the rocketio™ mgt clock distribution has changed from previous generations to support the columnar architecture of the virtex®-4 devices. Column a column consi...

Page 62

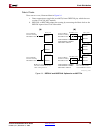

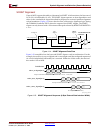

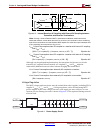

62 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r figure 2-1: mgt column clocking s h a red tr a n s mit pll divider s divider s receive pll a receive pll b divider s divider s pma rxclk a pma rxclk b pma txclk b pma txclk a ti...

Page 63

Virtex-4 rocketio mgt user guide www.Xilinx.Com 63 ug076 (v4.1) november 2, 2008 clock distribution r this chapter also includes several use models (see “common reference clock use models,” page 66 ). The use models illustrated here represent the most common configurations, but other configurations ...

Page 64

64 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r mgt clock ports and attributes the rocketio mgt has four groups of clocks: reference, user, mgt output, and crc logic clocks. The clock ports are shown in table 2-2 . Table 2-3 ...

Page 65

Virtex-4 rocketio mgt user guide www.Xilinx.Com 65 ug076 (v4.1) november 2, 2008 clock distribution r the mgtclk inputs drive the reference clocks that are low-jitter and must be used for the fastest data rates (over 1 gb/s). Additionally, one of the fpga fabric (global) clocks can be used as a refe...

Page 66

66 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r common reference clock use models high-speed dedicated mgt clocks illustrated in figure 2-2 is the common use case where the standard gt11clk_mgt module is used to route the ded...

Page 67

Virtex-4 rocketio mgt user guide www.Xilinx.Com 67 ug076 (v4.1) november 2, 2008 clock distribution r fabric clocks there are two cases, illustrated here in figure 2-3 : a. Direct connection to single tile (two mgts) from grefclk pin, which does not use the gt11clk_mgt module. B. Refclk1 or refclk2 ...

Page 68

68 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r pma transmit clocks the pma transmit block has several clocking options. These options include several dividers that determine the relationship between the parallel clocks (txou...

Page 69

Virtex-4 rocketio mgt user guide www.Xilinx.Com 69 ug076 (v4.1) november 2, 2008 clock distribution r table 2-4: tx pma attribute values (1) attribute available values definition txpllndivsel 40, 32, 20, 16, 10, 8 transmit pll feedback divide. This value becomes the pll multiplication factor for the...

Page 70

70 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r pma receive clocks the pma receive block has several clocking options. These options include several dividers that determine the relationship between the parallel clocks (rxrecc...

Page 71

Virtex-4 rocketio mgt user guide www.Xilinx.Com 71 ug076 (v4.1) november 2, 2008 clock distribution r table 2-6: rx pma attribute values (1) attribute available values definition rxpllndivsel 8, 10, 16, 20, 16, 32, 40 receive pll feedback divide. This value becomes the pll multiplication factor for ...

Page 72

72 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r rx and tx pll voltage-controlled oscillator (vco) operating fre q uency the minimum vco operating frequency is 2480 mhz. The maximum vco operating frequency is limited by the va...

Page 73

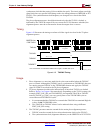

Virtex-4 rocketio mgt user guide www.Xilinx.Com 73 ug076 (v4.1) november 2, 2008 clock distribution r figure 2-6: transmitter and receiver line rates tx 622 m b / s 1.075 g b / s 1.24 g b / s 1.25 g b / s 2.15 g b / s 2.4 8 g b / s 4.3 g b / s 4.96 g b / s 6.5 g b / s tx tx tx rx dcdr rx acdr rx acd...

Page 74

74 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r pma/pcs clocking domains and data paths there are several clocking domains within the pma and pcs of the mgt’s receiver and transmitter. For the rx, there are four clock domains...

Page 75

Virtex-4 rocketio mgt user guide www.Xilinx.Com 75 ug076 (v4.1) november 2, 2008 pma/pcs clocking domains and data paths r pma configurations there are several configurations of the pma that also affect serial speeds and clocking schemes. These configurations can be modified by the dynamic reconfigu...

Page 76

76 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r common mgt clocking use cases figure 2-9 and figure 2-10 show the common clocking use models that the mgt supports. Note: txoutclk1/txoutclk2 / rxrecclk1/rxrecclk2 connect to lo...

Page 77: Setting The Clocking Options

Virtex-4 rocketio mgt user guide www.Xilinx.Com 77 ug076 (v4.1) november 2, 2008 setting the clocking options r setting the clocking options because of the mgt’s flexibility, there are many different clocking modes available. The rocketio wizard can automatically configure the mgt clocking options f...

Page 78

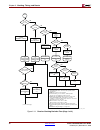

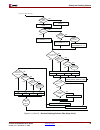

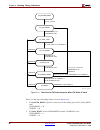

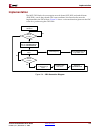

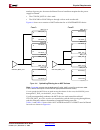

78 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r figure 2-11: receive clocking decision flow (page 1 of 2) i s line r a te > 5 g i s line r a te >2.5g no no no no rxoutdiv 2 s el = / 1 vco r a te = line r a te / 2 = / 2 vco r ...

Page 79

Virtex-4 rocketio mgt user guide www.Xilinx.Com 79 ug076 (v4.1) november 2, 2008 setting the clocking options r figure 2-11 (cont’d): receive clocking decision flow (page 2 of 2) 64b/66b decoding? ( 8 ) rxclkmode[5:4] = 11 rxclkmode[2:1] = 10 rxclkmode[5:4] = 00 rxclkmode[2:1] = 01 rxclkmode[5:4] = ...

Page 80

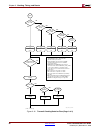

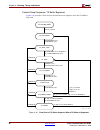

80 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r figure 2-12: transmit clocking decision flow (page 1 of 2) i s line r a te >5g i s line r a te >2.5g i s line r a te >1.25g i s line r a te >0.625g no no no no txoutdiv2 s el = ...

Page 81

Virtex-4 rocketio mgt user guide www.Xilinx.Com 81 ug076 (v4.1) november 2, 2008 setting the clocking options r fi figure 2-12 (cont’d): transmit clocking decision flow (page 2 of 2) provide u s rclk (6) extern a lly? 1 - b yte f ab ric interf a ce 2 - b yte f ab ric interf a ce tx _ clock _ divider...

Page 82

82 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r special clocking considerations rxclkstable and txclkstable in some systems, there are cases where the reference clock is not available when the mgt and fpga come out of configu...

Page 83: Resets

Virtex-4 rocketio mgt user guide www.Xilinx.Com 83 ug076 (v4.1) november 2, 2008 resets r resets the mgt has several different resets shown in table 2-9 . The resets affect different portions of the mgt. Rxreset and txreset reset the pcs portions of the transceiver. Rxpmareset and txpmareset reset t...

Page 84

84 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r • set rxpmareset to logic 1 at startup for a minimum of three usrclk cycles (based on internal data width). • do not use the output clocks of the mgt for clocking this reset. Tx...

Page 85

Virtex-4 rocketio mgt user guide www.Xilinx.Com 85 ug076 (v4.1) november 2, 2008 resets r • rx buffer — rxusrclk and pcs rxclk domains • channel bonding & clock correction logic — rxusrclk and pcs rxclk domains • comma detect align — pcs rxclk domain • digital cdr see figure 2-7 , “pcs receive clock...

Page 86

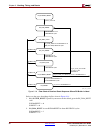

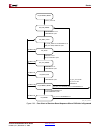

86 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r below are the steps describing the flow chart in figure 2-14 : 1. Tx_system_reset: upon tx system reset on this block, go to the tx_pma_reset state. Txpmareset == 0 txreset == 0...

Page 87

Virtex-4 rocketio mgt user guide www.Xilinx.Com 87 ug076 (v4.1) november 2, 2008 resets r 3. Tx_wait_lock: stall until txlock is high and until the clocks on txusrclk and txusrclk2 are stable (tx_usrclk_stable == 1). Txpmareset == 0 txreset == x 4. Tx_pcs_reset: assert txreset for three txusrclk cyc...

Page 88

88 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r transmit reset se q uence: tx buffer bypassed figure 2-16 provides a flow chart of the transmit reset sequence when the tx buffer is bypassed. Figure 2-16: flow chart of tx rese...

Page 89

Virtex-4 rocketio mgt user guide www.Xilinx.Com 89 ug076 (v4.1) november 2, 2008 resets r refer to the following points in conjunction with this figure: • the flow chart uses txusrclk and txusrclk2 as reference to the wait time for each state. Do not use txusrclk and txusrclk2 as the clock source fo...

Page 90

90 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r 3. Tx_wait_lock: stall until txlock is high and until the clocks on txusrclk and txusrclk2 are stable (tx_usrclk_stable == 1), then wait for 12,000 txusclk2 cycles and go to tx_...

Page 91

Virtex-4 rocketio mgt user guide www.Xilinx.Com 91 ug076 (v4.1) november 2, 2008 resets r • it is assumed that the frequency of txusrclk is slower than the frequency of txusrclk2. If txusrclk2 is slower, use that clock as reference to the wait time for each state. An exception of this requirement is...

Page 92

92 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r used to generate both the txusrclk and txusrclk2 clocks, then the dcm locked signal can be used here. • in synchronous systems like the gpon application, where rxrecclk1/rxreccl...

Page 93

Virtex-4 rocketio mgt user guide www.Xilinx.Com 93 ug076 (v4.1) november 2, 2008 resets r 7. Tx_ready: tx link is ready. Txpmareset == 0 txreset == 0 txsync == 0 figure 2-18 shows a timing diagram for resetting the transmitter when the tx buffer is bypassed. Refer to figure 2-16 and figure 2-17 for ...

Page 94

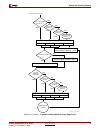

94 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r below are the steps describing the flow chart in figure 2-19 : 1. Rx_system_reset: upon rx system reset on this block, go to the rx_pma_reset state. Rxpmareset == 0 rxreset == 0...

Page 95

Virtex-4 rocketio mgt user guide www.Xilinx.Com 95 ug076 (v4.1) november 2, 2008 resets r 3. Rx_wait_lock: stall until rxlock is high and until the clocks on rxusrclk and rxusrclk2 are stable (rx_usrclk_stable == 1). In addition: ♦ for analog cdr mode, rx_wait_lock state should also stall until rxlo...

Page 96

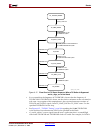

96 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r receive reset se q uence: rx buffer bypassed figure 2-22 provides a flow chart of the receive reset sequence when the rx buffer is bypassed. Refer to the following points in con...

Page 97

Virtex-4 rocketio mgt user guide www.Xilinx.Com 97 ug076 (v4.1) november 2, 2008 resets r figure 2-22: flow chart of receiver reset sequence where rx buffer is bypassed s y s tem_re s et==0 rx_ s y s tem_re s et rx_pma_re s et rx_wait_pc s rx_wait_lock rxpmare s et==1 for 3 rxu s rclk cycle s rxre s...

Page 98

98 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r below are the steps describing the flow chart in figure 2-22 : 1. Rx_system_reset: upon rx system reset on this block, go to the rx_pma_reset state. Rxpmareset == 0 rxreset == 0...

Page 99

Virtex-4 rocketio mgt user guide www.Xilinx.Com 99 ug076 (v4.1) november 2, 2008 resets r 8. Rx_ready: once rx_error is monitored low for some time, the rx link is ready for data reception. Rxpmareset == 0 rxreset == 0 rxsync == 0 figure 2-23 shows a timing diagram for resetting the rx transceiver w...

Page 100

100 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 2: clocking, timing, and resets r • for digital cdr, asserting rxreset causes the pma parallel clock rxrecclk1 to remain at a constant value. • when channel bonding is used in conjunction with 1-byte and 2-byte...

Page 101: Top-Level Architecture

Virtex-4 rocketio mgt user guide www.Xilinx.Com 101 ug076 (v4.1) november 2, 2008 r chapter 3 pcs digital design considerations the virtex®-4 rocketio™ mgt pcs supports 8b/10b encode/decode, sonet compatibility, and generic data modes. The mgt operates in two basic internal modes: 32 bit and 40 bit....

Page 102: Rx Buffer

102 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r fabric interface synchronicity the fabric interface affords a clock domain crossing between rx/txusrclk and rx/txusrclk2. To minimize latency, this cross-clock domain cros...

Page 103: Bus Interface

Virtex-4 rocketio mgt user guide www.Xilinx.Com 103 ug076 (v4.1) november 2, 2008 bus interface r the overflow mark is set when the difference between the write and read pointer is greater than 57 bytes. The underflow mark is set when the difference between the write and read pointer is less than 17...

Page 104

104 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r internal bus width configuration by using the signals txintdatawidth[1:0] and rxintdatawidth[1:0], the internal bus width can be designated. This is usually determined by ...

Page 105

Virtex-4 rocketio mgt user guide www.Xilinx.Com 105 ug076 (v4.1) november 2, 2008 bus interface r fabric interface functionality the number of rxusrclk2 cycles required to read rxdata varies depending on the interface mode (width). The mgt's internal datapath is 4 bytes wide; therefore, in 2-byte or...

Page 106

106 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r figure 3-5: fabric interface timing rxu s rclk2 32’h0 d3 d2 d1 d0 32’h0 8 ’h0 d3 d2 d1 32’h0 8 ’h0 d3 d2 d1 32’h0 8 ’h0 8 ’h0 d3 d2 32’h0 8 ’h0 8 ’h0 d3 d2 32’h0 8 ’h0 8 ’...

Page 107

Virtex-4 rocketio mgt user guide www.Xilinx.Com 107 ug076 (v4.1) november 2, 2008 bus interface r pcs bypass byte mapping when bypassing the entire rx pcs using an internal data width of 32 bits (rxdata_sel = 01 ), bytes are ordered as shown in figure 3-6 through figure 3-7 . Note that this mapping ...

Page 108: 8B/10B Encoding/decoding

108 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r 8b/10b encoding/decoding the gt11 supports the 8b/10b encoding and decoding scheme. These blocks can be enabled or bypassed both statically and on a clock-by-clock basis. ...

Page 109

Virtex-4 rocketio mgt user guide www.Xilinx.Com 109 ug076 (v4.1) november 2, 2008 8b/10b encoding/decoding r encoder a bypassable 8b/10b encoder is included in the transmitter. The encoder uses the same 256 data characters and 12 control characters (shown in appendix b, “8b/10b valid characters” ) t...

Page 110

110 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r txchardispval and txchardispmode txchardispval and txchardispmode are dual-purpose ports for the transmitter depending on whether 8b/10b encoding is done. Table 3-4 shows ...

Page 111

Virtex-4 rocketio mgt user guide www.Xilinx.Com 111 ug076 (v4.1) november 2, 2008 8b/10b encoding/decoding r mode where both txchardispmode and txchardispval are set to logic 0. Some applications can use other settings if special running disparity configurations are required, such as in the “non-sta...

Page 112

112 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r decoder an optional 8b/10b decoder is included in the receiver. A programmable option allows the decoder to be bypassed. When the 8b/10b decoder is bypassed, the 10-bit ch...

Page 113

Virtex-4 rocketio mgt user guide www.Xilinx.Com 113 ug076 (v4.1) november 2, 2008 8b/10b encoding/decoding r rxcharisk and rxrundisp rxcharisk and rxrundisp are dual-purpose ports for the receiver depending whether 8b/10b decoding is enabled. Table 3-6 shows this dual functionality. When decoding is...

Page 114

114 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r rxnotintable rxnotintable is set to a logic 1 whenever the received data is not in the 8b/10b tables. The data received on bytes marked by rxnotintable is the raw 10-bit d...

Page 115

Virtex-4 rocketio mgt user guide www.Xilinx.Com 115 ug076 (v4.1) november 2, 2008 8b/10b encoding/decoding r non-standard running disparity example to support other protocols, the transceiver can affect the disparity mode of the serial data transmitted. For example, vitesse channel-to-channel alignm...

Page 116

116 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r symbol alignment and detection (comma detection) summary in addition to 8/10-bit symbol alignment detection, the rocketio mgt has been expanded to detect and align to 32-b...

Page 117

Virtex-4 rocketio mgt user guide www.Xilinx.Com 117 ug076 (v4.1) november 2, 2008 symbol alignment and detection (comma detection) r 8-bit / 10-bit alignment the mcomma_32b_value, pcomma_32b_value, comma_10b_mask, and comma32 attributes determine the symbols the comma detection block uses to align d...

Page 118

118 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r therefore: • for 1-byte fabric width, rxcommadet is four rxusrclk2 cycles wide. • for 2-byte fabric width, rxcommadet is two rxusrclk2 cycles wide. • for 4-byte fabric wid...

Page 119

Virtex-4 rocketio mgt user guide www.Xilinx.Com 119 ug076 (v4.1) november 2, 2008 symbol alignment and detection (comma detection) r sonet alignment virtex-4 mgts support bit and byte alignment for sonet a1a2 transitions for line rates of oc12 (12 a1s followed by 12 a2s). The sonet aligner operates ...

Page 120

120 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r figure 3-16 shows the same process, but for a 16-bit external data interface width. The ports and attributes in table 3-11 and table 3-12 define the proper configuration f...

Page 121

Virtex-4 rocketio mgt user guide www.Xilinx.Com 121 ug076 (v4.1) november 2, 2008 symbol alignment and detection (comma detection) r although the sonet aligner is affected only by the enpcommaalign port, the enmcommaalign port must also be turned off; otherwise, the byte aligner realigns any time an...

Page 122

122 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r alignment status when sonet alignment is selected via comma32=true, the rxrealign and rxcommadet status flags indicate the status only of the sonet aligner. Status of symb...

Page 123: Clock Correction

Virtex-4 rocketio mgt user guide www.Xilinx.Com 123 ug076 (v4.1) november 2, 2008 clock correction r rxslide rxslide allows manual control of the pcs barrel shifter for applications that require an alignment function that cannot be defined with pcomma_32b_value/ mcomma_32b_value. When rxslide is set...

Page 124

124 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r there are a few attributes that need to be set by the user so that the append/remove function can be used correctly. The attribute clk_cor_max_lat sets the maximum latency...

Page 125

Virtex-4 rocketio mgt user guide www.Xilinx.Com 125 ug076 (v4.1) november 2, 2008 clock correction r table 3-15 is an example of data 11-bit attribute setting, the character value, charisk value, and the parallel data interface, and how each corresponds with the other. Clk_cor_seq_1_mask, clk_cor_se...

Page 126

126 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r in some cases, more than two clock correction sequences can be defined in a protocol. For this case, the clk_cor_seq_mask attributes can “mask” portions of the sequence. F...

Page 127: Channel Bonding

Virtex-4 rocketio mgt user guide www.Xilinx.Com 127 ug076 (v4.1) november 2, 2008 channel bonding r channel bonding channel bonding is the technique of tying several serial channels together to create one aggregate channel. Several channels are fed on the transmit side by one parallel bus and reprod...

Page 128

128 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r outside the limits of the clk_cor_min_lat and clk_cor_max_lat attributes. Channel bond operations are blocked while clock correction requests are pending. While servicing ...

Page 129

Virtex-4 rocketio mgt user guide www.Xilinx.Com 129 ug076 (v4.1) november 2, 2008 channel bonding r bond characters should be spaced more than 36 bytes + chan_bond_limit at least once. • the receivers must not be receiving the fixed channel bond sequence when rxreset is deasserted or enchansync is a...

Page 130

130 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r chan_bond_seq_1_mask, chan_bond_seq_2_mask, chan_bond_seq_len, chan_bond_seq_ * _ * attributes these attributes operate exactly the same as their clock correction counterp...

Page 131

Virtex-4 rocketio mgt user guide www.Xilinx.Com 131 ug076 (v4.1) november 2, 2008 channel bonding r in figure 3-21 , the two slave_1_hops are linked to the master in only one direction. To navigate to the other slave (a slave_2_hops), both x and y displacement is needed. This slave needs one level o...

Page 132: Status and Event Bus

132 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r rx fabric interface and channel bonding when channel bonding is used, rxreset must be deasserted synchronously on all channel-bonded mgts. This is because of the way the f...

Page 133: Loopback

Virtex-4 rocketio mgt user guide www.Xilinx.Com 133 ug076 (v4.1) november 2, 2008 loopback r event indication four types of events can occur. See table 3-23 . When an event occurs, it can override a status indication. An event can only last for one clock and can be signaled by rxstatus[5] being set ...

Page 134: Digital Receiver

134 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r enable serial loopback by setting loopback[1:0] to 11 . The txpost_tap_pd bit must also be set to 0 . This can be set in the drp at address 0x4c , bit 12 for mgta, and at ...

Page 135

Virtex-4 rocketio mgt user guide www.Xilinx.Com 135 ug076 (v4.1) november 2, 2008 digital receiver r • digital receiver output clock = 1x clock = 124.4 ÷ 8 (sampling rate) = 15.55 mhz (line rate/parallel data width) in addition to the 1x clock, the digital receiver can also generate a 4x and 2x cloc...

Page 136

136 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r clocking in buffered mode figure 3-24 shows the various clock domains in the mgt. The ring buffer aligns the pcs rxclk domain and rxusrclk domain. The rxusrclk domain and ...

Page 137

Virtex-4 rocketio mgt user guide www.Xilinx.Com 137 ug076 (v4.1) november 2, 2008 digital receiver r rxclk0_force_pmaclk true: the pma rxclk0 drives the pcs rxclk. Digrx_sync_mode false: phase aligner circuit is disabled. Rx_clock_divider sets rxusrclk rate. Pcs rxclk is driven by the pma rxclk0 (1x...

Page 138

138 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 3: pcs digital design considerations r.

Page 139: Serial I/o Description

Virtex-4 rocketio mgt user guide www.Xilinx.Com 139 ug076 (v4.1) november 2, 2008 r chapter 4 pma analog design considerations serial i/o description the rocketio multi-gigabit transceiver (mgt) transmits and receives serial differential signals, using a nominal termination supply voltage of 1.5 vdc...

Page 140

140 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r emphasis the mgt contains a 3-tap transmitter (shown in figure 4-2 ). This allows a data driver, pre- cursor driver, and post-cursor driver to help create a cleaner signal ...

Page 141

Virtex-4 rocketio mgt user guide www.Xilinx.Com 141 ug076 (v4.1) november 2, 2008 output swing and emphasis r and also to preserve the subsequent pulse of the next bit being transmitted in an actual system. Table 4-2 shows the recommended txdat_tap_dac and txpost_tap_dac settings for a range of diff...

Page 142

142 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r the txpre_tap_dac value can be set to some fraction of the txpost_tap_dac value. However, for most channels, txpre_tap_dac can be set to off, unless it is required to impro...

Page 143

Virtex-4 rocketio mgt user guide www.Xilinx.Com 143 ug076 (v4.1) november 2, 2008 output swing and emphasis r figure 4-4: tx with minimal pre-emphasis u g076_ch4_17.Ep s.

Page 144

144 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r figure 4-5: rx after 36 inches fr4 and minimal pre-emphasis u g076_ch4_1 8 .Ep s.

Page 145

Virtex-4 rocketio mgt user guide www.Xilinx.Com 145 ug076 (v4.1) november 2, 2008 output swing and emphasis r figure 4-6: tx with maximal pre-emphasis u g076_ch4_19.Ep s.

Page 146: Differential Receiver

146 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r differential receiver the differential receiver accepts the v p and v n signals, carrying out the difference calculation v p -v n electronically. All input data must be dif...

Page 147

Virtex-4 rocketio mgt user guide www.Xilinx.Com 147 ug076 (v4.1) november 2, 2008 differential receiver r at 1/32 nd and 1/40 th the incoming data rate depending on mode. A sufficient number of transitions must be present in the data stream for cdr to work properly. The cdr circuit is guaranteed to ...

Page 148

148 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r figure 4-8: ac response of continuous-time linear receiver equalizer 2.0 0.0 6.0 4.0 10 12 14 8 .0 freq ( hz ) ac re s pon s e 10m 100m 1g 10g rxafeeq = 111 rxafeeq = 011 r...

Page 149: Special Analog Functions

Virtex-4 rocketio mgt user guide www.Xilinx.Com 149 ug076 (v4.1) november 2, 2008 special analog functions r special analog functions out-of-band (oob) signals several protocols including serial ata and pci express implement oob signals, which are essentially low-frequency signals when compared to n...

Page 150

150 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r table 4-6 explains the usage of attributes fdet_hys_cal/rxfdet_hys_cal and fdet_lck_cal/rxfdet_lck_cal during calibration, and of attributes fdet_hys_sel/rxfdet_hys_sel and...

Page 151

Virtex-4 rocketio mgt user guide www.Xilinx.Com 151 ug076 (v4.1) november 2, 2008 special analog functions r powerdown powerdown, rxpd, and txpd are used to reduce power. Table 4-7 through table 4-9 show the definitions of powerdown, rxpd, and txpd. Powerdown is a single-bit primitive port (see tabl...

Page 152

152 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 4: pma analog design considerations r table 4-10 summarizes the attributes that power down the various tx pma blocks. When one of the listed attributes is asserted true, the indicated tx pma block(s) are powere...

Page 153

Virtex-4 rocketio mgt user guide www.Xilinx.Com 153 ug076 (v4.1) november 2, 2008 r chapter 5 cyclic redundancy check (crc) each rocketio mgt has two 32-bit crc blocks. The input data path width can be 1 to 8 bytes and can be changed on each clock cycle to allow the computation of a crc of any data ...

Page 154

154 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 5: cyclic redundancy check (crc) r txcrcdatavalid i 1 signals that the txcrcin data is valid when set to logic 1. Txcrcdatawidth i 3 determines the data width of the txcrcin. Txcrcin i 64 transmitter crc logic ...

Page 155: Functionality

Virtex-4 rocketio mgt user guide www.Xilinx.Com 155 ug076 (v4.1) november 2, 2008 functionality r functionality the 32-bit crc block is a crc generator using the following polynomial: g(x) = x 32 + x 26 + x 23 + x 22 + x 16 + x 12 + x 11 + x 10 + x 8 + x 7 + x 5 + x 4 + x 2 + x + 1. An important fea...

Page 156

156 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 5: cyclic redundancy check (crc) r for the different data widths, data in is always left-aligned within the 64-bit input data interface. For example, using a 32-bit data width would indicate data is transmitted...

Page 157: Latency and Timing

Virtex-4 rocketio mgt user guide www.Xilinx.Com 157 ug076 (v4.1) november 2, 2008 handling end-of-packet residue r handling end-of-packet residue if the data width changes, as in the case of end-of-packet residue (shown in figure 5-3 ), the crcdatawidth must be changed to correspond to the actual da...

Page 158

158 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 5: cyclic redundancy check (crc) r after wakeup of the crc, crcreset has to be asserted for at least two crcclk clock cycles. When crcreset is deasserted, the user should wait two crcclk clock cycles before sta...

Page 159

Virtex-4 rocketio mgt user guide www.Xilinx.Com 159 ug076 (v4.1) november 2, 2008 latency and timing r 3 2-bit example crcintclk and crcclk data are the same rate internally. The crcout rate is always the same as the crcin rate. This is shown in figure 5-4 . Figure 5-4: max data rate example (32-bit...

Page 160

160 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 5: cyclic redundancy check (crc) r 16-bit transmission, hold crc, and residue of 8-bit example in this example ( figure 5-5 ), data is 16 bits wide and the method for holding the crcout value is shown. This exa...

Page 161: Implementation

Virtex-4 rocketio mgt user guide www.Xilinx.Com 161 ug076 (v4.1) november 2, 2008 implementation r implementation the mgt crc blocks do not recognize start-of-frame (sof/sop) and end-of-frame (eof/eop), nor do they decode crc error conditions; this functionality must be implemented in the fpga fabri...

Page 162

162 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 5: cyclic redundancy check (crc) r.

Page 163: Analog and Board Design

Virtex-4 rocketio mgt user guide www.Xilinx.Com 163 ug076 (v4.1) november 2, 2008 r chapter 6 analog and board design considerations physical requirements to ensure reliable operation of the virtex®-4 rocketio™ mgt, the designer must meet certain requirements. This section outlines the requirements ...

Page 164

164 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r figure 6-1: mgt tile power and serial i/o pins pc s , control a nd config u r a tion v ccint avccauxrx avccauxrxb avccauxmgt avccauxtx vtrxa vttxa vttxb vtrxb rxap tx...

Page 165

Virtex-4 rocketio mgt user guide www.Xilinx.Com 165 ug076 (v4.1) november 2, 2008 physical requirements r power supply re q uirements the virtex-4 data sheet should be used for power consumption specifications for an mgt tile. Determining power supply budget due to the shared transmitter resources, ...

Page 166

166 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r note: placing a virtex-4 rocketio mgt in power-down mode does not disconnect the termination network; current draw from the v trx and v ttx pins continues to occur. A...

Page 167

Virtex-4 rocketio mgt user guide www.Xilinx.Com 167 ug076 (v4.1) november 2, 2008 physical requirements r note: figure 6- 3 shows the power supply circuit only. See figure 6-4 for the mgt power filtering network. Figure 6-5 shows an example layout. In most cases v ttx = v trx , but receive terminati...

Page 168

168 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r powering unused mgts important: all mgts in the fpga, whether instantiated in the design or not, must be connected to power and ground. Unused mgts should be connecte...

Page 169

Virtex-4 rocketio mgt user guide www.Xilinx.Com 169 ug076 (v4.1) november 2, 2008 physical requirements r number of power pins that must be filtered. Several conditions require that the power supply be filtered: • the gt11clk_mgt of a tile is used. • the synclk1 or synclk2 pass through a tile to rea...

Page 170

170 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r reference clock because a high degree of accuracy is required from the reference clock, an epson eg2121ca 2.5v oscillator should be used. (visit the epson electronics...

Page 171

Virtex-4 rocketio mgt user guide www.Xilinx.Com 171 ug076 (v4.1) november 2, 2008 physical requirements r for details, refer to the vectron website . The termination resistors are provided inside the fpga. Ac coupling caps are required on the gt11clk_mgt or gt11clk inputs. The common mode for these ...

Page 172

172 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r high side, low side, and differential (floating or active). This configuration supports receiver termination compatible to virtex-ii pro rocketio transceiver, using a...

Page 173

Virtex-4 rocketio mgt user guide www.Xilinx.Com 173 ug076 (v4.1) november 2, 2008 physical requirements r the internal ac coupling provides a high-pass filter with a corner frequency of 40.8 khz. Figure 6-12 shows the capacitor value as 6.5 pf and the resistance as 600 k Ω . See the rxdccouple attri...

Page 174

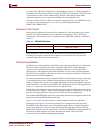

174 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r selectio-to-mgt crosstalk since it is possible that mgt performance can degrade in an environment flooded with selectio™ activity, it is important to have guidelines ...

Page 175

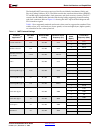

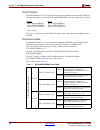

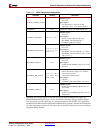

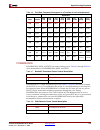

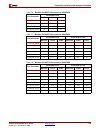

Virtex-4 rocketio mgt user guide www.Xilinx.Com 175 ug076 (v4.1) november 2, 2008 physical requirements r table 6-3: selectio pin guidance for xc4vfx60/40/20-ff672 mgt pair 1mm 1.4mm core via fx60 fx40 fx20 mgt_102 c23, c24, d24 c19, c21, c22 – k20, k21 k20, l19 mgt_103 p24, u24, v24 j24, l24, n24, ...

Page 176

176 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r high-speed serial trace design routing serial traces because jtag is not available on serial i/o pins, all mgt i/os are placed on the periphery of the bga package to ...

Page 177

Virtex-4 rocketio mgt user guide www.Xilinx.Com 177 ug076 (v4.1) november 2, 2008 high-speed serial trace design r all signal traces must have an intact reference plane beneath them. Stripline and microstrip geometries can be used. The reference plane should extend no less than five trace widths to ...

Page 178

178 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 6: analog and board design considerations r figure 6-15: obstacle route geometry figure 6-16: microstrip edge-coupled differential pair figure 6-17: stripline edge-coupled differential pair 45° bend z 0 = 50 Ω ...

Page 179: Model Considerations

Virtex-4 rocketio mgt user guide www.Xilinx.Com 179 ug076 (v4.1) november 2, 2008 r chapter 7 simulation and implementation model considerations the rocketio™ mgt swift model simulates the pll in the same fashion as in the virtex®-ii pro device. To save simulation time, the pll locks much faster tha...

Page 180

180 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 7: simulation and implementation r hspice hspice is a simulation model for the analog portions of the mgt design. To obtain these hspice models, go to the spice suite access web page at: http://support.Xilinx.C...

Page 181

Virtex-4 rocketio mgt user guide www.Xilinx.Com 181 ug076 (v4.1) november 2, 2008 smartmodel simulation considerations r out-of-band (oob) signaling out-of-band signaling is said to occur when txp and txn are driven to a common-mode voltage indicating “electrical idle” for protocols such as pci-expr...

Page 182

182 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 7: simulation and implementation r simulating in verilog the global set/reset (gsr) and global 3-state (gts) signals are defined in the $xilinx/verilog/src/glbl.V module. The glbl.V module connects the global s...

Page 183

Virtex-4 rocketio mgt user guide www.Xilinx.Com 183 ug076 (v4.1) november 2, 2008 smartmodel simulation considerations r i : in std_logic; o : out std_logic ); end component; begin u1 : rocbuf port map (i => srp, o => gsr); //dummy process counter : process (clock, enable,reset) begin ……………………………… …...

Page 184

184 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 7: simulation and implementation r phase-locked loop the txabpmaclksel and txpllndivsel attributes are present in both mgta and mgtb instantiations. However, due to the physical nature of a single tx pll, only ...

Page 185

Virtex-4 rocketio mgt user guide www.Xilinx.Com 185 ug076 (v4.1) november 2, 2008 smartmodel simulation considerations r user_8b_rx_data [31:24] → rx_data [7:0] user_8b_rx_data [23:16] → rx_data [15:8] user_8b_rx_data [15:8] → rx_data [23:16] user_8b_rx_data [7:0] → rx_data [31:24] mgt ports that ca...

Page 186

186 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 7: simulation and implementation r transceiver location and package pin relation mgt package pins the mgt is a hard core placed in the fpga fabric. All package pins for the mgts are dedicated on the virtex-4 fx...

Page 187

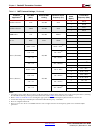

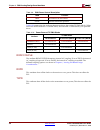

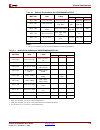

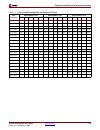

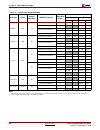

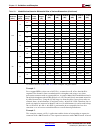

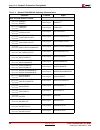

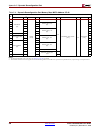

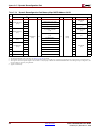

Virtex-4 rocketio mgt user guide www.Xilinx.Com 187 ug076 (v4.1) november 2, 2008 transceiver location and package pin relation r table 7-4: loc grid and package pins correlation for ff1152 loc constraint xc4vfx40-ff1152 xc4vfx60-ff1152 xc4vfx100-ff1152 mgt txp txn rxp rxn mgt txp txn rxp rxn mgt tx...

Page 188

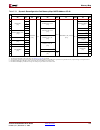

188 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 7: simulation and implementation r table 7-5: loc grid and package pins correlation for ff1517 loc constraint xc4vfx100-ff1517 xc4vfx140-ff1517 mgt txp txn rxp rxn mgt txp txn rxp rxn gt11_x0y0 106b aw25 aw24 a...

Page 189

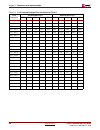

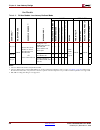

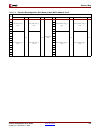

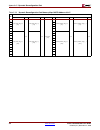

Virtex-4 rocketio mgt user guide www.Xilinx.Com 189 ug076 (v4.1) november 2, 2008 transceiver location and package pin relation r table 7-6: bonded out mgtclk sources for xc4vfx20 loc constraint xc4vfx20-ff672 mgtclk clkn clkp gt11clk_x0y0 105 af20 af21 gt11clk_x0y1 102 g26 f26 gt11clk_x1y0 110 af11...

Page 190

190 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 7: simulation and implementation r table 7-9: bonded out mgtclk sources for xc4vfx100 loc constraint xc4vfx100-ff1152 xc4vfx100-ff1517 mgtclk clkn clkp mgtclk clkn clkp gt11clk_x0y0 – – – – – – gt11clk_x0y1 105...

Page 191: Low-Latency Design

Virtex-4 rocketio mgt user guide www.Xilinx.Com 191 ug076 (v4.1) november 2, 2008 r chapter 8 low-latency design introduction the virtex®-4 rocketio™ multi-gigabyte transceiver (mgt) has the flexibility to minimize latency in the pcs. The rocketio transceiver contains two buffers, one for the transm...

Page 192

192 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r pcs clocking domains and data paths note: in this chapter, all references to unit intervals (ui) are in relation to the serial bit time. Receiver refer to figure 8-1 . If the shortest pa...

Page 193

Virtex-4 rocketio mgt user guide www.Xilinx.Com 193 ug076 (v4.1) november 2, 2008 pcs clocking domains and data paths r transmitter refer to figure 8-2 . On the transmit side, the only blocks to consider are the fabric interface (one txusrclk2 cycle and one txusrclk cycle), pma registers (one pma tx...

Page 194: Pcs Data Path Latency

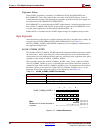

194 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r pcs data path latency the relationship between usrclk and usrclk2 (both tx and rx) depends on several factors, including the fabric interface width and the serial standard used. Another ...

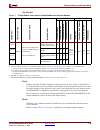

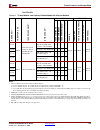

Page 195

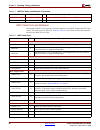

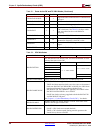

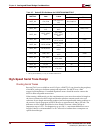

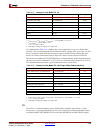

Virtex-4 rocketio mgt user guide www.Xilinx.Com 195 ug076 (v4.1) november 2, 2008 pcs data path latency r table 8-2: latency through various transmitter components/processes (1) transmit blocks 1 byte 2 byte 4 byte 8 byte fabric interface (2) 4 txusrclk2 + 1 txusrclk 2 txusrclk2 + 1 txusrclk 1 txusr...

Page 196: Ports and Attributes

196 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r ports and attributes receiver table 8-3: rx low-latency ports (1) ports description loopback(0) determines clock source for pma rxclk0 domain in conjunction with rx_clock_divider and rxc...

Page 197

Virtex-4 rocketio mgt user guide www.Xilinx.Com 197 ug076 (v4.1) november 2, 2008 synchronizing the pma/pcs clocks in low-latency modes r transmitter synchronizing the pma/pcs clocks in low-latency modes the txsync and rxsync ports are used to enable low-latency modes by activating the phase-alignme...

Page 198

198 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r transmit latency and output skew the channel-to-channel transmit output skew is an important concern for many channel- bonding applications. Many traditional serdes products manage this ...

Page 199

Virtex-4 rocketio mgt user guide www.Xilinx.Com 199 ug076 (v4.1) november 2, 2008 transmit latency and output skew r use models skew without using the txsync alignment circuitry, the native skew of the a and b mgts is 4 ui. Because the reset of the parallel clock dividers in the transmit data path o...

Page 200

200 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r tx low latency buffered mode with channel deskew overview for this mode, the txsync functionality is required to synchronize the pcs and pma clocks across all channels that need to be de...

Page 201

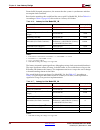

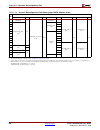

Virtex-4 rocketio mgt user guide www.Xilinx.Com 201 ug076 (v4.1) november 2, 2008 transmit latency and output skew r use models table 8-8: tx use models: low-latency buffered mode with channel deskew us e m o de l (1 ) tx_b uffe r_us e txusr c lk sour ce (2) by p a ss mo d e (5 ) ports attributes tx...

Page 202

202 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r use models tx_1a–tx_1d without channel deskew and tx_2a–tx_2d with channel deskew, txusrclk from txusrclk2 figure 8-4 shows the buffered-mode flow through the tx using the 10gbase-r enco...

Page 203

Virtex-4 rocketio mgt user guide www.Xilinx.Com 203 ug076 (v4.1) november 2, 2008 transmit latency and output skew r figure 8-5 shows the buffered-mode flow through the tx using the 8b/10b encoder. Figure 8-5: tx low latency buffered mode: use models tx_1b, tx_2b 10gba s e-r encode (1) 8 b/10b encod...

Page 204

204 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r figure 8-6 shows the buffered-mode flow through the tx bypassing the 10gbase-r gearbox and 64b/66b scrambler. Figure 8-6: tx low latency buffered mode: use models tx_1c, tx_2c 10gba s e-...

Page 205

Virtex-4 rocketio mgt user guide www.Xilinx.Com 205 ug076 (v4.1) november 2, 2008 transmit latency and output skew r figure 8-7 shows the buffered-mode flow through the tx bypassing 8b/10b encoding, 10gbase-r encoding, 10gbase-r gearbox, and 64b/66b scrambler. Figure 8-7: tx low latency buffered mod...

Page 206

206 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r use models tx_2e–tx_2h with channel deskew, external txusrclk figure 8-8 shows the buffered-mode flow through the tx using the 10gbase-r encoder, 10gbase-r gearbox, and 64b/66b scrambler...

Page 207

Virtex-4 rocketio mgt user guide www.Xilinx.Com 207 ug076 (v4.1) november 2, 2008 transmit latency and output skew r figure 8-9 shows the buffered-mode flow through the tx using the 8b/10b encoder. Figure 8-9: tx low latency buffered mode: use model tx_2f 10gba s e-r encode (1) 8 b/10b encode 8 x40 ...

Page 208

208 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r figure 8-10 shows the buffered-mode flow through the tx bypassing the 10gbase-r gearbox and 64b/66b scrambler. Figure 8-10: tx low latency buffered mode: use model tx_2g 10gba s e-r enco...

Page 209

Virtex-4 rocketio mgt user guide www.Xilinx.Com 209 ug076 (v4.1) november 2, 2008 transmit latency and output skew r figure 8-11 shows the buffered-mode flow through the tx bypassing 8b/10b encoding, 10gbase-r encoding, 10gbase-r gearbox, and 64b/66b scrambler. Skew see section “tx channel skew usin...

Page 210

210 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r tx low latency buffer bypass mode overview for this mode, the tx buffer is bypassed and txsync must be used to synchronize the pcs txclk and pma txclk0. In this case, the phase alignment...

Page 211

Virtex-4 rocketio mgt user guide www.Xilinx.Com 211 ug076 (v4.1) november 2, 2008 transmit latency and output skew r use models table 8-9: tx use models: low-latency buffer bypass w/out channel deskew use model (1 ) tx_b uffer_use txusrclk source (2) byp a ss mode ports (6) attributes txenc8b10b use...

Page 212

212 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r use models tx_ 3 a and tx 3 b figure 8-13 shows the buffer bypass mode flow through the tx using 8b/10b encoding. Figure 8-13: tx low latency buffer bypass mode: use model tx_3a 10gba s ...

Page 213: Txsync

Virtex-4 rocketio mgt user guide www.Xilinx.Com 213 ug076 (v4.1) november 2, 2008 txsync r figure 8-14 shows the full pcs bypass flow through the tx. Skew see section “tx channel skew using txsync,” page 215 . Reset refer to section “resets” in chapter 2 for more details. Txsync overview the pma pha...

Page 214

214 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r synchronous clock divider setting (32-bit or 40-bit data path). The circuit adjusts one high- speed clock for every parallel clock being used as the timing reference (grefclk or pcs txcl...

Page 215

Virtex-4 rocketio mgt user guide www.Xilinx.Com 215 ug076 (v4.1) november 2, 2008 tx channel skew using txsync r c. If multiple txsync pulses are necessary, it is also recommended that they be spaced at least four synchronization clock cycles apart. D. If txsync is left asserted, it acts as an enabl...

Page 216

216 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r 2-byte: 32-bit internal datapath: 16ui 40-bit internal datapath: 20ui 1-byte: 32-bit internal datapath: 24ui 40-bit internal datapath: 30ui skew pkg is the worst-case package skew betwee...

Page 217

Virtex-4 rocketio mgt user guide www.Xilinx.Com 217 ug076 (v4.1) november 2, 2008 tx channel skew using txsync r tx skew estimation examples all examples assume 4-byte fabric width and 40-bit internal datapath. 1.25 gbit/s, synchronization clock = pcs txclk, txphasesel = true 1.25 gbit/s, synchroniz...

Page 218

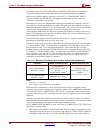

218 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r table 8-10: worst-case skew estimates data rate ui (ps) internal data path txusrclk source fabric data width synchronization clock pcs txclk grefclk ui (ns) ui (ns) 622 mb/s 1608 32 inte...

Page 219: Rx Latency

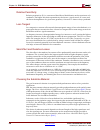

Virtex-4 rocketio mgt user guide www.Xilinx.Com 219 ug076 (v4.1) november 2, 2008 rx latency r rx latency to minimize the latency in the rx, the phase discrepancy between the pcs rxclk and pma rxclk0 can be minimized by the rx phase alignment circuitry. This allows the user to bypass portions of the...

Page 220

220 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r use models table 8-11: rx use models: low-latency buffered mode use model (1) rx_b uffer_use rxu s rc lk sourc e (2) byp a ss mode ( 3 ) ports attributes rxb l oc ksync64b66b use rxc o m...

Page 221

Virtex-4 rocketio mgt user guide www.Xilinx.Com 221 ug076 (v4.1) november 2, 2008 rx latency r use models rx_1a, rx_1b, and rx_1c figure 8-16 shows the buffered mode flow through the rx using 64b/66b decoding and block sync. Figure 8-16: rx low latency buffered mode: use model rx_1a 13x64 b it ring ...

Page 222

222 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r figure 8-17 shows the buffered mode flow through the rx using 8b/10b decoding. Figure 8-17: rx low latency buffered mode: use model rx_1b 13x64 b it ring b u ffer 8 b/10b decode 10gba s ...

Page 223

Virtex-4 rocketio mgt user guide www.Xilinx.Com 223 ug076 (v4.1) november 2, 2008 rx latency r figure 8-18 shows the buffered mode flow through the rx bypassing 8b/10b and 64b/66b decoding. Reset rxreset should be synchronized across channels to ensure that all the rx buffer pointers are in phase wi...

Page 224

224 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r rx low latency buffer bypass mode overview for this mode, the rx buffer is bypassed and rxsync must be used to synchronize the pcs rxclk and pma rxclk0. The pcx rxclk is used as the sync...

Page 225

Virtex-4 rocketio mgt user guide www.Xilinx.Com 225 ug076 (v4.1) november 2, 2008 rx latency r use models rx_2a, rx_2b, and rx_2c figure 8-19 shows the buffer bypass mode flow through the rx using 8b/10b decoding. Figure 8-19: rx low latency buffer bypass mode: use model rx_2a 13x64 b it ring b u ff...

Page 226

226 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r figure 8-20 shows the buffer bypass mode flow through the rx bypassing 8b/10b and 64b/66b decoding but retaining comma detection. Figure 8-20: rx low latency buffer bypass mode: use mode...

Page 227

Virtex-4 rocketio mgt user guide www.Xilinx.Com 227 ug076 (v4.1) november 2, 2008 rx latency r figure 8-21 shows the full pcs bypass flow through the rx, bypassing comma detection as well as decoding. Reset refer to section “resets” in chapter 2 for more details. Figure 8-21: rx low latency buffer b...

Page 228: Rxsync

228 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r rxsync overview the pma phase alignment block compares and then synchronizes the phase relationship between pma rxclk0 and the pcs rxclk. The phase alignment circuit is enabled by the ri...

Page 229

Virtex-4 rocketio mgt user guide www.Xilinx.Com 229 ug076 (v4.1) november 2, 2008 restrictions on low latency buffer bypass modes r 2. Rx phase alignment should not be initiated until all involved rx plls are locked. Refer to section “resets” in chapter 2 for more details . Depending on the rx pll s...

Page 230

230 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r example of a reduced-latency system xaui system characteristics • 3.125 gb/s data rate • 156.25 mhz reference clock • 4-lane channel-bonded system • 40-bit internal data width • 2-byte f...

Page 231

Virtex-4 rocketio mgt user guide www.Xilinx.Com 231 ug076 (v4.1) november 2, 2008 example of a reduced-latency system r as summarized in table 8-15 , a further step a user might take is to go to a 4-byte fabric interface. This would reduce the fabric interface latency and the skew. User logic can st...

Page 232

232 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 8: low-latency design r from the rx datapath perspective, this ensures that the system is synchronous and does not require clock correction. Based on the encoding, this would lead the user to pick use model rx_...

Page 233: Section Ii:

R section ii: board level design virtex-4 rocketio multi-gigabit transceiver.

Page 234

Virtex-4 rocketio mgt user guide www.Xilinx.Com ug076 (v4.1) november 2, 2008.

Page 235: Methodology Overview

Virtex-4 rocketio mgt user guide www.Xilinx.Com 235 ug076 (v4.1) november 2, 2008 r chapter 9 methodology overview introduction xilinx, in partnership with dr. Howard johnson, has developed a two-part dvd tutorial on signal integrity techniques and loss budgeting for rocketio transceivers. [ref 2] t...

Page 236: Powering The Rocketio Mgts

236 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 9: methodology overview r • the impedance mismatch (to 50 Ω ) of a transition which can lead to reflections, attenuation, and other artifacts in the signal. At gigahertz signaling speeds, losses due to the tran...

Page 237: Coupling

Virtex-4 rocketio mgt user guide www.Xilinx.Com 237 ug076 (v4.1) november 2, 2008 coupling r when considering alternate clock sources, the alternate oscillators must meet or exceed the specifications of the recommended oscillators. As with the regulator, allowances should be made for both recommende...

Page 238

238 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 9: methodology overview r frequency component in a coded stream is the longest run length allowed by the encoding scheme. Large value capacitors have larger body sizes, which can introduce sufficient shunt capa...

Page 239: Pcb Materials and Traces

Virtex-4 rocketio mgt user guide www.Xilinx.Com 239 ug076 (v4.1) november 2, 2008 r chapter 10 pcb materials and traces the choice of pcb materials and cable type can have a large impact on system performance. Although any transmission medium is lossy at gigahertz frequencies, this section provides ...

Page 240

240 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 10: pcb materials and traces r relative permittivity relative permittivity (e r ) is a measure of the effect of the dielectric on the capacitance of a conductor. The higher the relative permittivity, the slower...

Page 241: Traces

Virtex-4 rocketio mgt user guide www.Xilinx.Com 241 ug076 (v4.1) november 2, 2008 traces r for less dense applications, it might be possible to use a more traditional material such as fr4, yet achieve lower loss by using wider lines. However, this is more often true in lower data rate applications. ...

Page 242

242 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 10: pcb materials and traces r the same w/s ratio also must be less than 0.8, otherwise strong coupling between the traces requires narrower, lossier traces for a z 0o of 50 Ω . If an impedance-checking tool is...

Page 243

Virtex-4 rocketio mgt user guide www.Xilinx.Com 243 ug076 (v4.1) november 2, 2008 traces r characteristic impedance requirement. Alternatively, some manufacturers are willing to compute the initial line widths. A good pcb manufacturer understands controlled impedance and allows fine adjustments for ...

Page 244: Cable

244 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 10: pcb materials and traces r once a verified configuration is obtained, begin by modeling the configuration in the frequency domain by doing an ac sweep, and plot transmission line loss versus frequency. If t...

Page 245: Design of Transitions

Virtex-4 rocketio mgt user guide www.Xilinx.Com 245 ug076 (v4.1) november 2, 2008 r chapter 11 design of transitions transmission lines have defined and controlled characteristic impedance along their length by definition. However, the transitions — i.E., the three-dimensional structures to which th...

Page 246

246 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 11: design of transitions r the magnitude of this excess capacitance (c) or inductance (l) can also be extracted from the tdr waveform by integrating the normalized area of the transition’s tdr response. The re...

Page 247: Smt Pads

Virtex-4 rocketio mgt user guide www.Xilinx.Com 247 ug076 (v4.1) november 2, 2008 smt pads r the results using these equations are not sensitive to rise time variation and are valid for simulated tdr measurements provided that the leading and trailing transmission lines are very close to 50 Ω . Howe...

Page 248

248 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 11: design of transitions r the 2d field solver example shows that close to 50 Ω can be achieved if the ground plane under the pad footprint is cleared out. A 3d field solver is then used to verify this result ...

Page 249

Virtex-4 rocketio mgt user guide www.Xilinx.Com 249 ug076 (v4.1) november 2, 2008 smt pads r next, using simulated measurements on the same transition modeled in hfss, the time- domain performance of this transition can be measured by doing a tdr on the s-parameter results from the earlier frequency...

Page 250: Differential Vias

250 www.Xilinx.Com virtex-4 rocketio mgt user guide ug076 (v4.1) november 2, 2008 chapter 11: design of transitions r differential vias the most common transition is the differential via where the signal pair must transition from an upper stripline layer or top microstrip to a lower stripline layer ...

Page 251

Virtex-4 rocketio mgt user guide www.Xilinx.Com 251 ug076 (v4.1) november 2, 2008 differential vias r from the graph in figure 11-12 , the common-mode return loss (scc11) is about 20 db worse when compared to differential return loss (sdd11). The much worse common-mode response relative to the diffe...