- DL manuals

- Xilinx

- Motherboard

- ZC706

- User manual

Xilinx ZC706 User manual

Summary of ZC706

Page 1

Zc706 evaluation board for the zynq-7000 xc7z045 all programmable soc user guide ug954 (v1.5) september 10, 2015.

Page 2: Revision History

Zc706 evaluation board user guide www.Xilinx.Com 2 ug954 (v1.5) september 10, 2015 notice of disclaimer the information disclosed to you hereunder (the “materials”) is provided solely for the selection and use of xilinx products. To the maximum extent permitted by applicable law: (1) materials are m...

Page 3

Zc706 evaluation board user guide www.Xilinx.Com 3 ug954 (v1.5) september 10, 2015 04/24/2013 1.2 chapter 1, zc706 evaluation board features : table 1-1 feature descriptions are now linked to their respective sections in the book. Figure 1-2 , figure 1-33 , and figure 1-34 were replaced. Table 1-2 w...

Page 4

Zc706 evaluation board user guide www.Xilinx.Com 4 ug954 (v1.5) september 10, 2015 table of contents revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 chapter 1: zc706 evaluation board features o...

Page 5

Zc706 evaluation board user guide www.Xilinx.Com 5 ug954 (v1.5) september 10, 2015 switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62 power on/off slide switch . . . . . . . . . ...

Page 6

Zc706 evaluation board user guide www.Xilinx.Com 6 ug954 (v1.5) september 10, 2015 standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114 electromagnetic compatibility . . . . . . . . . . . . . . . . ....

Page 7: Overview

Zc706 evaluation board user guide www.Xilinx.Com 7 ug954 (v1.5) september 10, 2015 chapter 1 zc706 evaluation board features overview the zc706 evaluation board for the xc7z045 all programmable soc (ap soc) provides a hardware environment for developing and evaluating designs targeting the zynq®-700...

Page 8

Zc706 evaluation board user guide www.Xilinx.Com 8 ug954 (v1.5) september 10, 2015 overview • gtx transceivers ° fmc hpc connector (eight gtx transceivers) ° fmc lpc connector (one gtx transceiver) ° sma connectors (one pair each for tx, rx and refclk) ° pci express (four lanes) ° small form-factor ...

Page 9

Zc706 evaluation board user guide www.Xilinx.Com 9 ug954 (v1.5) september 10, 2015 overview ° fmc power good ° 12v input power on ° fpga init ° fpga done • user i/o: ° four (pl) user leds ° three (pl) user pushbuttons ° one (pl) user dip switch (4-pole) ° two dual row pmod gpio headers • ap soc ps r...

Page 10: Block Diagram

Zc706 evaluation board user guide www.Xilinx.Com 10 ug954 (v1.5) september 10, 2015 overview block diagram the zc706 evaluation board block diagram is shown in figure 1-1 . Board layout figure 1-2 shows the zc706 evaluation board. Each numbered feature that is referenced in figure 1-2 is described i...

Page 11

Zc706 evaluation board user guide www.Xilinx.Com 11 ug954 (v1.5) september 10, 2015 overview x-ref target - figure 1-2 figure 1-2: zc706 evaluation board component locations 17 6 30 31 21 18 15 2 11 13 12 1 4 7 3 9 10 16 25 24 26 22 33 27 19 32 23 28 14 35 29 5 8 20 34 36 37 38 00 square callout ref...

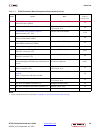

Page 12

Zc706 evaluation board user guide www.Xilinx.Com 12 ug954 (v1.5) september 10, 2015 overview 8 programmable user clock, page 35 i 2 c prog. User clock 3.3v lvds (u37, bottom of board) silicon labs si570bab0000544dg, default 156.250 mhz 34 9 user sma clock source, page 36 user differential sma clock ...

Page 13

Zc706 evaluation board user guide www.Xilinx.Com 13 ug954 (v1.5) september 10, 2015 overview 24 gpio dip switch, page 60 gpio dip switch (sw12) 4-pole c&k sda04h1sbd 38 25 arm® core pjtag header (j64) 2x10 0.1inch male header, samtec tst-110-01-g-d 39 26 user pmod gpio headers, page 60 pmod headers ...

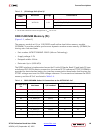

Page 14: Feature Descriptions

Zc706 evaluation board user guide www.Xilinx.Com 14 ug954 (v1.5) september 10, 2015 feature descriptions feature descriptions detailed information for each feature shown in figure 1-2 and listed in table 1-1 is provided in this section. Zynq-7000 xc7z045 ap soc [ figure 1-2 , callout 1] the zc706 ev...

Page 15

Zc706 evaluation board user guide www.Xilinx.Com 15 ug954 (v1.5) september 10, 2015 feature descriptions for additional information on zynq-7000 soc devices, see zynq-7000 all programmable soc overview ( ds190 ) and zynq-7000 all programmable soc technical reference manual ( ug585 ). Device configur...

Page 16

Zc706 evaluation board user guide www.Xilinx.Com 16 ug954 (v1.5) september 10, 2015 feature descriptions • pl configuration: usb jtag configuration port (digilent module u30) • pl configuration: platform cable header j3 and flying lead header j62 jtag configuration ports tip: designs using serial co...

Page 17

Zc706 evaluation board user guide www.Xilinx.Com 17 ug954 (v1.5) september 10, 2015 feature descriptions i/o voltage rails there are eleven i/o banks available on the xc7z045 ap soc. The voltages applied to the xc7z045 ap soc i/o banks used by the zc706 evaluation board are listed in table 1-3 . X-r...

Page 18: Ddr3 Sodimm Memory (Pl)

Zc706 evaluation board user guide www.Xilinx.Com 18 ug954 (v1.5) september 10, 2015 feature descriptions ddr3 sodimm memory (pl) [ figure 1-2 , callout 2] the memory module at j1 is a 1 gb ddr3 small outline dual-inline memory module (sodimm). It provides volatile synchronous dynamic random access m...

Page 19

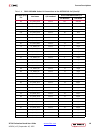

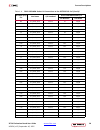

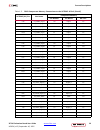

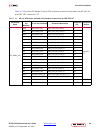

Zc706 evaluation board user guide www.Xilinx.Com 19 ug954 (v1.5) september 10, 2015 feature descriptions d6 pl_ddr3_a10 sstl15 107 a10/ap b7 pl_ddr3_a11 sstl15 84 a11 h12 pl_ddr3_a12 sstl15 83 a12_bc_n a10 pl_ddr3_a13 sstl15 119 a13 g11 pl_ddr3_a14 sstl15 80 a14 c6 pl_ddr3_a15 sstl15 78 a15 f8 pl_dd...

Page 20

Zc706 evaluation board user guide www.Xilinx.Com 20 ug954 (v1.5) september 10, 2015 feature descriptions b4 pl_ddr3_d26 sstl15 67 dq26 b5 pl_ddr3_d27 sstl15 69 dq27 a3 pl_ddr3_d28 sstl15 56 dq28 b1 pl_ddr3_d29 sstl15 58 dq29 c1 pl_ddr3_d30 sstl15 68 dq30 c4 pl_ddr3_d31 sstl15 70 dq31 k10 pl_ddr3_d32...

Page 21

Zc706 evaluation board user guide www.Xilinx.Com 21 ug954 (v1.5) september 10, 2015 feature descriptions b11 pl_ddr3_d61 sstl15 182 dq61 c14 pl_ddr3_d62 sstl15 192 dq62 b14 pl_ddr3_d63 sstl15 194 dq63 j3 pl_ddr3_dm0 sstl15 11 dm0 f2 pl_ddr3_dm1 sstl15 28 dm1 e1 pl_ddr3_dm2 sstl15 46 dm2 c2 pl_ddr3_d...

Page 22: Ddr3 Component Memory (Ps)

Zc706 evaluation board user guide www.Xilinx.Com 22 ug954 (v1.5) september 10, 2015 feature descriptions the zc706 ddr3 sodimm interface adheres to the constraints guidelines documented in the “dynamic memory” section of the zynq-7000 all programmable soc pcb design and pin planning guide ( ug933 )....

Page 23

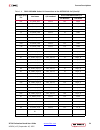

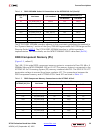

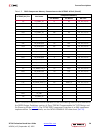

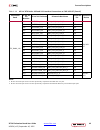

Zc706 evaluation board user guide www.Xilinx.Com 23 ug954 (v1.5) september 10, 2015 feature descriptions c28 ps_ddr3_dq11 c8 dq11 u3 d30 ps_ddr3_dq12 e3 dq12 u3 a30 ps_ddr3_dq13 e8 dq13 u3 d29 ps_ddr3_dq14 d2 dq14 u3 d28 ps_ddr3_dq15 e7 dq15 u3 h27 ps_ddr3_dq16 b3 dq16 u4 g27 ps_ddr3_dq17 c7 dq17 u4...

Page 24

Zc706 evaluation board user guide www.Xilinx.Com 24 ug954 (v1.5) september 10, 2015 feature descriptions the zc706 ddr3 component interface adheres to the constraints guidelines documented in the ddr3 design guidelines section of zynq-7000 all programmable soc pcb design and pin planning guide ( ug9...

Page 25: Quad-Spi Flash Memory

Zc706 evaluation board user guide www.Xilinx.Com 25 ug954 (v1.5) september 10, 2015 feature descriptions quad-spi flash memory [ figure 1-2 , callout 4] the quad-spi flash memory located at u58 and u59 provides 2 x 128 mb of nonvolatile storage that can be used for configuration and data storage. • ...

Page 26

Zc706 evaluation board user guide www.Xilinx.Com 26 ug954 (v1.5) september 10, 2015 feature descriptions x-ref target - figure 1-6 figure 1-6: 128 mb quad-spi flash memory dq3_hold_b vcc nc0 nc1 nc2 nc3 s_b dq1 c714 0.1uf 25v x5r c dq0 nc7 nc6 nc5 nc4 vss dq2_vpp_wp_b 16 15 14 13 12 11 10 9 qspi0_io...

Page 27: Usb 2.0 Ulpi Transceiver

Zc706 evaluation board user guide www.Xilinx.Com 27 ug954 (v1.5) september 10, 2015 feature descriptions usb 2.0 ulpi transceiver [ figure 1-2 , callout 19] the zc706 evaluation board uses a standard microsystems corporation usb3320 usb 2.0 ulpi transceiver at u12 to support a usb connection to the ...

Page 28

Zc706 evaluation board user guide www.Xilinx.Com 28 ug954 (v1.5) september 10, 2015 feature descriptions the connections between the usb micro-b connector at j2 and the phy at u12 are listed in table 1-8 . The connections between the usb 2.0 phy at u12 and the xc7z045 ap soc are listed in table 1-9 ...

Page 29: Sd Card Interface

Zc706 evaluation board user guide www.Xilinx.Com 29 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-7 shows the usb 2.0 ulpi transceiver circuitry. Note that the shield for the usb micro-b connector (j2) can be tied to gnd by a jumper on header j51 pins 1–2 (default). The usb shield ca...

Page 30

Zc706 evaluation board user guide www.Xilinx.Com 30 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-8 shows the connections of the sd card interface on the zc706 evaluation board. Table 1-10 lists the sd card interface connections to the xc7z045 ap soc x-ref target - figure 1-8 figure ...

Page 31

Zc706 evaluation board user guide www.Xilinx.Com 31 ug954 (v1.5) september 10, 2015 feature descriptions programmable logic jtag programming options [ figure 1-2 , callout 6] the zc706 evaluation board jtag chain is shown in figure 1-9 . Programmable logic jtag select switch [ figure 1-2 , callout 3...

Page 32

Zc706 evaluation board user guide www.Xilinx.Com 32 ug954 (v1.5) september 10, 2015 feature descriptions dip switch sw4[1:2] setting 10 selects the 14-pin header j3 for configuration using either a parallel cable iv (pc4) or platform cable usb ii. Dip switch sw4 setting 01 selects the usb-to-jtag di...

Page 33: Clock Generation

Zc706 evaluation board user guide www.Xilinx.Com 33 ug954 (v1.5) september 10, 2015 feature descriptions fmc connector jtag bypass when an fpga mezzanine card (fmc) is attached to hpc j37 or lpc j5 it is automatically added to the jtag chain through electronically controlled single-pole single-throw...

Page 34

Zc706 evaluation board user guide www.Xilinx.Com 34 ug954 (v1.5) september 10, 2015 feature descriptions table 1-13 lists the pin-to-pin connections from each clock source to the xc7z045 ap soc. System clock [ figure 1-2 , callout 7] table 1-12: zc706 evaluation board clock sources clock name clock ...

Page 35

Zc706 evaluation board user guide www.Xilinx.Com 35 ug954 (v1.5) september 10, 2015 feature descriptions the system clock source is an lvds 200 mhz oscillator at u64. It is wired to a multi-region clock capable (mrcc) input on programmable logic (pl) bank 34. The signal pair is named sysclk_p and sy...

Page 36

Zc706 evaluation board user guide www.Xilinx.Com 36 ug954 (v1.5) september 10, 2015 feature descriptions the user clock circuit is shown in figure 1-12 . See the silicon labs si570 data sheet [ref 21] . User sma clock source the zc706 board provides a pair of smas for differential user clock input i...

Page 37

Zc706 evaluation board user guide www.Xilinx.Com 37 ug954 (v1.5) september 10, 2015 feature descriptions processing system clock source the processing system (ps) clock source is a 1.8v lvcmos single-ended fixed 33.33333 mhz oscillator at u24. It is wired to ps bank 500, pin a22 (ps_clk), on the xc7...

Page 38

Zc706 evaluation board user guide www.Xilinx.Com 38 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-15 shows this ac-coupled clock circuit. Jitter attenuated clock [ figure 1-2 , callout 11] the zc706 board includes a silicon labs si5324 jitter attenuator u60 on the back side of the bo...

Page 39: Gtx Transceivers

Zc706 evaluation board user guide www.Xilinx.Com 39 ug954 (v1.5) september 10, 2015 feature descriptions see the silicon labs si5324 data sheet [ref 21] . Gtx transceivers [ figure 1-2 , callout 12] the zc706 board provides access to 16 gtx transceivers: • four of the gtx transceivers are wired to t...

Page 40

Zc706 evaluation board user guide www.Xilinx.Com 40 ug954 (v1.5) september 10, 2015 feature descriptions • one gtx transceiver is unused and is wired in a capacitively coupled tx-to-rx loopback configuration the gtx transceivers in zynq-7000 series ap socs are grouped into four channels described as...

Page 41

Zc706 evaluation board user guide www.Xilinx.Com 41 ug954 (v1.5) september 10, 2015 feature descriptions table 1-14 lists the gtx banks 109 and 110 interface connections between the ap soc u1 and fmc hpc connector j37. Table 1-14: ap soc gtx banks 109 and 110 interface connections to fmc hpc j37 tra...

Page 42

Zc706 evaluation board user guide www.Xilinx.Com 42 ug954 (v1.5) september 10, 2015 feature descriptions gtx_bank_110 ah2 mgtptxp0_110 fmc_hpc_dp4_c2m_p a34 fmc hpc j37 ah1 mgtptxn0_110 fmc_hpc_dp4_c2m_n a35 ah6 mgtprxp0_110 fmc_hpc_dp4_m2c_p a14 ah5 mgtprxn0_110 fmc_hpc_dp4_m2c_n a15 af2 mgtptxp1_1...

Page 43

Zc706 evaluation board user guide www.Xilinx.Com 43 ug954 (v1.5) september 10, 2015 feature descriptions table 1-15 lists the gtx bank interface connections between the ap soc u1 and fmc lpc connector j5. For additional information on zynq-7000 gtx transceivers, see 7 series fpgas gtx/gth transceive...

Page 44

Zc706 evaluation board user guide www.Xilinx.Com 44 ug954 (v1.5) september 10, 2015 feature descriptions pci express endpoint connectivity [ figure 1-2 , callout 13] the 4-lane pci express edge connector performs data transfers at the rate of 2.5 gt/s for a gen1 application and 5.0 gt/s for a gen2 a...

Page 45

Zc706 evaluation board user guide www.Xilinx.Com 45 ug954 (v1.5) september 10, 2015 feature descriptions table 1-17 lists the gtx bank 112 interface connections between the ap soc u1 and pcie 4-lane connector p4. For additional information about zynq-7000 pcie functionality, see 7 series fpgas integ...

Page 46: Sfp/sfp+ Module Connector

Zc706 evaluation board user guide www.Xilinx.Com 46 ug954 (v1.5) september 10, 2015 feature descriptions sfp/sfp+ module connector [ figure 1-2 , callout 14] the zc706 board contains a small form-factor pluggable (sfp/sfp+) connector and cage assembly p2 that accepts sfp or sfp+ modules. Figure 1-19...

Page 47

Zc706 evaluation board user guide www.Xilinx.Com 47 ug954 (v1.5) september 10, 2015 feature descriptions table 1-18 lists the sfp+ module control and status connections to the ap soc. For additional information about the enhanced small form factor pluggable (sfp+) module, see the sff-8431 specificat...

Page 48

Zc706 evaluation board user guide www.Xilinx.Com 48 ug954 (v1.5) september 10, 2015 feature descriptions the ethernet connections from the xc7z045 ap soc at u1 to the 88e1116r phy device at u51 are listed in table 1-20 . Ethernet phy clock source a 25.00 mhz 50 ppm crystal at x1 is the clock source ...

Page 49: Usb-to-Uart Bridge

Zc706 evaluation board user guide www.Xilinx.Com 49 ug954 (v1.5) september 10, 2015 feature descriptions the data sheet can be obtained under nda with marvell. Contact information can be found at their website [ref 24] . For additional information on the zynq-7000 ap soc device gigabit ethernet cont...

Page 50: Hdmi Video Output

Zc706 evaluation board user guide www.Xilinx.Com 50 ug954 (v1.5) september 10, 2015 feature descriptions table 1-22 lists the usb connections between the xc7z045 ap soc ps bank 501 and the cp2103 uart bridge. Refer to the silicon labs website for technical information on the cp2103gm and the vcp dri...

Page 51

Zc706 evaluation board user guide www.Xilinx.Com 51 ug954 (v1.5) september 10, 2015 feature descriptions • i 2 c • spdif figure 1-21 shows the hdmi codec circuit. X-ref target - figure 1-21 figure 1-21: hdmi codec circuit ug954_c1_21_041113 gnd gnd vcc3v3 gnd gnd oe gnd out vcc d31 d32 d33 d34 d35 d...

Page 52

Zc706 evaluation board user guide www.Xilinx.Com 52 ug954 (v1.5) september 10, 2015 feature descriptions table 1-23 lists the connections between the codec and the xc7z045 ap soc. Table 1-23: xc7z045 ap soc u1 to hdmi codec connections (adv7511) xc7z045 (u1) pin net name i/o standard adv7511 (u53) p...

Page 53: I2C Bus

Zc706 evaluation board user guide www.Xilinx.Com 53 ug954 (v1.5) september 10, 2015 feature descriptions table 1-24 lists the connections between the codec and the hdmi receptacle p1. Information about the adv7511kstz-p is available on the analog devices website [ref 25] . For additional information...

Page 54

Zc706 evaluation board user guide www.Xilinx.Com 54 ug954 (v1.5) september 10, 2015 feature descriptions the zc706 evaluation board i 2 c bus topology is shown in figure 1-22 . User applications that communicate with devices on one of the downstream i 2 c buses must first set up a path to the desire...

Page 55: Real Time Clock (Rtc)

Zc706 evaluation board user guide www.Xilinx.Com 55 ug954 (v1.5) september 10, 2015 feature descriptions real time clock (rtc) the epson rtc-8564je (u26) is an i 2 c bus interface real-time clock that has a built-in 32.768 khz oscillator with these features: • frequency output options: 32.768 khz, 1...

Page 56: Status and User Leds

Zc706 evaluation board user guide www.Xilinx.Com 56 ug954 (v1.5) september 10, 2015 feature descriptions status and user leds table 1-27 defines the status and user leds. Table 1-27: status leds reference designator net name led color description ds1 por red processor system power-on reset is active...

Page 57: Ethernet Phy User Leds

Zc706 evaluation board user guide www.Xilinx.Com 57 ug954 (v1.5) september 10, 2015 feature descriptions ethernet phy user leds [ figure 1-2 , callout 21] the three ethernet phy user leds shown in figure 1-24 are located near the rj45 ethernet jack p3. The on/off state for each led is software depen...

Page 58

Zc706 evaluation board user guide www.Xilinx.Com 58 ug954 (v1.5) september 10, 2015 feature descriptions ° gpio_dip_sw[3:0] sw12 • two user gpio male pin headers (callout 26 ) • 2 x 6 0.1 in. Pitch pmod1 j57 • 2 x 6 0.1 in. Pitch pmod2 j58 user leds [ figure 1-2 , callout 22] the zc706 evaluation bo...

Page 59

Zc706 evaluation board user guide www.Xilinx.Com 59 ug954 (v1.5) september 10, 2015 feature descriptions user pushbuttons [ figure 1-2 , callout 23] figure 1-26 shows the user pushbutton circuits. Table 1-29 lists the user pushbutton connections to xc7z045 ap soc u1. X-ref target - figure 1-26 figur...

Page 60

Zc706 evaluation board user guide www.Xilinx.Com 60 ug954 (v1.5) september 10, 2015 feature descriptions gpio dip switch figure 1-27 shows the gpio dip switch circuit. Table 1-30 lists the gpio dip switch connections to xc7z045 ap soc u1. User pmod gpio headers [ figure 1-2 , callout 26] the zc706 e...

Page 61

Zc706 evaluation board user guide www.Xilinx.Com 61 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-28 shows the user gpio male pin header circuits. X-ref target - figure 1-28 figure 1-28: user gpio headers pmod1_0_ls pmod1_1_ls pmod1_2_ls pmod1_3_ls pmod1_4_ls pmod1_5_ls pmod1_6_ls pm...

Page 62: Switches

Zc706 evaluation board user guide www.Xilinx.Com 62 ug954 (v1.5) september 10, 2015 feature descriptions table 1-31 lists the gpio header connections to xc7z045 ap soc u1. See zynq-7000 all programmable soc technical reference manual ( ug585 ) for information about the ps pjtag functionality. Switch...

Page 63

Zc706 evaluation board user guide www.Xilinx.Com 63 ug954 (v1.5) september 10, 2015 feature descriptions caution! Do not plug a pc atx power supply 6-pin connector into j22 on the zc706 evaluation board. The atx 6-pin connector has a different pinout than j22. Connecting an atx 6-pin connector into ...

Page 64

Zc706 evaluation board user guide www.Xilinx.Com 64 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-31 shows sw10. Ps power-on and system reset pushbuttons figure 1-32 shows the reset circuitry for the processing system. Depressing and then releasing pushbutton sw1 causes ps_por_b_sw t...

Page 65

Zc706 evaluation board user guide www.Xilinx.Com 65 ug954 (v1.5) september 10, 2015 feature descriptions depressing and then releasing pushbutton sw3 causes ps_srst_b_sw (connected to the xc7z045 ap soc u1 dedicated ps bank 500 pin d21) to strobe low. Ps_srst_b: this reset is used to force a system ...

Page 66

Zc706 evaluation board user guide www.Xilinx.Com 66 ug954 (v1.5) september 10, 2015 feature descriptions • 8 gtx transceivers • 2 gtx clocks • 2 differential clocks • 159 ground and 15 power connections the zc706 board v adj voltage for the j37 and j5 connectors is determined by the fmc v adj power ...

Page 67

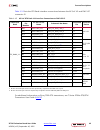

Zc706 evaluation board user guide www.Xilinx.Com 67 ug954 (v1.5) september 10, 2015 feature descriptions c14 fmc_hpc_la10_p lvcmos25 ag24 d12 fmc_hpc_la05_n lvcmos25 ah24 c15 fmc_hpc_la10_n lvcmos25 ag25 d14 fmc_hpc_la09_p lvcmos25 ad21 c18 fmc_hpc_la14_p lvcmos25 ac24 d15 fmc_hpc_la09_n lvcmos25 ae...

Page 68

Zc706 evaluation board user guide www.Xilinx.Com 68 ug954 (v1.5) september 10, 2015 feature descriptions e27 nc n/a n/a f26 nc n/a n/a e28 nc n/a n/a f28 nc n/a n/a e30 nc n/a n/a f29 nc n/a n/a e31 nc n/a n/a f31 nc n/a n/a e33 nc n/a n/a f32 nc n/a n/a e34 nc n/a n/a f34 nc n/a n/a e36 nc n/a n/a ...

Page 69

Zc706 evaluation board user guide www.Xilinx.Com 69 ug954 (v1.5) september 10, 2015 feature descriptions lpc connector j5 [ figure 1-2 , callout 31] the 160-pin lpc connector defined by the fmc specification ( figure b-1, page 90 ) provides connectivity for up to: h38 fmc_hpc_la32_n lvcmos25 r21 h40...

Page 70

Zc706 evaluation board user guide www.Xilinx.Com 70 ug954 (v1.5) september 10, 2015 feature descriptions • 68 single-ended or 34 differential user-defined signals • 1 gtx transceiver • 1 gtx clock • 2 differential clocks • 61 ground and 10 power connections the connections between the hpc connector ...

Page 71

Zc706 evaluation board user guide www.Xilinx.Com 71 ug954 (v1.5) september 10, 2015 feature descriptions c39 vcc3v3 n/a n/a d31 fmc_lpc_tdo_fpga_tdi n/a u31.2 d32 vcc3v3 n/a n/a d33 fmc_lpc_tms_buf n/a u23.16 d34 nc n/a n/a d35 ga1 = 0 = gnd n/a n/a d36 vcc3v3 n/a n/a d38 vcc3v3 n/a n/a d40 vcc3v3 n...

Page 72: Zc706 Board Power System

Zc706 evaluation board user guide www.Xilinx.Com 72 ug954 (v1.5) september 10, 2015 feature descriptions zc706 board power system the zc706 board hosts a power system based on the texas instruments (ti) ucd90120a power supply sequencer and monitor, and the lmz31500 and lmz31700 family voltage regula...

Page 73

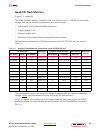

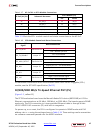

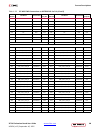

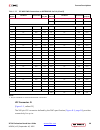

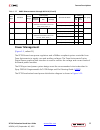

Zc706 evaluation board user guide www.Xilinx.Com 73 ug954 (v1.5) september 10, 2015 feature descriptions table 1-34 shows the zc706 board ti power system configuration for controller u48. Table 1-34: zc706 ti controller u48 power system configuration sequencer schematic page regulator type, u# volta...

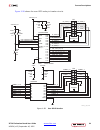

Page 74

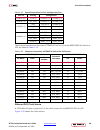

Zc706 evaluation board user guide www.Xilinx.Com 74 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-33 shows the power system for ucd90120a u48 controller. X-ref target - figure 1-33 figure 1-33: zc706 ti ucd90120a controller u48 power system sense connected at point of load gpio (out)...

Page 75

Zc706 evaluation board user guide www.Xilinx.Com 75 ug954 (v1.5) september 10, 2015 feature descriptions the lmz31520, lmz31506, and lmz31710 adjustable voltage regulators have their output voltage set through an external resistor. The regulator topology on the zc706 board permits the ti ucd90120a m...

Page 76

Zc706 evaluation board user guide www.Xilinx.Com 76 ug954 (v1.5) september 10, 2015 feature descriptions figure 1-34 shows the xadc external mux block diagram. See table 1-35 which lists the zc706 xadc power system voltage and current measurement details for the external mux u6. X-ref target - figur...

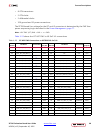

Page 77: Power Management

Zc706 evaluation board user guide www.Xilinx.Com 77 ug954 (v1.5) september 10, 2015 feature descriptions power management [ figure 1-2 , callout 32] the zc706 board uses power regulators and a pmbus-compliant system controller from texas instruments to supply core and auxiliary voltages. The texas i...

Page 78

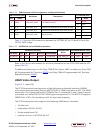

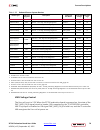

Zc706 evaluation board user guide www.Xilinx.Com 78 ug954 (v1.5) september 10, 2015 feature descriptions the zc706 evaluation board uses power regulators and pmbus compliant pwm system controllers from texas instruments to supply the core and auxiliary voltages listed in table 1-36 . X-ref target - ...

Page 79

Zc706 evaluation board user guide www.Xilinx.Com 79 ug954 (v1.5) september 10, 2015 feature descriptions vadj voltage control the v adj rail is set to 2.5v. When the zc706 evaluation board is powered on, the state of the fmc_vadj_on_b signal wired to header j18 is sampled by the ti ucd90120a control...

Page 80

Zc706 evaluation board user guide www.Xilinx.Com 80 ug954 (v1.5) september 10, 2015 feature descriptions because the rail turn on decision is made at power on time based on the presence of the j18 jumper, removing the jumper at j18 after the board is powered up does not affect the 2.5v power deliver...

Page 81

Zc706 evaluation board user guide www.Xilinx.Com 81 ug954 (v1.5) september 10, 2015 feature descriptions associated ti fusion digital power designer gui (downloadable from the ti site [ref 28] . This is the simplest and most convenient way to monitor the voltage and current values for the power rail...

Page 82

Zc706 evaluation board user guide www.Xilinx.Com 82 ug954 (v1.5) september 10, 2015 feature descriptions cooling fan the xc7z045 ap soc cooling fan connector is shown in figure 1-36 . When v adj is modified from a default of 2.5v to 1.8v or a lower v adj setting, the ap soc u1 cooling fan turns off....

Page 83

Zc706 evaluation board user guide www.Xilinx.Com 83 ug954 (v1.5) september 10, 2015 feature descriptions aa19 respectively, enabling the user to implement their own fan speed control ip in the ap soc pl logic. More information about the power system components used by the zc706 evaluation board are ...

Page 84

Zc706 evaluation board user guide www.Xilinx.Com 84 ug954 (v1.5) september 10, 2015 feature descriptions the zc706 evaluation board supports both the internal xc7z045 ap soc sensor measurements and the external measurement capabilities of the xadc. Internal measurements of the die temperature, vccin...

Page 85

Zc706 evaluation board user guide www.Xilinx.Com 85 ug954 (v1.5) september 10, 2015 feature descriptions gnd 16 digital ground (board) reference xadc_gpio_3, 2, 1, 0 19, 20, 17, 18 digital i/o. These pins should come from the same bank. These ios should not be shared with other functions because the...

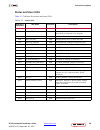

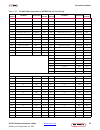

Page 86: Switches

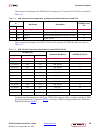

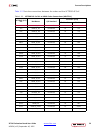

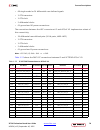

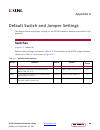

Zc706 evaluation board user guide www.Xilinx.Com 86 ug954 (v1.5) september 10, 2015 appendix a default switch and jumper settings the default switch and jumper settings for the zc706 evaluation board are provided in this appendix. Switches [ figure 1-2 , callout 24] default switch settings are liste...

Page 87: Jumpers

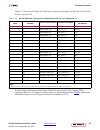

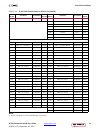

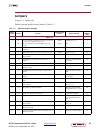

Zc706 evaluation board user guide www.Xilinx.Com 87 ug954 (v1.5) september 10, 2015 jumpers jumpers [ figure 1-2 , callout 24] default jumper positions are listed in table a-2 . Table a-2: default jumper settings jumper callout jumper function default jumper position option selected schematic 038151...

Page 88

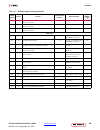

Zc706 evaluation board user guide www.Xilinx.Com 88 ug954 (v1.5) september 10, 2015 jumpers 18 j72 mio select header mio4 (note: dip sw11 pole 3 affects this signal) 1-2 qspi0_io4 = mio2_select 15 19 j73 mio select header mio5 (note: dip sw11 pole 4 affects this signal) 1-2 qspi0_io5 = mio2_select 1...

Page 89

Zc706 evaluation board user guide www.Xilinx.Com 89 ug954 (v1.5) september 10, 2015 jumpers x-ref target - figure a-1 figure a-1: zc706 jumper header locations ug954_aa_01_042415 34 33 11 24 25 23 4 13 32 7 1 8 31 9 30 10 15 12 14 5 26 28 6 29 27 2 3 21 22 16 17 18 19 20 send feedback.

Page 90

Zc706 evaluation board user guide www.Xilinx.Com 90 ug954 (v1.5) september 10, 2015 appendix b vita 57.1 fmc connector pinouts figure b-1 shows the pinout of the fpga mezzanine card (fmc) low pin count (lpc) connector defined by the vita 57.1 fmc specification. For a description of how the zc706 eva...

Page 91

Zc706 evaluation board user guide www.Xilinx.Com 91 ug954 (v1.5) september 10, 2015 x-ref target - figure b-2 figure b-2: fmc hpc connector pinout ug954_ab_02_100112 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 vref_b_m2c gnd gnd clk2...

Page 92

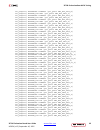

Zc706 evaluation board user guide www.Xilinx.Com 92 ug954 (v1.5) september 10, 2015 appendix c master constraints file listing the master xilinx design constraints (xdc) file template for the zc706 board provides for designs targeting the zc706 evaluation board. Net names in the constraints listed b...

Page 93

Zc706 evaluation board user guide www.Xilinx.Com 93 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin ad20 [get_ports rec_clock_c_p] set_property iostandard lvds_25 [get_ports rec_clock_c_p] set_property package_pin aj25 [get_ports si5324_int_alms] set_prope...

Page 94

Zc706 evaluation board user guide www.Xilinx.Com 94 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin ad10 [get_ports fmc_hpc_gbtclk0_m2c_c_p] set_property package_pin aa7 [get_ports fmc_hpc_gbtclk1_m2c_c_n] set_property package_pin aa8 [get_ports fmc_hpc_gb...

Page 95

Zc706 evaluation board user guide www.Xilinx.Com 95 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property iostandard lvcmos25 [get_ports fmc_hpc_la12_n] set_property package_pin af23 [get_ports fmc_hpc_la12_p] set_property iostandard lvcmos25 [get_ports fmc_hpc_la12_p] set_...

Page 96

Zc706 evaluation board user guide www.Xilinx.Com 96 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property iostandard lvcmos25 [get_ports fmc_hpc_la25_p] set_property package_pin t28 [get_ports fmc_hpc_la26_n] set_property iostandard lvcmos25 [get_ports fmc_hpc_la26_n] set_p...

Page 97

Zc706 evaluation board user guide www.Xilinx.Com 97 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing #la set_property package_pin af13 [get_ports fmc_lpc_la00_cc_n] set_property iostandard lvcmos25 [get_ports fmc_lpc_la00_cc_n] set_property package_pin ae13 [get_ports fmc_lpc_la00_...

Page 98

Zc706 evaluation board user guide www.Xilinx.Com 98 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin ah16 [get_ports fmc_lpc_la13_n] set_property iostandard lvcmos25 [get_ports fmc_lpc_la13_n] set_property package_pin ah17 [get_ports fmc_lpc_la13_p] set_pro...

Page 99

Zc706 evaluation board user guide www.Xilinx.Com 99 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin aj30 [get_ports fmc_lpc_la26_p] set_property iostandard lvcmos25 [get_ports fmc_lpc_la26_p] set_property package_pin aj29 [get_ports fmc_lpc_la27_n] set_pro...

Page 100

Zc706 evaluation board user guide www.Xilinx.Com 100 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin g2 [get_ports gpio_led_center] set_property iostandard lvcmos15 [get_ports gpio_led_center] set_property package_pin y21 [get_ports gpio_led_left] set_prop...

Page 101

Zc706 evaluation board user guide www.Xilinx.Com 101 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin ae30 [get_ports hdmi_r_d20] set_property iostandard lvcmos25 [get_ports hdmi_r_d20] set_property package_pin y25 [get_ports hdmi_r_d21] set_property iostan...

Page 102

Zc706 evaluation board user guide www.Xilinx.Com 102 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin t5 [get_ports pcie_rx1_n] set_property package_pin t6 [get_ports pcie_rx1_p] set_property package_pin u3 [get_ports pcie_rx2_n] set_property package_pin u4...

Page 103

Zc706 evaluation board user guide www.Xilinx.Com 103 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin l1 [get_ports pl_ddr3_d0] set_property iostandard sstl15 [get_ports pl_ddr3_d0] set_property package_pin l2 [get_ports pl_ddr3_d1] set_property iostandard ...

Page 104

Zc706 evaluation board user guide www.Xilinx.Com 104 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin b5 [get_ports pl_ddr3_d27] set_property iostandard sstl15 [get_ports pl_ddr3_d27] set_property package_pin a3 [get_ports pl_ddr3_d28] set_property iostanda...

Page 105

Zc706 evaluation board user guide www.Xilinx.Com 105 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin d14 [get_ports pl_ddr3_d54] set_property iostandard sstl15 [get_ports pl_ddr3_d54] set_property package_pin b17 [get_ports pl_ddr3_d55] set_property iostan...

Page 106

Zc706 evaluation board user guide www.Xilinx.Com 106 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing set_property package_pin l8 [get_ports pl_ddr3_dqs4_p] set_property iostandard diff_sstl15 [get_ports pl_ddr3_dqs4_p] set_property package_pin f12 [get_ports pl_ddr3_dqs5_n] set_pr...

Page 107

Zc706 evaluation board user guide www.Xilinx.Com 107 ug954 (v1.5) september 10, 2015 zc706 evaluation board xdc listing #sfp set_property package_pin y5 [get_ports sfp_rx_n] set_property package_pin y6 [get_ports sfp_rx_p] set_property package_pin w3 [get_ports sfp_tx_n] set_property package_pin w4 ...

Page 108

Zc706 evaluation board user guide www.Xilinx.Com 108 ug954 (v1.5) september 10, 2015 appendix d board setup installing the zc706 board in a pc chassis installation of the zc706 board inside a computer chassis is required when developing or testing pci express® functionality. When the zc706 board is ...

Page 109

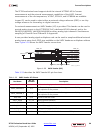

Zc706 evaluation board user guide www.Xilinx.Com 109 ug954 (v1.5) september 10, 2015 installing the zc706 board in a pc chassis 7. The zc706 board is taller than standard pcie cards. Ensure that the height of the card is free of obstructions. 8. Connect the atx power supply to the zc706 board using ...

Page 110: Dimensions

Zc706 evaluation board user guide www.Xilinx.Com 110 ug954 (v1.5) september 10, 2015 appendix e board specifications dimensions height 5.5 inch (14.0 cm) length 10.5 inch (26.7 cm) note: the zc706 board height exceeds the standard 4.376 inch (11.15 cm) height of a pci express card. Environmental tem...

Page 111: Xilinx Resources

Zc706 evaluation board user guide www.Xilinx.Com 111 ug954 (v1.5) september 10, 2015 appendix f additional resources xilinx resources for support resources such as answers, documentation, downloads, and forums, see the xilinx support website . For continual updates, add the answer record to your mya...

Page 112

Zc706 evaluation board user guide www.Xilinx.Com 112 ug954 (v1.5) september 10, 2015 references 5. 7 series fpgas configuration user guide ( ug470 ) 6. 7 series fpgas gtx/gth transceivers user guide ( ug476 ) 7. 7 series fpgas integrated block for pci express product guide for vivado design suite ( ...

Page 113

Zc706 evaluation board user guide www.Xilinx.Com 113 ug954 (v1.5) september 10, 2015 references 26. Texas instruments: www.Ti.Com , www.Ti.Com/fusiondocs (ucd90120a, lmz31506, lmz31520, lmz31710, lmz31704, tps54291pwp, tps51200dr, pca9548, tca641apwr, txs0108e) 27. Texas instruments: www.Ti.Com/xili...

Page 114: Overview

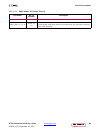

Zc706 evaluation board user guide www.Xilinx.Com 114 ug954 (v1.5) september 10, 2015 appendix g regulatory and compliance information overview this product is designed and tested to conform to the european union directives and standards described in this section. Refer to the zynq-7000 ap soc zc706 ...

Page 115: Safety

Zc706 evaluation board user guide www.Xilinx.Com 115 ug954 (v1.5) september 10, 2015 markings electromagnetic compatibility en 55022:2010, information technology equipment radio disturbance characteristics – limits and methods of measurement en 55024:2010, information technology equipment immunity c...