- DL manuals

- Xilinx

- Processor

- Zynq-7000

- User Manual

Xilinx Zynq-7000 User Manual - Core Architecture

Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1

90

UG586 November 30, 2016

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

10. Run implementation flow with the Vivado tool. For details about implementation, see

the Vivado Design Suite User Guide: Designing with IP (UG896)

.

Note:

Similar steps can be followed for the user design using appropriate .dcp and .xdc files.

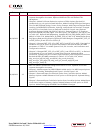

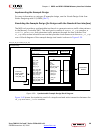

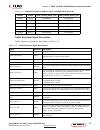

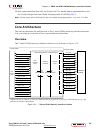

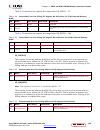

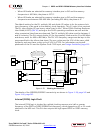

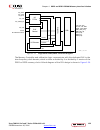

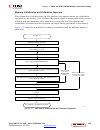

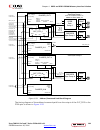

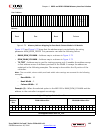

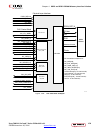

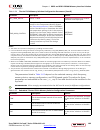

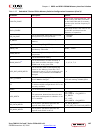

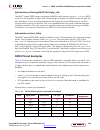

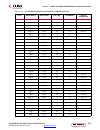

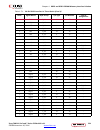

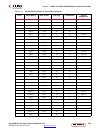

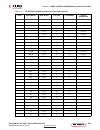

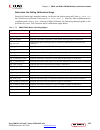

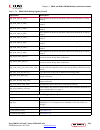

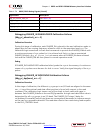

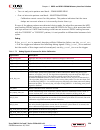

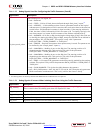

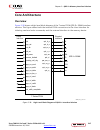

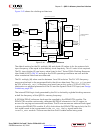

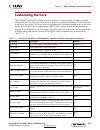

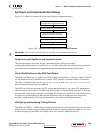

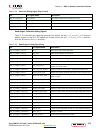

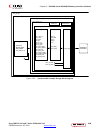

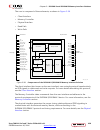

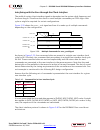

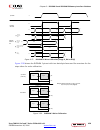

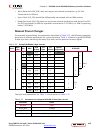

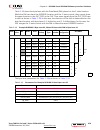

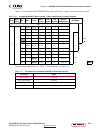

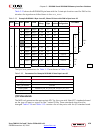

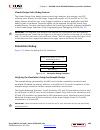

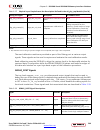

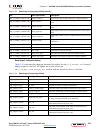

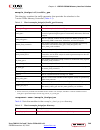

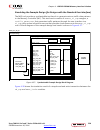

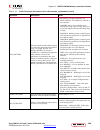

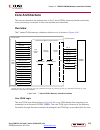

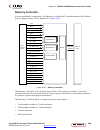

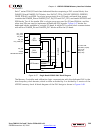

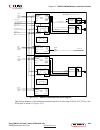

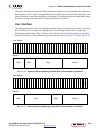

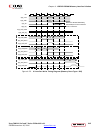

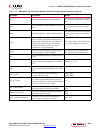

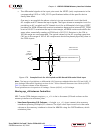

Core Architecture

This section describes the architecture of the 7 series FPGAs memory interface solutions

core, providing an overview of the core modules and interfaces.

Overview

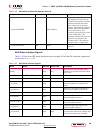

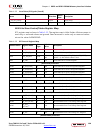

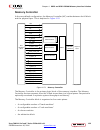

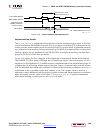

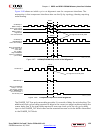

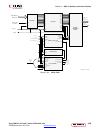

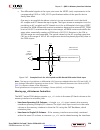

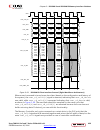

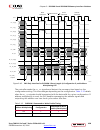

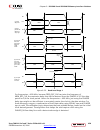

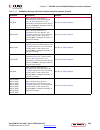

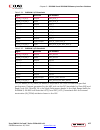

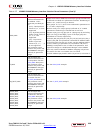

The 7 series FPGAs memory interface solutions core is shown in

.

X-Ref Target - Figure 1-51

Figure 1-51:

7 Series FPGAs Memory Interface Solution

rst

clk

app_addr

app_cmd

app_en

app_hi_pri

app_wdf_data

app_wdf_end

app_wdf_mask

app_wdf_wren

app_rdy

app_rd_data

app_rd_data_end

app_rd_data_valid

app_wdf_rdy

app_sr_req

app_sr_active

app_ref_req

app_ref_ack

app_zq_req

app_zq_ack

ddr_ad dr

ddr_ba

ddr_cas_n

ddr_ck

ddr_cke

ddr_cs_n

ddr_dm

ddr_o dt

ddr_ra s_n

ddr_reset_n

ddr we n

ddr_dq

ddr_dqs_n

ddr_dqs

User

FPGA

Logic

DDR2/DDR3

SDRAM

User

Interface

Block

Memory

Controller

Physical

Layer

7 Series FPGAs Memory Interface Solution

User Interface

(1)

Physical Interface

7 Series FPGAs

Native Interface

MC/PHY Interface

ddr_ck_n

ddr_parity

IOB

1. System clock (sys_clk_p and sys_clk_n/sys_clk_i), Reference clock (clk_ref_p and clk_ref_n/clk_ref_i), and system reset (sys_rst_n) port

connections are not shown in block diagram.

Summary of Zynq-7000

Page 1

Zynq-7000 ap soc and 7 series devices memory interface solutions v4.1 user guide ug586 november 30, 2016.

Page 2

Zynq-7000 ap soc and 7 series fpgas mis v4.1 2 ug586 november 30, 2016 www.Xilinx.Com date version revision 11/30/2016 4.1 • renamed questasim to questa advanced simulator. Qdr ii+ • updated qdr_k_n/p directions in physical interface signals table. • updated in qdr_k_n/p directions i/o standards tab...

Page 3

Zynq-7000 ap soc and 7 series fpgas mis v4.1 3 ug586 november 30, 2016 www.Xilinx.Com 11/18/2015 2.4 • added asynchronous to sys_rst in all sections. • added note to relaxed mode in ddr3/ddr2 and lddr2 sections. • updated code in all configuration sections • added important jitter note in pinout req...

Page 4

Zynq-7000 ap soc and 7 series fpgas mis v4.1 4 ug586 november 30, 2016 www.Xilinx.Com 04/01/2015 2.3 • updated description in all configuration sections. • updated sim_bypass_init_cal. Chapter 1 • added description in setting ddr3 memory parameter option section. • added note to answer record: 54025...

Page 5

Zynq-7000 ap soc and 7 series fpgas mis v4.1 5 ug586 november 30, 2016 www.Xilinx.Com 11/19/2014 2.3 chapter 1 • updated description in round-robin section. • updated rtt_wr in table 1-92: 7 series fpga memory solution configuration parameters. • updated description in debugging oclkdelayed calibrat...

Page 6

Zynq-7000 ap soc and 7 series fpgas mis v4.1 6 ug586 november 30, 2016 www.Xilinx.Com 06/04/2014 2.1 chapter 1 • added reference to data sheet in features section. • added important note about data mask in controller options section. • added note in precharge policy section. • added prbs_saddr_ mask...

Page 7

Zynq-7000 ap soc and 7 series fpgas mis v4.1 7 ug586 november 30, 2016 www.Xilinx.Com 04/02/2014 2.0 chapter 1 • updated book to dqs. • updated table 1-4: files in example_design/sim directory. • updated file description in simulation flow using ies and vcs script files section. • added no buffer de...

Page 8

Zynq-7000 ap soc and 7 series fpgas mis v4.1 8 ug586 november 30, 2016 www.Xilinx.Com 12/18/2013 2.0 • vivado design suite release only for mig v2.0. Chapter 1 • added out of context content. • updated table 1-4: modules in example_design/sim directory. • updated /user_design section. • updated fig....

Page 9

Zynq-7000 ap soc and 7 series fpgas mis v4.1 9 ug586 november 30, 2016 www.Xilinx.Com 10/02/2013 2.0 • vivado design suite release only for mig v2.0. • removed ise content throughout book and updated screenshots to v2.0. Chapter 1 • updated memory part bullet description. • updated table 1-4 sim.Do ...

Page 10

Zynq-7000 ap soc and 7 series fpgas mis v4.1 10 ug586 november 30, 2016 www.Xilinx.Com 06/19/2013 2.0 • vivado design suite release only for mig v2.0. Revision number advanced to 2.0 to align with core version number. Chapter 1 • updated chipscope to vivado logic analyzer, vio, and ila. • updated ui...

Page 11

Zynq-7000 ap soc and 7 series fpgas mis v4.1 11 ug586 november 30, 2016 www.Xilinx.Com continued • updated table 3-27 debug_port signal with dbg_rd_stage1_rtr_error[n_data_lanes - 1:0] and dbg_rd_stage1_error[n_data_lanes - 1:0]. • updated tables 3-31 and 3-32 read stage 1 and stage 2 debug signal m...

Page 12

Zynq-7000 ap soc and 7 series fpgas mis v4.1 12 ug586 november 30, 2016 www.Xilinx.Com continued chapter 2 • added no buffer option description in fpga options section. • added pinout description in verify pin changes and update design section. • updated fig. 2-15 fpga options. • updated refclk_freq...

Page 13

Zynq-7000 ap soc and 7 series fpgas mis v4.1 13 ug586 november 30, 2016 www.Xilinx.Com 12/18/2012 1.8 • ise 14.4 and vivado 2012.4 design suite releases for mig v1.8. Chapter 1 • updated table 1-2 to 1-9 with new table note and.V name. • updated fig. 1-16 fpga options gui. • added xadc instantiation...

Page 14

Zynq-7000 ap soc and 7 series fpgas mis v4.1 14 ug586 november 30, 2016 www.Xilinx.Com 10/16/2012 1.7 • mig 1.7 release. Updated ise design suite version to 14.3. • chapter 1: added axi4-lite slave control/status register interface block section. Updated figures (1-32 and 1-37) and added prbs and te...

Page 15

Zynq-7000 ap soc and 7 series fpgas mis v4.1 15 ug586 november 30, 2016 www.Xilinx.Com 04/24/2012 1.4 • mig 1.5 release. Updated ise design suite version to 14.1. Updated gui screen captures throughout document. Replaced iodelayctrl with idelayctrl throughout. • chapter 1: added i/o power reduction ...

Page 16

Zynq-7000 ap soc and 7 series fpgas mis v4.1 16 ug586 november 30, 2016 www.Xilinx.Com 10/19/2011 1.2 • mig 1.3 release. Updated ise design suite version to 13.3. • chapter 1: added step 2 to mig output options, page 26. Added note about optional use of the memory controller to controller options, p...

Page 17

Zynq-7000 ap soc and 7 series fpgas mis v4.1 17 ug586 november 30, 2016 www.Xilinx.Com 06/22/2011 1.1 • mig 1.2 release. Updated ise design suite version to 13.2. Updated gui screen captures throughout document. • chapter 1: added verify pin changes and update design, simulating the example design (...

Page 18

Zynq-7000 ap soc and 7 series fpgas mis v4.1 18 ug586 november 30, 2016 www.Xilinx.Com table of contents chapter 1: ddr3 and ddr2 sdram memory interface solution introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 19

Zynq-7000 ap soc and 7 series fpgas mis v4.1 19 ug586 november 30, 2016 www.Xilinx.Com designing with the core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 611 interfacing to the core. . . . . . . . . . . . . . . . . . . . . . . ...

Page 20: Introduction

Zynq-7000 ap soc and 7 series fpgas mis v4.1 20 ug586 november 30, 2016 www.Xilinx.Com chapter 1 ddr3 and ddr2 sdram memory interface solution introduction the xilinx ® 7 series fpgas memory interface solutions (mis) core is a combined pre-engineered controller and physical layer (phy) for interfaci...

Page 21

Zynq-7000 ap soc and 7 series fpgas mis v4.1 21 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution using mig in the vivado design suite this section provides the steps to generate the memory interface generator (mig) ip core using the vivado design suite ...

Page 22

Zynq-7000 ap soc and 7 series fpgas mis v4.1 22 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 3. Click next to proceed to the project name page ( figure 1-3 ). Enter the project name and project location. Based on the details provided, the project is...

Page 23

Zynq-7000 ap soc and 7 series fpgas mis v4.1 23 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 4. Click next to proceed to the project type page ( figure 1-4 ). Select the project type as rtl project because mig deliverables are rtl files. 5. Click ne...

Page 24

Zynq-7000 ap soc and 7 series fpgas mis v4.1 24 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 6. Click next to open the add existing ip (optional) page ( figure 1-6 ). If the ip is already created, the xci file generated by the ip can be added to the...

Page 25

Zynq-7000 ap soc and 7 series fpgas mis v4.1 25 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 8. Click next to proceed to the default part page ( figure 1-8 ) where the device that needs to be targeted can be selected. The default part page appears a...

Page 26

Zynq-7000 ap soc and 7 series fpgas mis v4.1 26 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution select the target family, package, and speed grade. The valid devices are displayed in the same page, and the device can be selected based on the targeted d...

Page 27

Zynq-7000 ap soc and 7 series fpgas mis v4.1 27 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 9. Click next to open the new project summary page ( figure 1-11 ). This includes the summary of selected project details. 10. Click finish to complete the ...

Page 28

Zynq-7000 ap soc and 7 series fpgas mis v4.1 28 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 11. Click ip catalog on the project manager window to open the ip catalog window. The vivado ip catalog window appears on the right side panel (see figure 1...

Page 29

Zynq-7000 ap soc and 7 series fpgas mis v4.1 29 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 13. Select mig 7 series to open the mig tool ( figure 1-13 ). 14. Click next to display the output options page. Customizing and generating the core caution...

Page 30

Zynq-7000 ap soc and 7 series fpgas mis v4.1 30 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution mig outputs are generated with the folder name . Important: only alphanumeric characters can be used for . Special characters cannot be used. This name shou...

Page 31

Zynq-7000 ap soc and 7 series fpgas mis v4.1 31 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution xilinx 7 series devices using stacked silicon interconnect (ssi) technology have super logic regions (slrs). Memory interfaces cannot span across slrs. If t...

Page 32

Zynq-7000 ap soc and 7 series fpgas mis v4.1 32 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution creating 7 series fpga ddr3 memory controller block design memory selection this page displays all memory types that are supported by the selected fpga fami...

Page 33

Zynq-7000 ap soc and 7 series fpgas mis v4.1 33 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution controller options this page shows the various controller options that can be selected ( figure 1-17 ). Tip: the use of the memory controller is optional. T...

Page 34

Zynq-7000 ap soc and 7 series fpgas mis v4.1 34 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • frequency – this feature indicates the operating frequency for all of the controllers. The frequency block is limited by factors such as the selected fpga...

Page 35

Zynq-7000 ap soc and 7 series fpgas mis v4.1 35 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution important: the data mask (dm) option is always selected for axi designs and is grayed out (you cannot select it). For axi interfaces, read modify write (rmw...

Page 36

Zynq-7000 ap soc and 7 series fpgas mis v4.1 36 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the create custom part page includes all the specifications of the memory component selected in the select base part pull-down menu. 3. Enter the appropriat...

Page 37

Zynq-7000 ap soc and 7 series fpgas mis v4.1 37 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution axi parameter options this feature allows the selection of axi parameters for the controller ( figure 1-20 ). These are standard axi parameters or parameter...

Page 38

Zynq-7000 ap soc and 7 series fpgas mis v4.1 38 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution x-ref target - figure 1-20 figure 1-20: setting axi parameter options ug586_c1_22_090511 send feedback.

Page 39

Zynq-7000 ap soc and 7 series fpgas mis v4.1 39 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution setting ddr3 memory parameter option this feature allows the selection of various memory mode register values, as supported by the controller specification ...

Page 40

Zynq-7000 ap soc and 7 series fpgas mis v4.1 40 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the desired input clock period is selected from the list. These values are determined by the memory clock period chosen and the allowable limits of the para...

Page 41

Zynq-7000 ap soc and 7 series fpgas mis v4.1 41 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • system clock – this option selects the clock type (single-ended, differential, or no buffer) for the sys_clk signal pair. When the no buffer option is sel...

Page 42

Zynq-7000 ap soc and 7 series fpgas mis v4.1 42 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • i/o power reduction – this option reduces the average i/o power by disabling dq and dqs ibufs automatically whenever the controller is in the idle state. ...

Page 43

Zynq-7000 ap soc and 7 series fpgas mis v4.1 43 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • dci cascade – this selection enables the vrn/vrp pins that are available in high performance banks to allocate for the address/control and reset_n ports. ...

Page 44

Zynq-7000 ap soc and 7 series fpgas mis v4.1 44 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution bank selection this feature allows the selection of bytes for the memory interface. Bytes can be selected for different classes of memory signals, such as: ...

Page 45

Zynq-7000 ap soc and 7 series fpgas mis v4.1 45 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution for devices implemented with ssi technology, the slrs are indicated by a number in the header in each bank, for example, slr 1. Interfaces cannot span acros...

Page 46

Zynq-7000 ap soc and 7 series fpgas mis v4.1 46 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • clk_ref – this is the reference frequency input for the idelay control. The clk_ref input can be generated internally or connected to an external source. ...

Page 47

Zynq-7000 ap soc and 7 series fpgas mis v4.1 47 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution memory model license the mig tool can output a chosen vendor’s memory model for simulation purposes for memories such as ddr2 or ddr3 sdrams. To access the ...

Page 48

Zynq-7000 ap soc and 7 series fpgas mis v4.1 48 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution click next to move to pcb information page. Pcb information this page displays the pcb-related information to be considered while designing the board that u...

Page 49

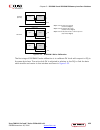

Zynq-7000 ap soc and 7 series fpgas mis v4.1 49 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution vivado integrated design flow for mig 1. After clicking generate, the generate output products window appears. This window has the out-of-context settings a...

Page 50

Zynq-7000 ap soc and 7 series fpgas mis v4.1 50 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 2. Click out-of-context settings to configure generation of synthesized checkpoints. To enable the out-of-context flow, enable the check box. To disable the...

Page 51

Zynq-7000 ap soc and 7 series fpgas mis v4.1 51 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 4. After generating the mig core design, the project window appears as shown in figure 1-31 . 5. After project creation, the xci file is added to the projec...

Page 52

Zynq-7000 ap soc and 7 series fpgas mis v4.1 52 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution design generation from the mig tool can be generated using the create design flow or the verify pin changes and update design flows. There is no difference ...

Page 53

Zynq-7000 ap soc and 7 series fpgas mis v4.1 53 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 7. Clicking the generate output products option brings up the manage outputs window ( figure 1-34 ). X-ref target - figure 1-33 figure 1-33: generate rtl an...

Page 54

Zynq-7000 ap soc and 7 series fpgas mis v4.1 54 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 8. All user-design rtl files and constraints files (xdc files) can be viewed in the sources > libraries tab ( figure 1-35 ). 9. The vivado design suite supp...

Page 55

Zynq-7000 ap soc and 7 series fpgas mis v4.1 55 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 10. This option creates a new vivado project. Selecting the menu brings up a dialog box, which guides you to the directory for a new design project. Select ...

Page 56

Zynq-7000 ap soc and 7 series fpgas mis v4.1 56 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 11. Click generate bitstream under project manager > program and debug to generate the bit file for the generated design. The /.Runs/ impl_1 directory inclu...

Page 57

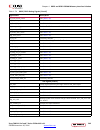

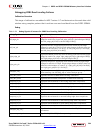

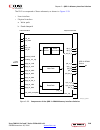

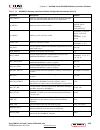

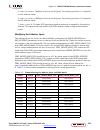

Zynq-7000 ap soc and 7 series fpgas mis v4.1 57 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution directory structure and file descriptions output directory structure the output directory structure of the selected memory controller (mc) design from the m...

Page 58

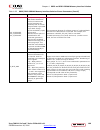

Zynq-7000 ap soc and 7 series fpgas mis v4.1 58 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution mig_7series_v4_1 docs example_design par rtl traffic_gen sim synth user_design rtl clocking controller ip_top phy ui xdc directory and file contents the 7 s...

Page 59

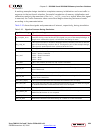

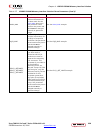

Zynq-7000 ap soc and 7 series fpgas mis v4.1 59 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution example_design/rtl/traffic_gen this directory contains the traffic generator that provides the stimulus to the 7 series fpgas memory controller ( table 1-2 ...

Page 60

Zynq-7000 ap soc and 7 series fpgas mis v4.1 60 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution /example_design/sim table 1-4 lists the modules in the example_design/sim directory. /user_design the user_design folder contains the following: • rtl and x...

Page 61

Zynq-7000 ap soc and 7 series fpgas mis v4.1 61 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution user_design/rtl/clocking this directory contains the user design ( table 1-5 ). User_design/rtl/controller this directory contains the memory controller tha...

Page 62

Zynq-7000 ap soc and 7 series fpgas mis v4.1 62 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution user_design/rtl/ip_top this directory contains the user design ( table 1-7 ). User_design/rtl/phy this directory contains the 7 series fpga memory interface...

Page 63

Zynq-7000 ap soc and 7 series fpgas mis v4.1 63 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution user_design/rtl/ui this directory contains the user interface code that mediates between the native interface of the memory controller and user applications...

Page 64

Zynq-7000 ap soc and 7 series fpgas mis v4.1 64 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution verify pin changes and update design this feature verifies the input xdc for bank selections, byte selections, and pin allocation. It also generates errors ...

Page 65: Quick Start Example Design

Zynq-7000 ap soc and 7 series fpgas mis v4.1 65 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ° an fpga byte lane should not contain pins related to two different strobe sets. ° v ref i/o can be used only when the internal v ref is chosen. • verified...

Page 66

Zynq-7000 ap soc and 7 series fpgas mis v4.1 66 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution implementing the example design for more information on using an ip example design, see the vivado design suite user guide: designing with ip (ug896) [ref 7...

Page 67

Zynq-7000 ap soc and 7 series fpgas mis v4.1 67 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution traffic generator operation the traffic generator module contained within the synthesizable test bench can be parameterized to create various stimulus patte...

Page 68: Modifying The Example Design

Zynq-7000 ap soc and 7 series fpgas mis v4.1 68 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the read data returning from the memory device is accessed by the traffic generator through the user interface read data port and compared against internall...

Page 69

Zynq-7000 ap soc and 7 series fpgas mis v4.1 69 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution prbs_eaddr_mask_pos sets the 32-bit and mask position. This parameter is used with the prbs address generator to shift random addresses down into the port a...

Page 70

Zynq-7000 ap soc and 7 series fpgas mis v4.1 70 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution data_pattern this parameter sets the data pattern circuits to be generated through rtl logic. For larger devices, the data_pattern can be set to “dgen_all,”...

Page 71

Zynq-7000 ap soc and 7 series fpgas mis v4.1 71 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the command patterns instr_mode_i, addr_mode_i, bl_mode_i, and data_mode_i of the traffic_gen module can each be set independently. The provided init_mem_pa...

Page 72

Zynq-7000 ap soc and 7 series fpgas mis v4.1 72 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 5: dgen_walking1. Walking 1s are on the dq pins. The starting position of 1 depends on the address value. 6: dgen_walking0. Walking 0s are on the dq pins. T...

Page 73

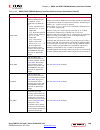

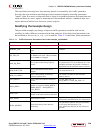

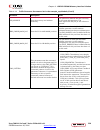

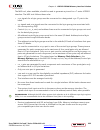

Zynq-7000 ap soc and 7 series fpgas mis v4.1 73 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution traffic generator signal description traffic generator signals are described in table 1-13 . 0x2000 0xafff 0x00002000 0xffff0000 0x2000 0xbfff 0x00002000 0x...

Page 74

Zynq-7000 ap soc and 7 series fpgas mis v4.1 74 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution vio_modify_enable input allow vio_xxxx_mode_value to alter traffic pattern. Vio_data_mode_value[3:0] input valid settings for this signal are: • 0x0: reserv...

Page 75

Zynq-7000 ap soc and 7 series fpgas mis v4.1 75 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution vio_instr_mode_value[3:0] input valid settings for this signal are: • 0x1: command type (read/write) as defined by fixed_instr_i. • 0x2: random read/write c...

Page 76

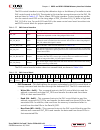

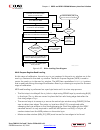

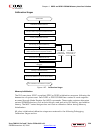

Zynq-7000 ap soc and 7 series fpgas mis v4.1 76 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution memory initialization and traffic test flow after power-up, the init memory control block directs the traffic generator to initialize the memory with the se...

Page 77

Zynq-7000 ap soc and 7 series fpgas mis v4.1 77 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 2. The cmd_seed_i and data_seed_i input values are set for the internal prbs generator. This step is not required for other patterns. 3. The instr_mode_i in...

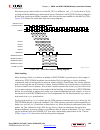

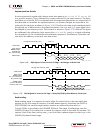

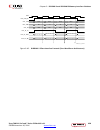

Page 78

Zynq-7000 ap soc and 7 series fpgas mis v4.1 78 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution figure 1-42 shows the simple write transaction being performed on the axi4 interface. This transaction consists of a command phase, a data phase, and a resp...

Page 79

Zynq-7000 ap soc and 7 series fpgas mis v4.1 79 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution figure 1-43 shows a simple read transaction being performed on the axi4 interface. This transaction consists of a command phase and data phase. This follows...

Page 80

Zynq-7000 ap soc and 7 series fpgas mis v4.1 80 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the initialization and the calibration sequence remain the same as that indicated in simulating the example design (for designs with the standard user inter...

Page 81

Zynq-7000 ap soc and 7 series fpgas mis v4.1 81 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the status generated for a read transaction is shown in figure 1-45 . 5:2 response id for the write response 1:0 write response received for axi table 1-15:...

Page 82

Zynq-7000 ap soc and 7 series fpgas mis v4.1 82 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution calibration and other ddr data read and write transactions are similar to what is described in simulating the example design (for designs with the standard ...

Page 83

Zynq-7000 ap soc and 7 series fpgas mis v4.1 83 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution simulation flow using vivado simulator 1. In the open ip example design vivado project, under flow navigator, select simulation settings ( figure 1-46 ). 2....

Page 84

Zynq-7000 ap soc and 7 series fpgas mis v4.1 84 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 3. In the flow navigator window, select run simulation and select run behavioral simulation as shown in figure 1-47 . Simulation flow using questa advanced ...

Page 85

Zynq-7000 ap soc and 7 series fpgas mis v4.1 85 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 4. In the flow navigator window, select run simulation and select run behavioral simulation as shown in figure 1-47 . 5. Vivado invokes questa advanced simu...

Page 86

Zynq-7000 ap soc and 7 series fpgas mis v4.1 86 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution a. Browse to the compiled libraries location and set the path on compiles libraries location option. B. Under the compilation tab, set the vcs.Compile.Vloga...

Page 87

Zynq-7000 ap soc and 7 series fpgas mis v4.1 87 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 5. Vivado invokes vcs and simulations are run in the vcs tool. For more information, see the vivado design suite user guide: logic simulation (ug900) [ref 8...

Page 88

Zynq-7000 ap soc and 7 series fpgas mis v4.1 88 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 3. Apply the settings and select ok. 4. In the flow navigator window, select run simulation and select run behavioral simulation as shown in figure 1-47 . 5...

Page 89

Zynq-7000 ap soc and 7 series fpgas mis v4.1 89 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution synplify pro black box testing using the synopsys ® synplify pro ® flow for example_design, follow these steps to run black box synthesis with synplify pro ...

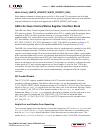

Page 90: Core Architecture

Zynq-7000 ap soc and 7 series fpgas mis v4.1 90 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 10. Run implementation flow with the vivado tool. For details about implementation, see the vivado design suite user guide: designing with ip (ug896) [ref 7...

Page 91

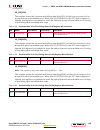

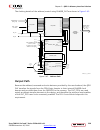

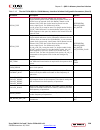

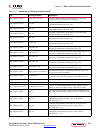

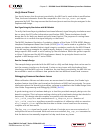

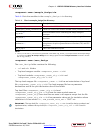

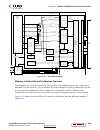

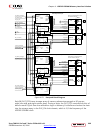

Zynq-7000 ap soc and 7 series fpgas mis v4.1 91 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution user fpga logic the user fpga logic block shown in figure 1-51 is any fpga design that requires to be connected to an external ddr2 or ddr3 sdram. The user ...

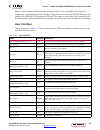

Page 92: User Interface

Zynq-7000 ap soc and 7 series fpgas mis v4.1 92 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution when a user creates a multicontroller design on their own, each mig output has the component instantiated with the primitive. This violates the rules for id...

Page 93

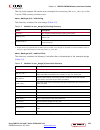

Zynq-7000 ap soc and 7 series fpgas mis v4.1 93 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution app_addr[addr_width – 1:0] this input indicates the address for the request currently being submitted to the ui. The ui aggregates all the address fields of...

Page 94

Zynq-7000 ap soc and 7 series fpgas mis v4.1 94 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution app_en this input strobes in a request. You must apply the desired values to app_addr[], app_cmd [2:0], and app_hi_pri, and then assert app_en to submit the...

Page 95

Zynq-7000 ap soc and 7 series fpgas mis v4.1 95 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution - a write is requested and no write buffer pointers are available ° a periodic read is being inserted app_rd_data[app_data_width – 1:0] this output contains...

Page 96: Axi4 Slave Interface Block

Zynq-7000 ap soc and 7 series fpgas mis v4.1 96 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ui_clk_sync_rst this is the reset from the ui which is in synchronous with ui_clk. Ui_clk this is the output clock from the ui. It must be a half or quarter...

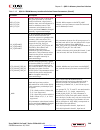

Page 97

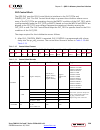

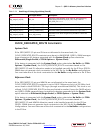

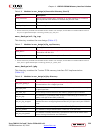

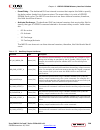

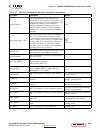

Zynq-7000 ap soc and 7 series fpgas mis v4.1 97 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution axi4 slave interface parameters table 1-19 lists the axi4 slave interface parameters. Table 1-19: axi4 slave interface parameters parameter name default val...

Page 98

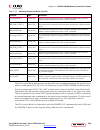

Zynq-7000 ap soc and 7 series fpgas mis v4.1 98 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution axi4 slave interface signals table 1-20 lists the axi4 slave interface specific signal. All of the axi interface signals are synchronous to ui_clk. C_s_axi_...

Page 99

Zynq-7000 ap soc and 7 series fpgas mis v4.1 99 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution s_axi_awready 1 output high write address ready. This signal indicates that the slave is ready to accept an address and associated control signals. S_axi_wd...

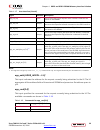

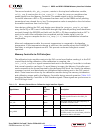

Page 100: Arbitration In Axi Shim

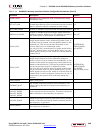

Zynq-7000 ap soc and 7 series fpgas mis v4.1 100 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution arbitration in axi shim the axi4 protocol calls for independent read and write address channels. The memory controller has one address channel. The followi...

Page 101

Zynq-7000 ap soc and 7 series fpgas mis v4.1 101 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution write priority (write_priority, write_priority_reg) write address channel is always given priority in this mode. The requests from the read address channel...

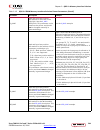

Page 102

Zynq-7000 ap soc and 7 series fpgas mis v4.1 102 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution there can be between 0 and c_nck_per_clk × 2 errors per cycle with each data beat signaled by one of the vector bits. Multiple bits of the vector can be si...

Page 103

Zynq-7000 ap soc and 7 series fpgas mis v4.1 103 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution axi4-lite slave control/status register interface signals table 1-22 lists the axi4 slave interface specific signals. Clock/reset to the interface is provi...

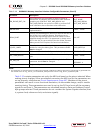

Page 104

Zynq-7000 ap soc and 7 series fpgas mis v4.1 104 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution axi4-lite slave control/status register map ecc register map is shown in table 1-23 . The register map is little endian. Write accesses to read-only or res...

Page 105

Zynq-7000 ap soc and 7 series fpgas mis v4.1 105 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution axi4-lite slave control/status register map detailed descriptions ecc_status this register holds information on the occurrence of correctable and uncorrect...

Page 106

Zynq-7000 ap soc and 7 series fpgas mis v4.1 106 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ue_en_irq are set to 1 (enabled), the value of the interrupt signal is the logical or between the ce_status and ue_status bits. Ecc_on_off the ecc on/off c...

Page 107

Zynq-7000 ap soc and 7 series fpgas mis v4.1 107 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ce_ffa[31:0] this register stores the address (bits[31:0]) of the first occurrence of an access with a correctable error. When the ce_status bit in the ecc...

Page 108

Zynq-7000 ap soc and 7 series fpgas mis v4.1 108 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution this register is re-enabled to store the data of the next correctable error. Storing of the failing data is enabled after reset. Ce_ffd[95:64] note: this r...

Page 109

Zynq-7000 ap soc and 7 series fpgas mis v4.1 109 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-34 describes the register bit usage when dq_width = 72. Table 1-35 describes the register bit usage when dq_width = 144. Ue_ffa[31:0] this register...

Page 110

Zynq-7000 ap soc and 7 series fpgas mis v4.1 110 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ue_ffd[31:0] this register stores the (uncorrected) failing data (bits[31:0]) of the first occurrence of an access with an uncorrectable error. When the ue...

Page 111

Zynq-7000 ap soc and 7 series fpgas mis v4.1 111 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ue_ffd[127:96] note: this register is only used when the dq_width == 144. This register stores the (uncorrected) failing data (bits[127:96]) of the first o...

Page 112

Zynq-7000 ap soc and 7 series fpgas mis v4.1 112 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the register is only implemented if c_ecc_test = “on” or ecc_test_fi_xor = “on” and ecc = “on” in a mig design in the vivado ip catalog. Injecting faults s...

Page 113

Zynq-7000 ap soc and 7 series fpgas mis v4.1 113 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution injecting faults should be performed in a critical region in software; that is, writing this register and the subsequent write to the memory must not be in...

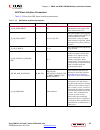

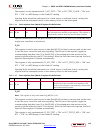

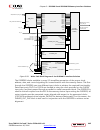

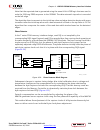

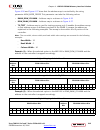

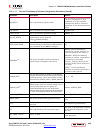

Page 114: User Interface Block

Zynq-7000 ap soc and 7 series fpgas mis v4.1 114 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-48 describes the register bit usage when dq_width = 72. Table 1-49 describes the register bit usage when dq_width = 144. User interface block the u...

Page 115

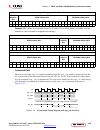

Zynq-7000 ap soc and 7 series fpgas mis v4.1 115 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the bank, row, and column comprise a target address on the memory device for read and write operations. Commands are specified using the cmd[2:0] input to ...

Page 116

Zynq-7000 ap soc and 7 series fpgas mis v4.1 116 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution receives read data from the external memory. The core echoes this address back when the requests are processed. Write command signals the native interface ...

Page 117

Zynq-7000 ap soc and 7 series fpgas mis v4.1 117 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution wr_data_offset this bus is used to step through the data buffer when the burst length requires more than a single cycle to complete. This bus, in combinati...

Page 118

Zynq-7000 ap soc and 7 series fpgas mis v4.1 118 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution native interface maintenance command signals table 1-54 lists the native interface maintenance command signals. App_ref_req when asserted, this active-high...

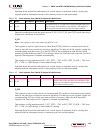

Page 119: Clocking Architecture

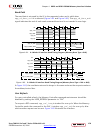

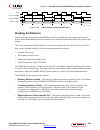

Zynq-7000 ap soc and 7 series fpgas mis v4.1 119 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution clocking architecture the phy design requires that a pll module be used to generate various clocks, and both global and local clock networks are used to di...

Page 120

Zynq-7000 ap soc and 7 series fpgas mis v4.1 120 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • when hr banks are selected for memory interface pins in gui and the memory frequencies ≥ 400 mhz, the phase is 337.5°. • when hr banks are selected for m...

Page 121

Zynq-7000 ap soc and 7 series fpgas mis v4.1 121 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution write path (output) i/o logic clock the output path comprising both data and controls is clocked by phaser_out. The phaser_out provides synchronized clocks...

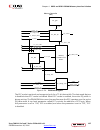

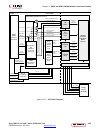

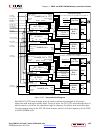

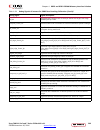

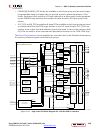

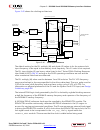

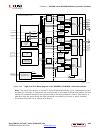

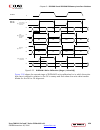

Page 122: Memory Controller

Zynq-7000 ap soc and 7 series fpgas mis v4.1 122 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution memory controller in the core default configuration, the memory controller (mc) resides between the ui block and the physical layer. This is depicted in fi...

Page 123

Zynq-7000 ap soc and 7 series fpgas mis v4.1 123 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution bank machines most of the memory controller logic resides in the bank machines. Bank machines correspond to dram banks. A given bank machine manages a sing...

Page 124

Zynq-7000 ap soc and 7 series fpgas mis v4.1 124 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution column commands can be reordered for the purpose of optimizing memory interface throughput. The ordering algorithm nominally ensures data coherence. The re...

Page 125

Zynq-7000 ap soc and 7 series fpgas mis v4.1 125 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution not all requests require an activate. If a preceding request has activated the same rank, bank, or row, a subsequent request might inherit the bank machine...

Page 126: Error Correcting Code

Zynq-7000 ap soc and 7 series fpgas mis v4.1 126 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution precharge policy the controller implements an aggressive precharge policy. The controller examines the input queue of requests as each transaction complete...

Page 127

Zynq-7000 ap soc and 7 series fpgas mis v4.1 127 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the ecc mode is optional and supported only for a 72-bit data width. The data mask feature is disabled when ecc mode is enabled. When ecc mode is enabled, ...

Page 128

Zynq-7000 ap soc and 7 series fpgas mis v4.1 128 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the ecc functionality is implemented as three functional blocks. A write data merge and ecc generate block. A read data ecc decode and correct block and a ...

Page 129

Zynq-7000 ap soc and 7 series fpgas mis v4.1 129 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution when the wr_bytes command is given, the memory controller performs a read-modify-write (rmw) cycle. When a wr_bytes command is at the head of the queue, it...

Page 130

Zynq-7000 ap soc and 7 series fpgas mis v4.1 130 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ecc self-test functionality under normal operating conditions, the ecc part of the data written to the dram array is not visible at the user interface. Thi...

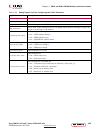

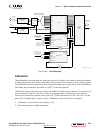

Page 131: Phy

Zynq-7000 ap soc and 7 series fpgas mis v4.1 131 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution phy the phy provides a physical interface to an external ddr2 or ddr3 sdram. The phy generates the signal timing and sequencing required to interface to th...

Page 132

Zynq-7000 ap soc and 7 series fpgas mis v4.1 132 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the memory controller and calibration logic communicate with this dedicated phy in the slow frequency clock domain, which is either a divided by 4 or divid...

Page 133

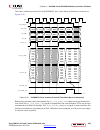

Zynq-7000 ap soc and 7 series fpgas mis v4.1 133 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution x-ref target - figure 1-56 figure 1-56: phy block diagram )/,/')# )3%2$%3 /3%2$%3 /$$2 )$%,!9 $$2 $$2 3$2!- )/ &)&/s &0'! $$2$$2 &0'! 0(9 #ontrol "lock 0(!...

Page 134

Zynq-7000 ap soc and 7 series fpgas mis v4.1 134 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution memory initialization and calibration sequence after deassertion of system reset, the phy performs the required power-on initialization sequence for the me...

Page 135

Zynq-7000 ap soc and 7 series fpgas mis v4.1 135 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the calibration stages in figure 1-57 correspond to these sections: • memory initialization, page 144 • phaser_in phase lock, page 145 • phaser_in dqsfound...

Page 136

Zynq-7000 ap soc and 7 series fpgas mis v4.1 136 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the phy control interface is used by the calibration logic or the memory controller to write phy control words to the phy. The signals in this interface ar...

Page 137

Zynq-7000 ap soc and 7 series fpgas mis v4.1 137 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • control offset – this field is used to control when the address and command in/out_fifos are read and transferred to the iois. The control offset is in u...

Page 138

Zynq-7000 ap soc and 7 series fpgas mis v4.1 138 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-59: auxiliary output attributes attribute type description mc_ao_wrlvl_en vector[3:0] this attribute specifies whether or not the related aux_outpu...

Page 139

Zynq-7000 ap soc and 7 series fpgas mis v4.1 139 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the phy control block has several counters that are not enabled because the synchronous mode is used where phy_clk is either 1/4 or 1/2 the frequency of th...

Page 140

Zynq-7000 ap soc and 7 series fpgas mis v4.1 140 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution command path a command requested by the calibration logic or memory controller is sent out as a phy control word to the phy control block and a simultaneou...

Page 141

Zynq-7000 ap soc and 7 series fpgas mis v4.1 141 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the timing diagram of the address/command path from the output of the out_fifo to the fpga pins is shown in figure 1-59 . X-ref target - figure 1-58 figure...

Page 142

Zynq-7000 ap soc and 7 series fpgas mis v4.1 142 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution datapath the datapath comprises the write and read datapaths. The datapath in the 7 series fpga is completely implemented in dedicated logic with in/out_fi...

Page 143

Zynq-7000 ap soc and 7 series fpgas mis v4.1 143 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution each in/out_fifo has a storage array of memory elements arranged as 10 groups eight bits wide and eight entries deep. During a write, the out_fifo receives...

Page 144

Zynq-7000 ap soc and 7 series fpgas mis v4.1 144 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the out_fifo serializes from eight bits to four bits and outputs the 4-bit data to the oserdes in the oclkdiv domain that is half the frequency of the ddr2...

Page 145

Zynq-7000 ap soc and 7 series fpgas mis v4.1 145 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution phaser_in phase lock phaser_in is placed in the read calibration mode to phase align its free-running frequency reference clock to the associated read dqs....

Page 146

Zynq-7000 ap soc and 7 series fpgas mis v4.1 146 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution each byte group can be read out of the in_fifo on different phy_clk cycles due to fly-by routing and delay differences within each group. Therefore, the in...

Page 147

Zynq-7000 ap soc and 7 series fpgas mis v4.1 147 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the timing diagram for write leveling is shown in figure 1-63 . Periodic dqs pulses are output by the fpga memory interface to detect the level of the ck c...

Page 148

Zynq-7000 ap soc and 7 series fpgas mis v4.1 148 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution implementation details the write_calib_n signal indicating the start of write leveling mode is input to the phy control block after twldqsen to ensure that...

Page 149

Zynq-7000 ap soc and 7 series fpgas mis v4.1 149 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution multi-purpose register read leveling at this stage of calibration, the write dqs is not centered in the write dq window nor is the read dqs centered in the...

Page 150

Zynq-7000 ap soc and 7 series fpgas mis v4.1 150 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • when second edge is not found, second_edge_taps are set to zero. However, the algorithm computes the midpoint of the data window using 63 as the second e...

Page 151

Zynq-7000 ap soc and 7 series fpgas mis v4.1 151 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the stage 3 start tap value places the dqs anywhere between 90° and 225° with respect to dq . The number of edges detected depends on the write level taps ...

Page 152

Zynq-7000 ap soc and 7 series fpgas mis v4.1 152 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution during the centering substage the write dqs is centered in the write dq window based on the edges found during the edge detection stage. At the end of this...

Page 153

Zynq-7000 ap soc and 7 series fpgas mis v4.1 153 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution figure 1-68 shows an initial dqs to ck alignment case for component interfaces. The assumption is that component interfaces also use the fly-by topology, t...

Page 154

Zynq-7000 ap soc and 7 series fpgas mis v4.1 154 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution implementation details a write command is issued with a known write data pattern (ff 00 aa 55 55 aa 99 66) to a specific location. This is followed by a re...

Page 155

Zynq-7000 ap soc and 7 series fpgas mis v4.1 155 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution a phaser_in provides two clock outputs namely iclk and iclkdiv. Iclk is the stage 2 delay output and iclkdiv is the rising edge aligned divided by 2 versio...

Page 156

Zynq-7000 ap soc and 7 series fpgas mis v4.1 156 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the first two scenarios would result in the left data window edge being detected with a tap count less than 1/2 the bit time and the second window edge mig...

Page 157

Zynq-7000 ap soc and 7 series fpgas mis v4.1 157 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution prbs read leveling this stage of read calibration follows the read leveling calibration stage. The dqs phaser_in fine tap setting determined during the rea...

Page 158

Zynq-7000 ap soc and 7 series fpgas mis v4.1 158 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution important: customers using the phy only design must include the periodic read logic within the custom controller. If the periodic reads are not included, t...

Page 159

Zynq-7000 ap soc and 7 series fpgas mis v4.1 159 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the second module, ddr_phy_tempmon, resides in the top-level calibration module, calib_top . It receives the device_temp[11:0] from the tempmon module and ...

Page 160

Zynq-7000 ap soc and 7 series fpgas mis v4.1 160 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution sync_pulse 1 input – this is the synchronization pulse output by the pll. Pll_lock 1 input – the locked output of the pll instantiated in the infrastructur...

Page 161

Zynq-7000 ap soc and 7 series fpgas mis v4.1 161 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution mc_cke [nck_per_clk – 1:0] input – mc_cke [nck_per_clk – 1:0] is the cke associated with the dram interface. This signal is valid when the cke_odt_aux para...

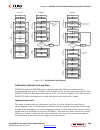

Page 162: Designing With The Core

Zynq-7000 ap soc and 7 series fpgas mis v4.1 162 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution designing with the core the core is bundled with an example design that can be simulated. The example design can be used as a starting point for the user d...

Page 163: Interfacing To The Core

Zynq-7000 ap soc and 7 series fpgas mis v4.1 163 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution interfacing to the core the memory controller can be connected using either the axi4 slave interface, the ui, or the native interface. The axi4 slave inter...

Page 164: Upsizing

Zynq-7000 ap soc and 7 series fpgas mis v4.1 164 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution upsizing when the data width on the user interface side is wider than that on the axi interface side, upsizing is performed in the axi shim interface. Data...

Page 165

Zynq-7000 ap soc and 7 series fpgas mis v4.1 165 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution figure 1-72 and figure 1-73 show that the address map is controlled by the string parameter mem_addr_order. This parameter can take the following values: •...

Page 166

Zynq-7000 ap soc and 7 series fpgas mis v4.1 166 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution example (2) – when the selected option in the mig gui is row_bank_column and the address to the controller is mapped accordingly. Command path when the use...

Page 167

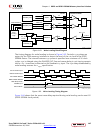

Zynq-7000 ap soc and 7 series fpgas mis v4.1 167 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution a non back-to-back write command can be issued as shown in figure 1-75 . This figure depicts three scenarios for the app_wdf_data, app_wdf_wren, and app_wd...

Page 168

Zynq-7000 ap soc and 7 series fpgas mis v4.1 168 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution write path the write data is registered in the write fifo when app_wdf_wren is asserted and app_wdf_rdy is high ( figure 1-76 ). If app_wdf_rdy is deassert...

Page 169

Zynq-7000 ap soc and 7 series fpgas mis v4.1 169 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the data values at different clock edges are as shown in table 1-63 . For a 2:1 memory controller to dram clock ratio, the application data width is 32 bit...

Page 170

Zynq-7000 ap soc and 7 series fpgas mis v4.1 170 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution read path the read data is returned by the ui in the requested order and is valid when app_rd_data_valid is asserted ( figure 1-81 and figure 1-82 ). The a...

Page 171

Zynq-7000 ap soc and 7 series fpgas mis v4.1 171 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution a user-refresh operation can be performed any time provided the handshake defined above is followed. There are no additional interfacing requirements with ...

Page 172: Native Interface

Zynq-7000 ap soc and 7 series fpgas mis v4.1 172 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution to account for the worst case, subtract trcd, cl, the data transit time and trp for each bank machine to ensure that all transactions can complete before t...

Page 173

Zynq-7000 ap soc and 7 series fpgas mis v4.1 173 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution in figure 1-86 , requests 1 and 2 are accepted normally. The first time request 3 is presented, accept is driven low, and the request is not accepted. The ...

Page 174

Zynq-7000 ap soc and 7 series fpgas mis v4.1 174 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution transfers can be isolated with gaps of non-activity, or there can be long bursts with no gaps. The user design can identify when a request is being process...

Page 175

Zynq-7000 ap soc and 7 series fpgas mis v4.1 175 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution a detailed description of the phy architecture and the various stages of calibration are provided in phy, page 131 . The signals required for the memory co...

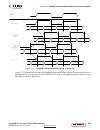

Page 176

Zynq-7000 ap soc and 7 series fpgas mis v4.1 176 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution x-ref target - figure 1-88 figure 1-88: phy interface example $$2 3$2!- 0hysical -#?2!3?. -#?#!3?. -#?7%?. -#?#3?. -#?"!;= -#?!$$2%33;= &2%1?2%,+ -#?#-$;= ...

Page 177

Zynq-7000 ap soc and 7 series fpgas mis v4.1 177 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the data offset field (mc_data_offset) in the phy control word for read commands is determined during phaser_in dqsfound calibration. It is provided by the...

Page 178

Zynq-7000 ap soc and 7 series fpgas mis v4.1 178 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution important: bits[31:27, 24:23, 14:12, and 7:3] in table 1-58, page 136 are not used in this example. The write waveform shown in figure 1-90 illustrates an ...

Page 179

Zynq-7000 ap soc and 7 series fpgas mis v4.1 179 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution important: bits[31:27, 24:23, 14:12, and 7:3] in table 1-58, page 136 are not used in this example. The phy calibration operates with additive latency al) ...

Page 180: Customizing The Core

Zynq-7000 ap soc and 7 series fpgas mis v4.1 180 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution customizing the core the 7 series fpgas memory interface solution supports several configurations for ddr2 or ddr3 sdram devices. The specific configuratio...

Page 181

Zynq-7000 ap soc and 7 series fpgas mis v4.1 181 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ck_width this is the number of ck/ck# outputs to memory. This option is based on the selected mig tool configuration. Cke_width this is the number of cke o...

Page 182

Zynq-7000 ap soc and 7 series fpgas mis v4.1 182 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution wrlvl this option enables write leveling calibration in ddr3 designs. This parameter must always be “on” for ddr3 and “off” for ddr2. This parameter should...

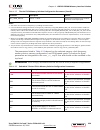

Page 183

Zynq-7000 ap soc and 7 series fpgas mis v4.1 183 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution the parameters listed in table 1-65 depend on the selected memory clock frequency, memory device, memory configuration, and fpga speed grade. The values fo...

Page 184

Zynq-7000 ap soc and 7 series fpgas mis v4.1 184 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution trcd this is the active-to-read or -write command delay. This value, in picoseconds, is based on the device selection in the mig tool. Trefi this is the av...

Page 185

Zynq-7000 ap soc and 7 series fpgas mis v4.1 185 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution trcd this is the active-to-read or -write command delay. This value, in picoseconds, is based on the device selection in the mig tool. Trefi this is the av...

Page 186

Zynq-7000 ap soc and 7 series fpgas mis v4.1 186 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution data_io_prim_type this option instantiates ibuf primitives for data (dq) and strobe (dqs) as per banks selected for the interface and also depends on the i...

Page 187

Zynq-7000 ap soc and 7 series fpgas mis v4.1 187 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution clkout0_phase – phase of pll output clkout0. This value is set by the mig tool based on the banks selected for memory interface pins and the frequency of o...

Page 188

Zynq-7000 ap soc and 7 series fpgas mis v4.1 188 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-66 contains parameters set up by the mig tool based on the pinout selected. When making pinout changes, xilinx recommends rerunning the mig tool to...

Page 189

Zynq-7000 ap soc and 7 series fpgas mis v4.1 189 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution phy_0_bitlanes, phy_1_bitlanes, phy_2_bitlanes 12-bit parameter per byte lane used to determine which i/o locations are used to generate the necessary phy ...

Page 190

Zynq-7000 ap soc and 7 series fpgas mis v4.1 190 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution addr_map bank and byte lane position information for the address. 12-bit parameter provided per pin. • [11:8] – bank position. Values of 0, 1, or 2 are sup...

Page 191

Zynq-7000 ap soc and 7 series fpgas mis v4.1 191 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution odt_map bank and byte lane position information for the odt. This parameter is referred to as one of the address/control byte groups. See addr_map descript...

Page 192: Design Guidelines

Zynq-7000 ap soc and 7 series fpgas mis v4.1 192 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution design guidelines guidelines for ddr2 and ddr3 sdram designs are covered in this section. For general pcb routing guidelines, see appendix a, general memor...

Page 193

Zynq-7000 ap soc and 7 series fpgas mis v4.1 193 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution bank and pin selection guides for ddr3 designs the mig tool generates pin assignments for a memory interface based on physical layer rules. Xilinx 7 series...

Page 194

Zynq-7000 ap soc and 7 series fpgas mis v4.1 194 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution ° an unused pin exists in the adjacent byte group (t0/t3) or the ck output is contained in the adjacent byte group. • no more than three vertical banks fro...

Page 195

Zynq-7000 ap soc and 7 series fpgas mis v4.1 195 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution through the frequency backbone to the pll. The system clock input to the pll must come from clock capable i/o. The system clock input can only be used for ...

Page 196

Zynq-7000 ap soc and 7 series fpgas mis v4.1 196 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution power system and plane discontinuities see 7 series fpgas pcb design and pin planning guide (ug483) [ref 12] . Termination these rules apply to termination...

Page 197

Zynq-7000 ap soc and 7 series fpgas mis v4.1 197 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • differential signals should be terminated with the memory device internal termination or an 80Ω differential termination at the load ( figure 1-93 ). For...

Page 198

Zynq-7000 ap soc and 7 series fpgas mis v4.1 198 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • dci (hp banks) or in_term (hr banks) is required at the fpga to meet the specified performance. • the reset_n signal is not terminated. This signal shoul...

Page 199

Zynq-7000 ap soc and 7 series fpgas mis v4.1 199 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • the maximum electrical delay between any address and control signals and the corresponding ck/ck# must be ≤ ±25 ps, with 8 ps being the optimal target. •...

Page 200

Zynq-7000 ap soc and 7 series fpgas mis v4.1 200 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution for example, if an 1,866 rated –3 fpga operates at 1,600 mb/s with a 1,600 rated ddr3 component, the dq to dqs skew limit is ±31.3 ps. If the interface ope...

Page 201

Zynq-7000 ap soc and 7 series fpgas mis v4.1 201 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution for example, if an 1,863 mb/s rated fpga operates at 1600 mb/s with a 1,600 rated ddr3 component, the ck to address/control skew limit is ±94.1 ps. If a 1,...

Page 202

Zynq-7000 ap soc and 7 series fpgas mis v4.1 202 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • sys_rst – this is the main system reset (asynchronous). The reset signal must be applied for a minimum pulse width of 5 ns. • init_calib_complete – this ...

Page 203: Ddr2 Sdram

Zynq-7000 ap soc and 7 series fpgas mis v4.1 203 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution consult the constraints guide for more information. For ddr3 sdram interfaces that have the memory system input clock (sys_clk_p/sys_clk_n) placed on ccio ...

Page 204

Zynq-7000 ap soc and 7 series fpgas mis v4.1 204 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution associated i/os. In a typical ddr2 configuration, eight of these 10 i/os are used for the dqs: one is used for the data mask (dm), and one remains for othe...

Page 205

Zynq-7000 ap soc and 7 series fpgas mis v4.1 205 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • for data widths of 16 with a x8 part, only one set of ck/ck#, cs, odt ports is generated to fit the design in a single bank. • vrn and vrp are used for t...

Page 206

Zynq-7000 ap soc and 7 series fpgas mis v4.1 206 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution system clock, pll location, and constraints the pll is required to be in the bank that supplies the clock to the memory to meet the specified interface per...

Page 207

Zynq-7000 ap soc and 7 series fpgas mis v4.1 207 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution these signals are all set to lvcmos25 and can be altered as needed for the system design. They can be generated and used internally instead of being brough...

Page 208

Zynq-7000 ap soc and 7 series fpgas mis v4.1 208 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution source can be connected directly to the diff_sstl18_ii ccio pins. For more details on usage and required circuitry for lvds and lvds_25 i/o standards, see ...

Page 209

Zynq-7000 ap soc and 7 series fpgas mis v4.1 209 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • dm should be pulled to gnd if odt is used but dm is not driven by the fpga (for scenarios where the data mask is not used or is disabled). I/o standards ...

Page 210: Clocking

Zynq-7000 ap soc and 7 series fpgas mis v4.1 210 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution these rules indicate the maximum electrical delays between ddr2 sdram signals: • the maximum electrical delay between any dq or dm and its associated dqs/d...

Page 211

Zynq-7000 ap soc and 7 series fpgas mis v4.1 211 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • the clock input (sys_clk) can be input on any ccio in the column where the memory interface is located; this includes ccio in banks that do not contain t...

Page 212

Zynq-7000 ap soc and 7 series fpgas mis v4.1 212 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution provides the 100Ω differential receiver termination because the internal diff_term is set to false. To maximize the input noise margin, all rbias resistors...

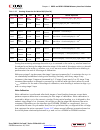

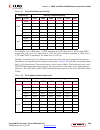

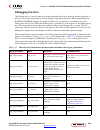

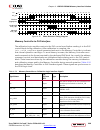

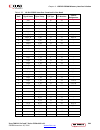

Page 213: Ddr3 Pinout Examples

Zynq-7000 ap soc and 7 series fpgas mis v4.1 213 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution information on sharing bufg clock (phy_clk) the mig 7 series ddr3 design includes an mmcm which outputs the phy_clk on a bufg route. It is not possible to ...

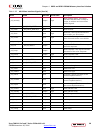

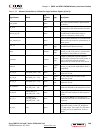

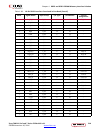

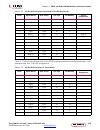

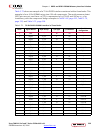

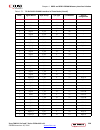

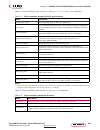

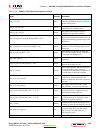

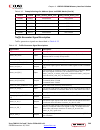

Page 214

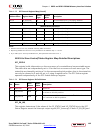

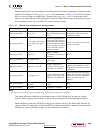

Zynq-7000 ap soc and 7 series fpgas mis v4.1 214 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 1 dqs1_n d_06 n 43 dqs-n 1 dq11 d_05 p 42 – 1 dq10 d_04 n 41 – 1 dq9 d_03 p 40 – 1 dq8 d_02 n 39 – 1 dm1 d_01 p 38 – 1 – d_00 n 37 – 1 dq7 c_11 p 36 – 1 dq...

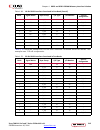

Page 215

Zynq-7000 ap soc and 7 series fpgas mis v4.1 215 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-70 shows an example of a 32-bit ddr3 interface contained within two banks. This example uses 2 gb x8 components. 1 a8 a_08 n 9 – 1 a7 a_07 p 8 dqs-...

Page 216

Zynq-7000 ap soc and 7 series fpgas mis v4.1 216 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 1 – c_06 n 31 dqs-n 1 – c_05 p 30 – 1 – c_04 n 29 – 1 – c_03 p 28 ccio-p 1 – c_02 n 27 ccio-n 1 cke c_01 p 26 ccio-p 1 odt c_00 n 25 ccio-n 1 ras_n b_11 p ...

Page 217

Zynq-7000 ap soc and 7 series fpgas mis v4.1 217 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 2 dq30 d_10 n 47 – 2 dq29 d_09 p 46 – 2 dq28 d_08 n 45 – 2 dqs3_p d_07 p 44 dqs-p 2 dqs3_n d_06 n 43 dqs-n 2 dq27 d_05 p 42 – 2 dq26 d_04 n 41 – 2 dq25 d_0...

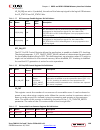

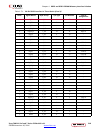

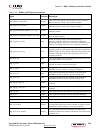

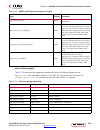

Page 218

Zynq-7000 ap soc and 7 series fpgas mis v4.1 218 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-71 shows an example of a 64-bit ddr3 interface contained within three banks. This example uses four 2 gb x16 components. 2 – b_00 n 13 – 2 dq7 a_11...

Page 219

Zynq-7000 ap soc and 7 series fpgas mis v4.1 219 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 1 dq54 c_10 n 35 – 1 dq53 c_09 p 34 – 1 dq52 c_08 n 33 – 1 dqs6_p c_07 p 32 dqs-p 1 dqs6_n c_06 n 31 dqs-n 1 dq51 c_05 p 30 – 1 dq50 c_04 n 29 – 1 dq49 c_0...

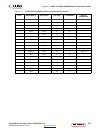

Page 220

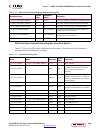

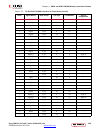

Zynq-7000 ap soc and 7 series fpgas mis v4.1 220 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 1 – a_00 n 1 – 1 vrn – se 0 – 2 vrp – se 49 – 2 – d_11 p 48 – 2 – d_10 n 47 – 2 – d_09 p 46 – 2 – d_08 n 45 – 2 – d_07 p 44 dqs-p 2 – d_06 n 43 dqs-n 2 – d...

Page 221

Zynq-7000 ap soc and 7 series fpgas mis v4.1 221 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 2 ba0 b_04 n 17 – 2 cs_n b_03 p 16 – 2 cke b_02 n 15 – 2 a13 b_01 p 14 – 2 a12 b_00 n 13 – 2 a11 a_11 p 12 – 2 a10 a_10 n 11 – 2 a9 a_09 p 10 – 2 a8 a_08 n...

Page 222

Zynq-7000 ap soc and 7 series fpgas mis v4.1 222 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 3 dq20 c_08 n 33 – 3 dqs2_p c_07 p 32 dqs-p 3 dqs2_n c_06 n 31 dqs-n 3 dq19 c_05 p 30 – 3 dq18 c_04 n 29 – 3 dq17 c_03 p 28 ccio-p 3 dq16 c_02 n 27 ccio-n ...

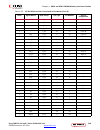

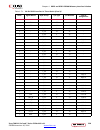

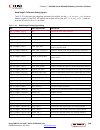

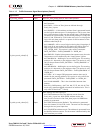

Page 223

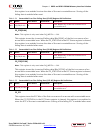

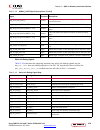

Zynq-7000 ap soc and 7 series fpgas mis v4.1 223 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution table 1-72 shows an example of a 72-bit ddr3 interface contained within three banks. This example is for a 4 gb udimm using nine 4 gb x8 components. The se...

Page 224

Zynq-7000 ap soc and 7 series fpgas mis v4.1 224 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 1 dqs5_p b_07 p 20 dqs-p 1 dqs5_n b_06 n 19 dqs-n 1 dq43 b_05 p 18 – 1 dq42 b_04 n 17 – 1 dq41 b_03 p 16 – 1 dq40 b_02 n 15 – 1 dm5 b_01 p 14 – 1 – b_00 n ...

Page 225

Zynq-7000 ap soc and 7 series fpgas mis v4.1 225 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 2 – c_11 p 36 – 2 – c_10 n 35 – 2 – c_09 p 34 – 2 – c_08 n 33 – 2 – c_07 p 32 dqs-p 2 – c_06 n 31 dqs-n 2 – c_05 p 30 – 2 – c_04 n 29 – 2 – c_03 p 28 ccio-...

Page 226

Zynq-7000 ap soc and 7 series fpgas mis v4.1 226 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 2 a1 a_01 p 2 – 2 a0 a_00 n 1 – 2 vrn – se 0 – 3 vrp – se 49 – 3 dq31 d_11 p 48 – 3 dq30 d_10 n 47 – 3 dq29 d_09 p 46 – 3 dq28 d_08 n 45 – 3 dqs3_p d_07 p ...

Page 227

Zynq-7000 ap soc and 7 series fpgas mis v4.1 227 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution 3 dq11 b_05 p 18 – 3 dq10 b_04 n 17 – 3 dq9 b_03 p 16 – 3 dq8 b_02 n 15 – 3 dm1 b_01 p 14 – 3 – b_00 n 13 – 3 dq7 a_11 p 12 – 3 dq6 a_10 n 11 – 3 dq5 a_09 ...

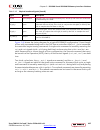

Page 228: Debugging Ddr3/ddr2 Designs

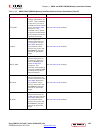

Zynq-7000 ap soc and 7 series fpgas mis v4.1 228 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution debugging ddr3/ddr2 designs calibration failures and data errors can occur for many reasons and the debug of these errors can be time consuming. This secti...

Page 229: Debug Tools

Zynq-7000 ap soc and 7 series fpgas mis v4.1 229 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution answer records for this core can also be located by using the search support box on the main xilinx support web page . To maximize your search results, use...

Page 230

Zynq-7000 ap soc and 7 series fpgas mis v4.1 230 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution debug signals the mig 7 series tool includes a debug signals control option on the fpga options screen. Enabling this feature allows calibration, tap delay...

Page 231: Hardware Debug

Zynq-7000 ap soc and 7 series fpgas mis v4.1 231 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution reference boards various xilinx development boards support mig ip core that include fpga interfaces to a ddr sodimm. These boards can be used to prototype ...

Page 232

Zynq-7000 ap soc and 7 series fpgas mis v4.1 232 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution many of these common issues can also be applied to debugging design simulations. Details are provided on: • general checks • calibration stages • determine...

Page 233

Zynq-7000 ap soc and 7 series fpgas mis v4.1 233 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution • check the reset to ensure the polarity is correct and the signal is clean. The reset signal must be applied for a minimum pulse width of 5 ns. • check te...

Page 234

Zynq-7000 ap soc and 7 series fpgas mis v4.1 234 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution calibration stages memory initialization the phy executes a jedec-compliant ddr2 or ddr3 initialization sequence following the deassertion of system reset....

Page 235

Zynq-7000 ap soc and 7 series fpgas mis v4.1 235 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution determine the failing calibration stage using the vivado logic analyzer feature, configure the device along with debug_nets.Ltx file. This file can be foun...

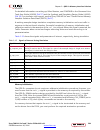

Page 236

Zynq-7000 ap soc and 7 series fpgas mis v4.1 236 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution debug signals table 1-74: ddr2/ddr3 debug signals signal name description ila signals (status) dbg_init_calib_complete signifies memory initialization and ...

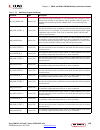

Page 237

Zynq-7000 ap soc and 7 series fpgas mis v4.1 237 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution dbg_rddata_r read data read out of the in_fifo for the dqs group selected through dbg_dqs on the vio. This is a 64-bit bus. This debug port does not captur...

Page 238

Zynq-7000 ap soc and 7 series fpgas mis v4.1 238 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution dbg_wl_po_fine_cnt_by_dqs phaser_out fine taps found during write leveling. Byte capture based on vio dbg_dqs setting. Dbg_wl_po_coarse_cnt_by_dqs phaser_o...

Page 239

Zynq-7000 ap soc and 7 series fpgas mis v4.1 239 ug586 november 30, 2016 www.Xilinx.Com chapter 1: ddr3 and ddr2 sdram memory interface solution dbg_pi_phase_locked_phy4lanes signifies which of the phaser_in lanes has achieved lock. It is a 12-bit bus, three nibble data. Each nibble corresponds to a...

Page 240