Icom IC-F80DS Service Manual - page 7

4 - 1

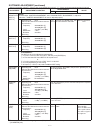

SECTION 4 CIRCUIT DESCRIPTION

4-1 RECEIVER CIRCUITS

4-1-1 ANTENNA SWITCHING CIRCUIT (MAIN UNIT)

The antenna switching circuit toggles the receive line and

the transmit line. This circuit does not allow transmit signals

to enter the receiver circuits.

Received signals from the antenna connector (CHASSIS

UNIT; J1) are passed through a two-stage low-pass filter

(LPF; L522, L523, C565–C569) and applied to the

λ

/

4

type

antenna switching circuit (D203, D510).

While receiving, no voltage is applied to D203 and D510.

Thus, the receive line and the ground are disconnected and

L520 and C564 function as an LPF which leads received

signals to the RF circuits via the limiter (D509).

4-1-2 RF CIRCUITS (MAIN UNIT)

The RF circuits amplify received signals within the range of

frequency coverage and filters off out-of-band signals.

The signals from the antenna switching circuit are passed

through the two-stage tunable bandpass filters (BPF; D506,

D507, L516, L517, C551, C552, C554–C556) to suppress

unwanted signals. The filtered signals are amplified at the

RF amplifier (Q502).

The amplified signals are passed through another two-

stage tunable BPF (D502, D504, D505, L510, C520, C522,

C523, C527, C530, C536, C538) to suppress unwanted

signals again. The filtered signals are then applied to the

1st IF circuit.

4-1-3 1st IF CIRCUITS (MAIN UNIT)

The 1st IF circuits contain the 1st mixer, IF amplifier and

the 1st IF filter circuits, and the 1st IF mixer converts the

received signals into a fixed frequency of the 1st intermedi-

ate frequency (IF) signal. The converted 1st IF signal is fil-

tered at the 1st IF filter, then amplified at the 1st IF amplifier.

The signals from the two-stage tunable BPF are converted

into the 46.35 MHz 1st IF signal at the double-balanced

type 1st mixer (IC500, L503, L504, L506) by being mixed

with the 1st LO signal generated at the RX VCOs (Q600,

D604, D605 for 400–434 MHz, Q601, D606, D607 for 435–

470 MHz).

The 1st IF signal from the 1st mixer is passed through the

crystal filter (FI500) to suppress unwanted signals, and

then amplified at the 1st IF amplifier (Q500). The amplified

1st IF signal is applied to the FM IF IC (IC3, pin 16).

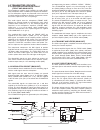

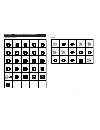

4-1-4 2nd IF AND FM DEMODULATOR CIRCUITS

(MAIN UNIT)

The 1st IF signal is converted into the 2nd IF signal and

demodulated at the detector section in the FM IF IC. The

FM IF IC contains 2nd mixer, limiter amplifier, quadrature

detector, etc. in its package.

The 1st IF signal from the 1st IF amplifier (Q500) is applied

to the mixer section in FM IF IC (IC3, pin 16). The applied

1st IF signal is mixed with the 45.9 MHz 2nd LO signal gen-

erated by tripling the 15.3 MHz PLL reference frequency to

be converted into the 450 kHz 2nd IF signal.

The 2nd IF signal from the mixer section is output from pin 3

and passed through the N/W switches (D13, D14) and a

ceramic filter (FI1 or FI2) to suppress the heterodyne noise.

The N/W switches (D13, D14) toggle the receive mode

wide and narrow according to “NWC” signal from the CPU

(IC307, pin 19). FI1 is used for wide, and FI2 is used for

narrow mode operation.

The filtered signal is applied to IC3 (pin 5) again, and

amplified at the limiter amplifier section and demodulated

by the quadrature detector.

The quadrature detector is a detection method which uses

a ceramic discriminator (X2).

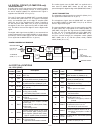

Mixer

RSSI

Quadrature

detector

1st IF from the IF amplifier (Q500)

16

Noise

detector

5V

X2

11

10

IC3

TA31136FN

Filter

amp.

Limiter

amp.

“DET” signal

to the D/A convertor (IC303; pin 1)

“SQL” signal

from the D/A convertor (IC303; pin 2)

• 2ND IF AND DEMODULATOR CIRCUITS

9

“NOIS” signal to the CPU (IC307: pin 37)

“RSSI” signal to the CPU (IC307: pin 50)

“DFIL” signal to the digital IF filter (FI1: DSP UNIT)

13

12

Q14

X1

15.3 MHz

45.9 MHz

BPF

2

3

Q303

D-IF

8

7

3

5

FI2

FI1

N/W

SW

N/W

SW

D14

D13