Lattice Semiconductor LatticeXP2 User Manual - page 24

24

LatticeXP2 Standard

Lattice Semiconductor

Evaluation Board User’s Guide

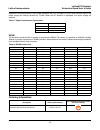

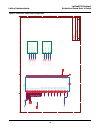

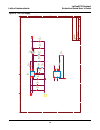

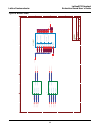

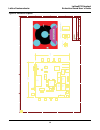

Figure 11. D/A, A/D, 7-Segment and RS232

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

AD

_

C

T

R

L

1

A

D

_C

T

R

L[

0.

.6

]

AD

_

C

T

R

L

0

AD

_

C

T

R

L

2

AD

_

C

T

R

L

3

AD

_

C

T

R

L

4

AI

N

0

A

D

_

D

[0

..1

1

]

AD

_

C

T

R

L

5

AI

N

1

AD

_

C

T

R

L

6

AI

N

2

AD

_

D

0

AI

N

3

AD

_

D

1

AD

_

D

2

AD

_

D

3

A

D

_D

11

AD

_

D

4

A

D

_D

10

DA

[0

..5

]

AD

_

D

9

AD

_

D

8

AD

_

D

7

AD

_

D

6

AD

_

D

5

DA

3

DA

4

DA

5

AI

N

2

VO

U

T

A

VO

U

T

B

VO

U

T

C

VO

U

T

D

DA

0

DA

1

DA

2

C1

-

X7

LV

_R

T

S

_N

C2

+

HV

_

T

X

D

V+

HV

_

R

T

S

_

N

X2

LV

_R

X

D

C1

+

V-

R

S

232_3

LV

_C

T

S

_N

R

S

232_[

0

..

3]

HV

_

C

T

S

_

N

X3

HV

_

R

X

D

X8

SEG

[0

..7

]

R

S

232_1

LV

_T

X

D

R

S

232_2

C2

-

PO

T

[0

..2

]

PO

T

_

C

S

n

P

O

T

2

PO

T

_

U

_

D

n

PO

T

1

PO

T

_

C

L

K

PO

T

0

AI

N

2

PO

T

_

O

U

T

R

S

232_0

SEG

0

S_

F

S_

A

S_

E

S_

D

SEG

3

SEG

4

SEG

5

S_

D

P

SEG

7

S_

C

S_

G

S_

B

SEG

1

SEG

6

SEG

2

A

D

_C

T

R

L[

0.

.6

]

A

D

_D

[0

..

11]

DA

[0

..5

]

R

S

232_[

0

..

3]

SEG

[0

..7

]

PO

T

[0

..2

]

+3

_

3

A

+

3

_3V

+3

_

3

V

+3

_

3

V

+

3_3A

+3

_

3

V

+3

_

3

A

+3

_

3

V

+

3_3V

Ti

tl

e

Siz

e

D

o

c

u

m

e

n

t N

u

m

b

e

r

R

e

v

D

a

te

:

S

h

eet

of

o c > 000 D /A, A/ D , 7 S e g m e n t, R S 2 3 2 L a tt ic e S e m ic o n d u c to r Co rp o ra ti o n 5555 N E M o or e C t H ill s b o ro , O R 97124 B 82 0 Ti tl e Siz e D o c u m e n t N u m b e r R e v D a te : S h eet of o c > 000 D /A, A/ D , 7 S e g m e n t, R S 2 3 2 L a tt ic e S e m ic o n d u c to r Co rp o ra ti o n 5555 N E M o or e C t H ill s b o ro , O R 97124 B 82 0 Ti tl e Siz e D o c u m e n t N u m b e r R e v D a te : S h eet of o c > 000 D /A, A/ D , 7 S e g m e n t, R S 2 3 2 L a tt ic e S e m ic o n d u c to r Co rp o ra ti o n 5555 N E M o or e C t H ill s b o ro , O R 97124 B 82 0 /RTS Select DCE (default) -> shunt pin 1-2 of all headers DTE ->shunt pin 2-3 of all headers RS-232 TXD Select RXD Select /CTS Select AIN0 AIN1 AIN2 AIN3 VOUT3 VOUT2 VOUT1 VOUT0 GND GND AGND AGND GND POT_OUT TXD 1-2: DB9 pin 2 2-3: DB9 pin 3 RXD 1-2: DB9 pin 3 2-3: DB9 pin 2 CTS# 1-2: DB9 pin 7 2-3: DB9 pin 8 RTS# 1-2: DB9 pin 8 2-3: DB9 pin 7 AIN2 J1 8 H E A D E R _ 3 HD 3 x 1 DI J1 8 H E A D E R _ 3 HD 3 x 1 DI 1 2 3 DA C7 6 1 7 U1 0 SO IC 1 6 DI DA C7 6 1 7 U1 0 SO IC 1 6 DI VD D 1 VO U T D 2 VO U T C 3 VR EF L 4 VR EF H 5 VO U T B 6 VO U T A 7 AG N D 8 R ESET S EL 16 RS T n 15 LOA D R E Gn 14 LD A C n 13 CS n 12 CL K 11 SD I 10 GN D 9 TP 7 4 TP TP 7 4 TP J2 2 H E A D E R _ 3 HD 3 x 1 DI J2 2 H E A D E R _ 3 HD 3 x 1 DI 1 2 3 R1 0 0 0 S M /R _0402 DI R1 0 0 0 S M /R _0402 DI C9 7 0. 1u F S M /C _0402 DI C9 7 0. 1u F S M /C _0402 DI C8 3 0. 1u F S M /C _0402 DI C8 3 0. 1u F S M /C _0402 DI C8 8 0. 1u F S M /C _0402 DI C8 8 0. 1u F S M /C _0402 DI TP 7 2 TP TP 7 2 TP TP 2 2 TP TP 2 2 TP R4 8 4 7 0 S M /R _0402 DI R4 8 4 7 0 S M /R _0402 DI R5 1 4 7 0 S M /R _0402 DI R5 1 4 7 0 S M /R _0402 DI C9 8 0. 1u F S M /C _0402 DI C9 8 0. 1u F S M /C _0402 DI R4 9 4 7 0 S M /R _0402 DI R4 9 4 7 0 S M /R _0402 DI TP 2 4 TP TP 2 4 TP C8 4 0. 1u F S M /C _0402 DI C8 4 0. 1u F S M /C _0402 DI R 5 0 470 S M /R _0402 DI R 5 0 470 S M /R _0402 DI TP 2 3 TP TP 2 3 TP R9 6 0 S M /R _0402 DI R9 6 0 S M /R _0402 DI C8 9 0. 1u F S M /C _0402 DI C8 9 0. 1u F S M /C _0402 DI TP 4 5 TP TP 4 5 TP R5 2 4 7 0 S M /R _0402 DI R5 2 4 7 0 S M /R _0402 DI R9 5 0 S M /R _0402 DI R9 5 0 S M /R _0402 DI U9 A D 5220 SO IC 8 DI U9 A D 5220 SO IC 8 DI CL K 1 U/Dn 2 A1 3 GN D 4 W1 5 B1 6 CS n 7 VD D 8 JB 9 JB L O C K DI JB 9 JB L O C K DI R4 2 4 7 0 S M /R _0402 DI R4 2 4 7 0 S M /R _0402 DI TP 4 3 TP TP 4 3 TP U2 Se v e n _ Se g m e n t_ D is p la y DI DIP 1 4 U2 Se v e n _ Se g m e n t_ D is p la y DI DIP 1 4 1 2 3 4 5 6 7 11 12 13 14 8 9 10 U 1 2 M A X 3232 TS S O P 1 6 DI U 1 2 M A X 3232 TS S O P 1 6 DI GN D 15 VC C 16 R1 IN 13 R2 IN 8 T2 IN 10 T1 IN 11 C1 + 1 C1 - 3 C2 + 4 C2 - 5 R1 O U T 12 R2 O U T 9 T1 O U T 14 T2 O U T 7 V+ 2 V- 6 JB 1 1 JB L O C K DI JB 1 1 JB L O C K DI L1 F e rr it e_b e ad B D 0603 DI L1 F e rr it e_b e ad B D 0603 DI C 1 02 0. 1u F S M /C _0402 DI C 1 02 0. 1u F S M /C _0402 DI TP 4 4 TP TP 4 4 TP TP 2 0 TP TP 2 0 TP J1 6 DB 9 -F e m a le DB 9 DI J1 6 DB 9 -F e m a le DB 9 DI 5 9 4 8 3 7 2 6 1 C1 0 0 0. 1u F S M /C _0402 DI C1 0 0 0. 1u F S M /C _0402 DI JB 8 JB L O C K DI JB 8 JB L O C K DI AD S 7 8 4 2 U1 3 SSO P 2 8 DI AD S 7 8 4 2 U1 3 SSO P 2 8 DI AI N 0 1 AI N 1 2 AI N 2 3 AI N 3 4 VR EF 5 AG N D 6 DB 1 1 7 DB 1 0 8 DB 9 9 DB 8 10 DB 7 11 DB 6 12 DB 5 13 DG ND 14 DB 4 15 DB 3 16 DB 2 17 DB 1 18 DB 0 19 RDN 20 CS N 21 WRN 22 BU SY N 23 CL K 24 A0 25 A1 26 VD IG 27 VAN A 28 J2 0 HE A D E R _ 2 HD R 2 X 1 DI J2 0 HE A D E R _ 2 HD R 2 X 1 DI 1 2 L3 F e rr it e_b e ad B D 0603 DI L3 F e rr it e_b e ad B D 0603 DI TP 4 6 TP TP 4 6 TP JB 1 0 JB L O C K DI JB 1 0 JB L O C K DI R5 3 4 7 0 S M /R _0402 DI R5 3 4 7 0 S M /R _0402 DI J1 9 H E A D E R _ 3 HD 3 x 1 DI J1 9 H E A D E R _ 3 HD 3 x 1 DI 1 2 3 TP 1 9 TP TP 1 9 TP J1 7 H E A D E R _ 3 HD 3 x 1 DI J1 7 H E A D E R _ 3 HD 3 x 1 DI 1 2 3 R5 4 4 7 0 S M /R _0402 DI R5 4 4 7 0 S M /R _0402 DI R9 4 0 S M /R _0402 DI R9 4 0 S M /R _0402 DI C 1 01 0. 1u F S M /C _0402 DI C 1 01 0. 1u F S M /C _0402 DI JB 1 2 JB L O C K DI JB 1 2 JB L O C K DI R 2 2 25K PO T DI R 2 2 25K PO T DI C8 2 10u F S M /C _0805 DI C8 2 10u F S M /C _0805 DI C1 0 3 2. 2u F S M /C _0402 DI C1 0 3 2. 2u F S M /C _0402 DI TP 2 1 TP TP 2 1 TP TP 4 7 TP TP 4 7 TP C9 9 0 .1 u F S M /C _0402 DI C9 9 0 .1 u F S M /C _0402 DI TP 3 8 TP TP 3 8 TP