Lattice Semiconductor LCMXO256C-S-EV User Manual - page 4

4

MachXO Starter Evaluation Board

Lattice Semiconductor

User’s Guide

I/O Voltage

The Lattice MachXO device has two sysIO™ banks; each is capable of supporting multiple I/O standards. Each

sysIO bank has its own I/O supply voltage (V

CCIO

), which allows each I/O bank to be completely independent.

Refer to the Lattice MachXO Family Data Sheet for additional information about supported I/O standards. This data

sheet can be downloaded from www.latticesemi.com.

The MachXO Starter Evaluation Board allows individual control of each I/O bank capable of supporting V

CCIO

between 1.2V and 3.3V. The board includes 0 ohm resistors which allow the user to select 3.3V or an adjustable

voltage between 1.25V and 3.3V. During manufacturing, the V

CCIO

banks are set to 3.3V. The adjustable voltage

rail (ADJ) is fixed at 2.5V during manufacturing. Table 1 shows the required resistor population to set the appropri-

ate core and I/O voltages.

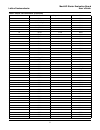

Table 1. Voltage Jumpers/Settings for V

CCIO

and VCC_CORE

Device Clocks

The MachXO Starter Evaluation Board provides a variety of ways to supply clock signals to the MachXO device.

These include a 33MHz on-board crystal oscillator, expansion connectors and 0.1” header pins. The on-board

oscillator is connected to MachXO pin 36, which is a dedicated clock input. The oscillator can be enabled/disabled

via pull up (R144) /down (R145), or through pin 44 of the MachXO. Dedicated clock inputs are also available on the

following pins: 38, 85 and 86. These pins are brought out to test points on the PCB, and to the expansion headers.

Device I/O Banks

MachXO I/O banks 0 and 1 are general purpose I/O banks connected to a combination of test pads, switches,

LEDs and two board expansion headers. The switches consist of two user defined push-button switches and an 8-

position DIP switch. Both types of switches are pulled up to the associated V

CCIO

voltage with 10K

Ω

resistors

(when in the up position) and connected to GND when activated (in the down position). LEDs are active (lit) when

the device I/O is low. Table 2 details the I/O banks 0 and 1 connections.

I/Os listed as GPIO (General Purpose I/O) are connected to 0.1” centered plated through hole, with an associated

GND hole and pads for a pull-up or pull-down resistor. The pull-up pads are located on the component side of the

PCB, and the pull-down pads on the solder side. These pads are sized for 0805 components. Each device I/O is

connected to a test point on the PCB. The PCB silkscreen is marked with the corresponding MachXO 100-TQFP

I/O pin.

3.3V

ADJ

1.2V

VCC_CORE

R157 (default

1

)

R158

R156(default*)

V

CCIO0

R148 (default)

R150

N/A

V

CCIO1

R151 (default)

R152

N/A

1. Default resistor is based on device core I/O voltage, 3.3V for “C” devices, and

1.2V for “E” devices.

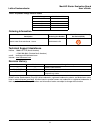

Table 2. Device I/O Connections

Pin #

Pin Name

Expansion Connect

Function/PCB Connect

1

PL2A

J1-5

GPIO

2

PL2B

J1-6

GPIO

3

PL3A

J1-7

GPIO

4

PL3B

J1-8

GPIO

5

PL3C

J1-9

GPIO

6

PL3D

J1-10

GPIO

7

PL4A

J1-11

GPIO

8

PL4B

J1-12

GPIO

9

PL5A

J1-13

GPIO