N.A.T. NAT-MCH Technical Reference Manual - 3 Functional Blocks

NAT-MCH HUB-Module SRIO – Technical Reference Manual

Version 1.5

© N.A.T. GmbH

12

3 Functional Blocks

The NAT-MCH HUB-Module SRIO is divided into a number of functional blocks, which

are described in the following paragraphs.

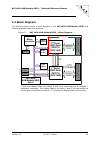

3.1 SRIO Switches

The board is equipped with two IDT CPS-1848 Serial Rapid IO switches, which provide

non-blocking high performance data switching functionality. Data integrity and health

checks are performed by hardware. The CPS-1848 offers 12.5 Gbit/s bandwidth per port

(x4) combined with a low latency packet transport. Additional a flexible port width (x1 or

x4) and different operating baud rates (1.25Gbit/s, 2.5Gbit/s and 3.125Gbit/s) can be

selected.

Each of the twoCPS-1848 SRIO Switches supports 6 ports, each with 4 lanes (SRIO x4),

in order to connect 6 AMCs. Three ports with 4 lanes are used to connect the two

Switches. The first switch supports also a 4-lane port to connect to a second MCH via the

backplane update fabrics D-G. Furthermore two four lane ports of the first switch are

used to supports the optional face plate uplinks.

Both CPS-1848 can be configured by strapping pins, by loading an EEPROM, or by

accessing the TSI register interface via I²C from the microcontroller. A standard

configuration is done by the microprocessor and resistors, by setting the strapping pins.

The values of the strapping signals that are connected to the microcontroller can be

controlled by programming a register in the microcontroller.

These standard settings can be changed by reading the EEPROM after a reset, or by

changing the values of the TSI register interface with the help of the microcontroller (via

I²C interface).

The intended way of standard configuration is that the microcontroller performs the basic

setup via strapping. By default the EEPROM contains basic settings that need to be done

to configure the device regarding the board and system requirements. The MCH firmware

is then able to initialize (or terminate) each port to the needed speed and port width.

The first port of the switch is not connected to the first port of fabric D-G, and so on. To

ease routing of the differential fabrics between the switches and the backplane

connectors the following allocation has been selected.