Radstone PowerPact Hardware Product Manual - page 31

PowerPact6 Processors Family Product Manual

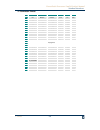

Standard Interfaces

1

st

Edition

5-3

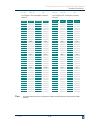

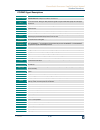

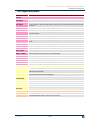

Signal Descriptions

S

IGNAL

D

ESCRIPTION

+5V

+5V power connection

+3.3V

+3.3V power connection

-12V

-12V power connection. Not used by the PowerPact6 processor, but fed to the PMC site

+12V

+12V power connection. Not used by the PowerPact6 processor, but fed to the PMC site

GND

Signal Ground connection

V(IO)

PCI bus I/O voltage reference (+3.3V or +5V)

AD(0) to AD(31)

PCI Multiplexed Address/Data bits 0 to 31

CBE(0)~

PCI Command/Byte Enable 0 for AD(7:0)

CBE(1)~

PCI Command/Byte Enable 1 for AD(15:8)

CBE(2)~

PCI Command/Byte Enable 2 for AD(23:16)

CBE(3)~

PCI Command/Byte Enable 3 for AD(31:24)

INTA~ to INTD~

PCI Interrupt A to Interrupt D signals

REQ~

PCI Master request to system arbiter

SERR~

PCI system Error signal; may be pulsed by any PCI device to report address parity errors, data parity

errors during a Special Cycle, and critical errors other than parity

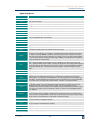

FRAME~

Cycle Frame is driven by the current initiator and indicates the start (when first asserted) and duration

(the duration of its assertion) of a transaction. To determine that bus ownership has been acquired,

the master must sample FRAME~ and IRDY~ both de-asserted and GNT~ asserted on the same

rising edge of the PCI CLK signal. A transaction may consist of one or more data transfers between

the current initiator and the currently-addressed target. FRAME~ is de-asserted when the initiator is

ready to complete the final data phase

IRDY~

Initiator Ready is driven by the current bus master (the initiator of the transaction). During a write,

IRDY~ asserted indicates that the initiator is driving valid data onto the data bus. During a read,

IRDY~ asserted indicates that the initiator is ready to accept data from the currently addressed target.

To determine that bus ownership has been acquired, the master must sample FRAME~ and IRDY~

both de-asserted and GNT~ asserted on the same rising edge of the PCI CLK signal. See also

TRDY~

GNT~

PCI Grant signal

CLK

PCI clock signal (33 or 66MHz)

TRDY~

Target Ready is driven by the currently addressed target. It is asserted when the target is ready to

complete the current data phase (data transfer). A data phase is completed when the target is

asserting TRDY~ and the initiator is asserting IRDY~ at the rising edge of the CLK signal. During a

read, TRDY~ asserted indicates that the target is ready to accept data from the master. Wait states

are inserted in the current data phase until both TRDY~ and IRDY~ are sampled asserted.

PAR

Parity Signal. Driven by the initiator one clock after completion of the address phase or one clock after

the assertion of IRDY~ during each data phase of write transactions. It is driven by the currently

addressed target one clock after the assertion of TRDY~ during each data phase of read

transactions. One clock after completion of the address phase, the initiator drives PAR either high or

low to ensure even parity across the address bus, AD(31:0), and the four Command/Byte Enable

lines, CBE(3:0)~

DEVSEL~

Device Select is asserted by a target when the target has decoded its address. It acts as an input to

the current initiator and the subtractive decoder in the expansion bus bridge. If a master initiates a

transfer and does not detect DEVSEL~ active within six CLK periods, it must assume that the target

cannot respond or that the address is unpopulated. A master-abort results

IDSEL

Initialization Device Select is an input to the PCI device and is used as a chip select during an access

to one of the device's configuration registers

LOCK~

Used by the initiator to lock the currently-addressed target during an atomic transaction series (e.g.

during a semaphore read/modify/write operation)

STOP~

The target asserts STOP~ to indicate that it wishes the initiator to stop the transaction in progress

PERR~

Parity Error signal

M66EN

PCI 66 MHz operation signal