- DL manuals

- Xilinx

- Motherboard

- KCU105

- User Manual

Xilinx KCU105 User Manual

Summary of KCU105

Page 1

Kcu105 pci express control plane trd user guide kucon-trd01 vivado design suite ug918 (v2017.2) july 18, 2017.

Page 2: Revision History

Pci express control plane trd www.Xilinx.Com 2 ug918 (v2017.2) july 18, 2017 revision history the following table shows the revision history for this document. Date version revision 07/18/2017 2017.2 released with vivado design suite 2017.2 with no changes from previous version. 07/17/2017 2017.1 re...

Page 3

Pci express control plane trd www.Xilinx.Com 3 ug918 (v2017.2) july 18, 2017 table of contents revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 chapter 1: introduction overview . . . . . . . . ....

Page 4

Pci express control plane trd www.Xilinx.Com 4 ug918 (v2017.2) july 18, 2017 appendix a: directory structure appendix b: recommended practices and troubleshooting in windows recommended practices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5: Overview

Pci express control plane trd www.Xilinx.Com 5 ug918 (v2017.2) july 18, 2017 chapter 1 introduction this document describes the features and functions of the pci express® control plane targeted reference design (trd). The trd comprises a base design and a user extension design. The user extension de...

Page 6: Features

Pci express control plane trd www.Xilinx.Com 6 ug918 (v2017.2) july 18, 2017 chapter 1: introduction an expresso dma bridge core from northwest logic (nwl) [ref 1] is used to demonstrate pcie-to-axi conversion of transactions. The downstream slaves include a power, voltage, and temperature (pvt) mod...

Page 7

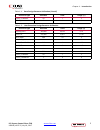

Pci express control plane trd www.Xilinx.Com 7 ug918 (v2017.2) july 18, 2017 chapter 1: introduction gthe3_channel 20 1 5 gthe3_common 5 0 0 table 1-2: user extension design resource utilization resource type available used usage (%) clb registers 484,800 44,395 9.16 clb luts 242,400 27,817 11.48 bl...

Page 8: Requirements

Pci express control plane trd www.Xilinx.Com 8 ug918 (v2017.2) july 18, 2017 chapter 2 setup this chapter identifies the hardware and software requirements, and the preliminary setup procedures required prior to bringing up the targeted reference design. Requirements hardware board and peripherals •...

Page 9: Preliminary Setup

Pci express control plane trd www.Xilinx.Com 9 ug918 (v2017.2) july 18, 2017 chapter 2: setup preliminary setup complete these tasks before bringing up the design. Install the vivado design suite install vivado design suite 2017.2 on the control computer. Follow the installation instructions provide...

Page 10

Pci express control plane trd www.Xilinx.Com 10 ug918 (v2017.2) july 18, 2017 chapter 2: setup x-ref target - figure 2-1 figure 2-1: disable driver signature enforcement ug918_c2_01_040315 send feedback.

Page 11: Set Dip Switches

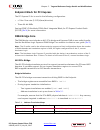

Pci express control plane trd www.Xilinx.Com 11 ug918 (v2017.2) july 18, 2017 chapter 2: setup install drivers 1. From the windows explorer, navigate to the folder in which the reference design is downloaded ( ) and run the setup file with administrator privileges, as shown in figure 2-2 . 2. Click ...

Page 12: Install The Kcu105 Board

Pci express control plane trd www.Xilinx.Com 12 ug918 (v2017.2) july 18, 2017 chapter 2: setup install the kcu105 board 1. Remove all rubber feet and standoffs from the kcu105 board. 2. Power down the host chassis and disconnect the power cord. Caution! Remove the power cord to prevent electrical sh...

Page 13

Pci express control plane trd www.Xilinx.Com 13 ug918 (v2017.2) july 18, 2017 chapter 2: setup 6. Connect the atx power supply to the kcu105 board using the atx power supply adapter cable as shown in figure 2-4 . Note: a 100 vac–240 vac input, 12 vdc 5.0a output external power supply can be substitu...

Page 14: (Linux)

Pci express control plane trd www.Xilinx.Com 14 ug918 (v2017.2) july 18, 2017 chapter 3 bringing up the design this chapter describes how to bring up and test the targeted reference design. Set the host system to boot from the livedvd (linux) note: this section is only applicable to host computers r...

Page 15: Configure The Fpga

Pci express control plane trd www.Xilinx.Com 15 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design configure the fpga while in bios, program the fpga with the bit file: 1. Connect the standard-a plug to micro-b plug usb cable to the jtag port on the kcu105 board and to the control compu...

Page 16

Pci express control plane trd www.Xilinx.Com 16 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design 2. Launch the vivado® integrated design environment (ide) on the control computer: a. Select start > all programs > xilinx design tools > vivado 2017.2 > vivado 2017.2 . B. On the getting ...

Page 17

Pci express control plane trd www.Xilinx.Com 17 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design 3. Open the connection wizard to initiate a connection to the kcu105 board: a. Click open new target ( figure 3-3 ). X-ref target - figure 3-3 figure 3-3: using the user assistance bar to ...

Page 18

Pci express control plane trd www.Xilinx.Com 18 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design 4. Configure the wizard to establish connection with the kcu105 board by selecting the default value on each wizard page. Click next > next > next > finish . A. In the hardware view, right...

Page 19

Pci express control plane trd www.Xilinx.Com 19 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design b. In the bitstream file field, browse to the location of the bit file /kcu105_control_plane/ready_to_test/trd01.Bit and click program (see figure 3-5 ). 5. Check the status of the design ...

Page 20

Pci express control plane trd www.Xilinx.Com 20 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design 6. Exit the bios and let the system boot. 7. On most systems, this gives a second reset on the pcie connector, which should discover the device during enumeration. ° to know that the pcie ...

Page 21

Pci express control plane trd www.Xilinx.Com 21 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design run the design on the host computer this section provides instructions to run the reference design on either a host computer with linux, or a host computer with windows 7. Run the design o...

Page 22

Pci express control plane trd www.Xilinx.Com 22 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design run the design 1. Navigate to the /kcu105_control_plane/software folder and open a terminal. (the trd files were extracted to your in download the targeted reference design files, page 9 )...

Page 23

Pci express control plane trd www.Xilinx.Com 23 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design run the design on a windows 7 host computer after booting the windows os, follow these steps: 1. Repeat the steps in section disable driver signature enforcement, page 9 . 2. Open device m...

Page 24

Pci express control plane trd www.Xilinx.Com 24 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design 3. Open a command prompt with administrator privileges, as shown in figure 3-10 . X-ref target - figure 3-10 figure 3-10: command prompt with administrator privileges ug918_c3_12_040715 se...

Page 25

Pci express control plane trd www.Xilinx.Com 25 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design 4. Navigate to the folder where the reference design is copied: cd 5. Run the batch script quickstart_win7.Bat : quickstart_win7.Bat 6. The screen in figure 3-11 shows the trd setup screen...

Page 26: Test The Reference Design

Pci express control plane trd www.Xilinx.Com 26 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design test the reference design the control and monitoring gui, shown in figure 3-12 , provides information on power and fpga die temperature, (pvtmon is mapped to bar2), pcie express endpoint l...

Page 27: (Windows Only)

Pci express control plane trd www.Xilinx.Com 27 ug918 (v2017.2) july 18, 2017 chapter 3: bringing up the design remove drivers from the host computer (windows only) important: shutdown the host computer and power off the kcu105 board. Then use the following steps to remove the windows drivers. 1. Po...

Page 28: Implementing The Base Design

Pci express control plane trd www.Xilinx.Com 28 ug918 (v2017.2) july 18, 2017 chapter 4 implementing and simulating the design this chapter describes how to implement and simulate the targeted reference design. The time required to do so can vary from system to system depending on the control comput...

Page 29

Pci express control plane trd www.Xilinx.Com 29 ug918 (v2017.2) july 18, 2017 chapter 4: implementing and simulating the design x-ref target - figure 4-1 figure 4-1: base design—project view ug918_c4_01_070717 send feedback.

Page 30

Pci express control plane trd www.Xilinx.Com 30 ug918 (v2017.2) july 18, 2017 chapter 4: implementing and simulating the design 5. In the flow navigator panel, click the generate bitstream option which runs synthesis, implementation, and generates the bit file (see figure 4-2 ). Click yes if a windo...

Page 31

Pci express control plane trd www.Xilinx.Com 31 ug918 (v2017.2) july 18, 2017 chapter 4: implementing and simulating the design implementing the user extension design 1. Open a terminal window on a linux system with the vivado environment set up, or open a vivado tools tcl shell on a windows system....

Page 32

Pci express control plane trd www.Xilinx.Com 32 ug918 (v2017.2) july 18, 2017 chapter 4: implementing and simulating the design 4. In the flow navigator panel, click the generate bitstream option which runs synthesis, implementation, and generates the bit file (see figure 4-4 ). The generated bitstr...

Page 33

Pci express control plane trd www.Xilinx.Com 33 ug918 (v2017.2) july 18, 2017 chapter 4: implementing and simulating the design simulation setup is provided only for the base design and not for the pre-built user extension design. Running simulation using the vivado simulator 1. Open a terminal wind...

Page 34

Pci express control plane trd www.Xilinx.Com 34 ug918 (v2017.2) july 18, 2017 chapter 4: implementing and simulating the design 4. In the flow navigator panel, under simulation, click run simulation and select run behavioral simulation . This generates all the simulation files, loads the vivado simu...

Page 35: Hardware

Pci express control plane trd www.Xilinx.Com 35 ug918 (v2017.2) july 18, 2017 chapter 5 targeted reference design details and modifications this chapter describes the trd hardware design and software components in detail, and provides modifications to add an additional axi block ram controller to th...

Page 36: Dma Bridge Core

Pci express control plane trd www.Xilinx.Com 36 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications endpoint block for pci express the pci express ip for is used in the following configuration: • x1 gen1 line rate (2.5 gt/s/lane/direction) • three 64-bit bars...

Page 37: Axi Block Ram Controller

Pci express control plane trd www.Xilinx.Com 37 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications • during bridge register initialization: ° bridge base low ( 0x210 ) is programmed to (bar0 + 0x8000 ). ° bridge control register ( 0x208 ) is programmed to se...

Page 38

Pci express control plane trd www.Xilinx.Com 38 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications power and temperature monitoring the design uses a sysmon block to provide system power and die temperature monitoring capabilities.The design uses a sysmon bl...

Page 39: Data Flow

Pci express control plane trd www.Xilinx.Com 39 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications data flow this section summarizes the trd data flow. Transmit path 1. The gui opens the driver interface for read/write functionality. 2. The gui issues write ...

Page 40: Software

Pci express control plane trd www.Xilinx.Com 40 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications software software architecture the software component of the trd framework comprises a kernel space base driver module (see figure 5-3 ) and a user space gui t...

Page 41

Pci express control plane trd www.Xilinx.Com 41 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications • gui front end graphical display of statistics collected from the underlying driver through the driver interface. The trd demonstrates the use of pcie in cont...

Page 42

Pci express control plane trd www.Xilinx.Com 42 ug918 (v2017.2) july 18, 2017 chapter 5: targeted reference design details and modifications to enable read access to both block ram controllers, an additional ingress translation aperture can be mapped and the readuserreg function in the driver can be...

Page 43

Pci express control plane trd www.Xilinx.Com 43 ug918 (v2017.2) july 18, 2017 appendix a directory structure the directory structure for the trd is shown in figure a-1 and described in table a-1 . For a detailed description of each folder, see the readme file. X-ref target - figure a-1 figure a-1: t...

Page 44

Pci express control plane trd www.Xilinx.Com 44 ug918 (v2017.2) july 18, 2017 appendix a: directory structure table a-1: directory description folder description readme a txt file that includes revision history information, steps to implement and simulate the design, required vivado® tool software v...

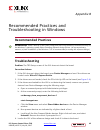

Page 45: Recommended Practices

Pci express control plane trd www.Xilinx.Com 45 ug918 (v2017.2) july 18, 2017 appendix b recommended practices and troubleshooting in windows recommended practices recommended: make a backup of the system image and files using the backup and restore utility of the windows 7 operating system before i...

Page 46: Xilinx Resources

Pci express control plane trd www.Xilinx.Com 46 ug918 (v2017.2) july 18, 2017 appendix c additional resources and legal notices xilinx resources for support resources such as answers, documentation, downloads, and forums, see xilinx support . For continual updates, add the answer record to your myal...

Page 47

Pci express control plane trd www.Xilinx.Com 47 ug918 (v2017.2) july 18, 2017 appendix c: additional resources and legal notices 6. Logicore ip axi block ram (bram) controller product guide ( pg078 ) 7. Logicore ip axi interconnect product guide ( pg059 ) 8. Ultrascale architecture system monitor us...