FPGANETWORKING SGA10GD Reference Manual - 4. Fpga Test Cores

4. FPGA test Cores

The on-board subsystems have been successfully tested using the Xilinx's Coregen

generated cores. User Constraints files were modified according to the boards metric.

Further modifications are discussed below on a per-Core bases.

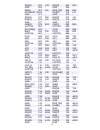

These test Cores are available in the Distribution media:

4.1 PCIEX4 - Endpoint Block for PCI Express v. 1.6

This core implements a PCI Express x4 endpoint, with a completer allowing R/W

access to the on-chip RAM block.

Little modifications were made to the orignal top level design. Red LED's above P1,

P2, and P3 signal failures.

P1 - PLLLKDET lit if the GTP's PLL is not locked.

P2 - LINKUP lit if link training have failed for the lanes.

P3 - CLKLOCK lit if the on-chip PLL_ADV did not locked.

In order to report the presence of all four lanes, J2 has to be closed. Closing J4

forces the FPGA to be reloaded from the Platform Flash when the OS restarts, or the

reset button is pushed on the PC.

Using the Microsoft Windows XP operating system, SGA10GD is found as a new

hardware with the following ID's:

Vendor: 15C6 - BUTE

Device: 106D - 10 Gbps Dual Ethernet Adapter

Revision: 1

Base Class: 02 - Network

Subclass: 80 - Other

4.2 XAUI v. 8.1

The dual-XFP subystems are currently being tested.

4.3 DDR2 - MIG v. 2.0 generated SODIMM teszt core

SGA10GD has a 256 MBytes DDR2-400 SODIMM type MT4HTF3264HY-667

installed by default. The Memory Interface Generator produced a test core that

initialize the module, and performs continuous R/W tests.

Little modifications were made to the orignal top level design.

Red LED's above P1 signals failure.

P1 - phy_init_done lit if failed to initialize the module.

Green LED's above P1, P2 acts as described below.

P1 - error lit if the R/W test does not reveal bit errors. This signal is latched. Close

pin 1 and 20 on the feature connector to reset the core in order to restart the test.

P2 - testcnt(26) Blinks slowly if 200 MHz global clock is OK.

18