FPGANETWORKING SGA10GD Reference Manual - page 9

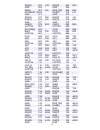

The table below lists the XAUI/XFI converter vs. FPGA connectivity.

Common Signal

Function

FPGA#

PRTAD[0]

Port base address 0AJ11

PRTAD[1]

Port base address 1AP12

PRTAD[2]

Port base address 2AK11

PRTAD[3]

Port base address 3AN12

PRTAD[4]

Port base address 4AM11

U12 Signals

Function

FPGA# U14 Signals

Function

FPGA#

TRSTN[0]

Reset (active low)

AN14 TRSTN[1]

Reset (active low)

AF11

MDIO[0]

MDIO data

AM13 MDIO[1]

MDIO data

AL10

MDC[0]

MDIO clock

AM12 MDC[1]

MDIO clock

AJ10

CDRLOL[0] Loss of Lock in CDR AP14 CDRLOL[1] Loss of Lock in CDR AE11

CMULOL[0] Loss of Lock in CMUAN13 CMULOL[1] Loss of Lock in CMUAH10

TTXON[0]

TX enable

AL11 TTXON[1]

TX enable

AG11

RXDP[0][0] XAUI RX lane 0

D1

RXDP[1][0] XAUI RX lane 0

T1

RXDN[0][0]

C1

RXDN[1][0]

R1

RXDP[0][1] XAUI RX lane 1

A3

RXDP[1][1] XAUI RX lane 1

N1

RXDN[0][1]

A2

RXDN[1][1]

P1

RXDP[0][2] XAUI RX lane 2

A6

RXDP[1][2] XAUI RX lane 2

K1

RXDN[0][2]

A7

RXDN[1][2]

J1

RXDP[0][3] XAUI RX lane 3

A9

RXDP[1][3] XAUI RX lane 3

G1

RXDN[0][3]

A8

RXDN[1][3]

H1

TXDP[0][0] XAUI TX lane 0

E2

TXDP[1][0] XAUI TX lane 0

U2

TXDN[0][0]

D2

TXDN[1][0]

T2

TXDP[0][1] XAUI TX lane 1

B4

TXDP[1][1] XAUI TX lane 1

M2

TXDN[0][1]

B3

TXDN[1][1]

N2

TXDP[0][2] XAUI TX lane 2

B5

TXDP[1][2] XAUI TX lane 2

L2

TXDN[0][2]

B6

TXDN[1][2]

K2

TXDP[0][3] XAUI TX lane 3

B10

TXDP[1][3] XAUI TX lane 3

F2

TXDN[0][3]

B9

TXDN[1][3]

G2

* RXPOLARITY attribute for the MGT has to be changed

** TXPOLARITY attribute for the MGT has to be changed

9