FPGANETWORKING SGA10GD Reference Manual - Contents

Contents

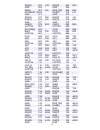

Contents...........................................................................................................................................................................................2

1. Introduction..................................................................................................................................................................................3

1.1 What is SGA10GD?...............................................................................................................................................................3

1.2 What is on-board?..................................................................................................................................................................3

1.3 Conformity.............................................................................................................................................................................4

2. Architecture..................................................................................................................................................................................5

2.1 Power Supply.........................................................................................................................................................................6

2.2 Clock sources.........................................................................................................................................................................7

2.3 Dual XFPs for 10Gbps Ethernet............................................................................................................................................8

2.4 PCI Express x8 endpoint......................................................................................................................................................10

2.5 DDR2 SODIMM RAM........................................................................................................................................................12

2.6 Feature Connector................................................................................................................................................................14

2.7 FPGA Programming.............................................................................................................................................................16

2.7.1 Programming through JTAG.........................................................................................................................................16

2.7.2 Programming from FLASH..........................................................................................................................................16

2.7.3 Partial reconfiguration...................................................................................................................................................17

2.8 Status LEDs.........................................................................................................................................................................17

4. FPGA test Cores.........................................................................................................................................................................18

4.1 PCIEX4 - Endpoint Block for PCI Express v. 1.6...............................................................................................................18

4.2 XAUI v. 8.1..........................................................................................................................................................................18

4.3 DDR2 - MIG v. 2.0 generated SODIMM teszt core............................................................................................................18

4.4 Clock domains......................................................................................................................................................................19

2