I-Lotus RX Oncore User Manual - page 10

Document Number: 403

– GPS – 070

Page | 6

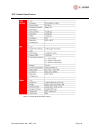

Serial Peripheral Interface (SPI) allows full duplex, synchronous communications with external devices,

slave operation, maximum baud rate of 5.5Mb/s.

USB unit V1.1 compliant, software configurable endpoint setting, USB Suspend/Resume support.

Controller Area Network Interface (CAN) compliant with the CAN specification V2.0 part B (active) and

bit rate can be programmed up to 1 MBaud. (Optional, with this option, this feature shares the same

hardware pins as USB interface)

Inter-IC Interface (I

2

C) Interface provides multi-master and slave functions, support normal and fast

I

2

C mode (400 KHz), 7/10 bit addressing modes. (Optional)

RF Front-end Features:

LOW IF (4MHz) architecture

Compatible with GPS L1 signal

VGA Gain internally regulated

On-chip programmable PLL

3.3

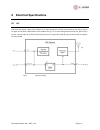

Hardware Interface Overview

The RX Oncore GPS module uses the STA8058 fully embedded GPS engine core chip set. This chipset features 64KB

RAM and 256 KB + 16 KB Flash Memory in a single chip BGA package.

The GPS IC contains a 66-MHz ARM7TDMI 32 bit processor. The RX Oncore uses an internal frequency synthesizer

to create all internal clocks from the 16.368MHz GPS clock. A 32 KHz oscillator is utilized as the real-time-clock

(RTC).

3.4

Power Modes

Software command to drive the device to sleep mode (low power wait for interrupt).

RF will be disabled when device enters sleep mode and is enabled when it wakes up.

To wake up, a command is sent through UART.

Wake up procedure: send any command and wait for device response.

3.4.1 Tracking

Upon power up, the RX Oncore will run in Full Power Mode, and will immediately search for all visible satellites

available.