Lattice Semiconductor MachXO2 User Manual - page 7

Functional Description

IPUG92_01.2, October 2012

7

LPDDR SDRAM Controller User’s Guide

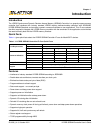

Table 2-2

describes the user interface signals at the top level I/O for Wishbone Interface.

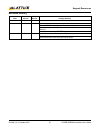

data_mask[(DSIZE/8)-1:0]

N/A

Input

Data mask input for write_data.

sclk

N/A

Output

System clock output. The user logic uses this as a system

clock unless an external clock generator is used.

init_done

High

Output

Initialization done output. It is asserted for one clock cycle

when the core completes the memory initialization routine.

cmd_rdy

High

Output

Command ready output. When asserted, it indicates the core

is ready to accept the next command and address.

data_rdy

High

Output

Data ready output. When asserted, it indicates the core is

ready to receive the write data.

read_data[DSIZE-1:0]

N/A

Output

Read data output from the memory to the user logic.

read_data_valid[1:0]

High

Output

Read data valid output. When asserted, it indicates the data

on the read_data bus is valid. The two bits are independent

outputs of the two DQSBUFH used in the design.

If the LPDDR IO training and alignment is achieved, the bits

of the read_data_valid bus should be identical.

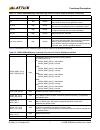

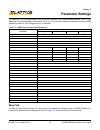

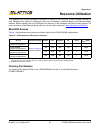

Table 2-2. LPDDR SDRAM Memory Controller Top-Level I/O List for Wishbone Interface

Port Name

I/O

Description

PORT0_ARRD_I[31:0],

PORT1_ARRD_I[31:0]

Input

The address input array used to pass a binary address.

For LPDDR memory of:

1G :

PORT0_ARRD_I[25:0] = valid address

PORT0_ARRD_I[31:26] = unused

512M :

PORT0_ARRD_I[24:0] = valid address

PORT0_ARRD_I[31:25] = unused

256M :

PORT0_ARRD_I[23:0] = valid address

PORT0_ARRD_I[31:24] = unused

128M :

PORT0_ARRD_I[22:0] = valid address

PORT0_ARRD_I[31:23] = unused

64M :

PORT0_ARRD_I[21:0] = valid address

PORT0_ARRD_I[31:22] = unused

PORT0_DAT_I[31:0],

PORT1_DAT_I[31:0]

Input

The data input array used for write data

PORT0_SEL_I[4:0],

PORT1_SEL_I[4:0]

Input

The select input array indicates where valid data is placed on the DAT_I( ) signal array

during WRITE cycles and where it should be present on the DAT_O( ) signal array

during READ cycles.

PORT0_WE_I,

PORT1_WE_I

Input

The write enable Input WE_I indicates whether the current local bus cycle is a

READ or WRITE cycle. The signal is negated during READ cycles and is

asserted during WRITE cycles

PORT0_CYC_I[2:0],

PORT1_CYC_I[2:0]

Input

The Cycle Input CYC_I, when asserted, indicates that a valid bus cycle is in progress.

The signal is asserted for the duration of all bus cycles.

The CYC_I signal is asserted during the first data transfer and remains asserted until

the last data transfer.

PORT0_CLK_I,

PORT1_CLK_I

Input

Wishbone input clocks

RST_I

Input

Wishbone reset

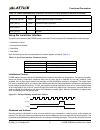

Table 2-1. LPDDR SDRAM Memory Controller Top-Level I/O List for Generic Interface (Continued)

Port Name

Active State

I/O

Description