N.A.T. NAT-MCH Technical Reference Manual - 3 Board Features

NAT-MCH HUB-Module PCIe – Technical Reference Manual

Version 1.2

© N.A.T. GmbH

11

3 Board Features

The NAT-MCH HUB-Module PCIe is divided into a number of functional blocks, which

are described in the following paragraphs.

3.1 PCI Express Switch PLX PEX8748

The NAT-MCH HUB-Module PCIe is equipped with a PLX PEX8748 PCI Express switch,

which provides non-blocking switching at full line rate. Quality of Service (QoS) is

provided by the PEX8748, supporting 2 virtual cannels and 8 traffic classes per port. One

of all ports can be configured as transparent upstream port, and one of all ports can be

configured as non-transparent upstream port.

The PCI Express Switch PEX8748 can be configured by strapping pins, by loading an

EEPROM, or by PCI Express messages from a host. A standard configuration is done by

the microprocessor and resistors by setting the strapping pins. The values of the

strapping signals that are connected to the microcontroller can be controlled by

programming a register in the microcontroller.

These standard settings can be changed by reading the EEPROM after a reset, or by

receiving PCI Express messages from a host.

The EEPROM contains basic configuration information for the PCIe switch as well as user

settings, e.g. upstream port settings. The user settings can be changed by the CPU on

the NAT-MCH BASE-Module.

The /PERST pin is also connected to the microcontroller. The value of this pin can also be

controlled by programming a register in the microcontroller.

The PLX PEX8748 supports 12 ports, per default with 4 lanes (PCIe x4). As shown in the

following tables a certain switch port is not constrained to the according AMC port or MCH

fabric.

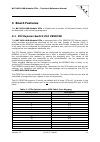

Table 2: PCIe Switch Lane to MCH Fabric Port Mapping

Switch Lanes

MCH Fabric

0

G-4

1

F-4

2

E-4

3

D-4

4

G-3

5

F-3

6

E-3

7

D-3

8

G-2

9

F-2

10

E-2

11

D-2

12

G-1

13

F-1

14

E-1

15

D-1