- DL manuals

- Xilinx

- Transceiver

- RocketIO

- User Manual

Xilinx RocketIO User Manual

Summary of RocketIO

Page 1

R rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 product not recommended for new designs.

Page 2

Rocketio™ transceiver user guide www.Xilinx.Com ug024 (v3.0) february 22, 2007 “xilinx” and the xilinx logo shown above are registered trademarks of xilinx, inc. Any rights not expressly granted herein are reserved. Coolrunner, rocketchips, rocket ip, spartan, statebench, statecad, virtex, xact, xc2...

Page 3

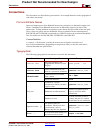

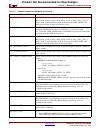

Ug024 (v3.0) february 22, 2007 www.Xilinx.Com rocketio™ transceiver user guide rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 the following table shows the revision history for this document. Date version revision 11/20/01 1.0 • initial xilinx release. 01/23/02 1.1 • updated for typ...

Page 4

Rocketio™ transceiver user guide www.Xilinx.Com ug024 (v3.0) february 22, 2007 06/12/03 2.1 • table 1-2 : added qualifying footnote to xaui 10gfc. • table 1-5 : corrected definition of rxrecclk. • section “rocketio transceiver instantiations” in chapter 1 : added text briefly explaining what the ins...

Page 5

Ug024 (v3.0) february 22, 2007 www.Xilinx.Com rocketio™ transceiver user guide 02/24/04 2.3 • table 2-3, page 41 : added fg676 row to brefclk pin numbers. • figure 2-4, page 47 : added note above figure 2-4 stating, “these local mgt clock input inverters, shown and noted in figure 2-4, are not inclu...

Page 6

Rocketio™ transceiver user guide www.Xilinx.Com ug024 (v3.0) february 22, 2007 02/22/07 3.0 • “example 1a: two-byte clock with dcm,” page 43 : corrected code in two_byte_clk definition (vhdl). • “example 2: four-byte clock,” page 46 : corrected code in dcm instantiation (vhdl). • “rx_loss_of_sync_fs...

Page 7: Table of Contents

Rocketio™ transceiver user guide www.Xilinx.Com 7 ug024 (v3.0) february 22, 2007 schedule of figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 schedule of tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 8

8 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r 8b/10b decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 ports and attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 9

Rocketio™ transceiver user guide www.Xilinx.Com 9 ug024 (v3.0) february 22, 2007 r ports and attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 rxclkcorcnt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 10

10 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r rx_data_width, tx_data_width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90 serdes_10b . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....

Page 11

Rocketio™ transceiver user guide www.Xilinx.Com 11 ug024 (v3.0) february 22, 2007 r setup/hold times of inputs relative to clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129 clock to output delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

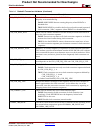

Page 12

12 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r product not recommended for new designs.

Page 13: Schedule of Figures

Rocketio™ transceiver user guide www.Xilinx.Com 13 ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview figure 1-1: rocketio transceiver block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 chapter 2: digital design considerations figure 2-1: refclk/b...

Page 14

14 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r figure 3-3: k28.5+ with pre-emphasis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105 figure 3-4: eye diagram, 10% pre-emphasis, 20" fr4, worst-case conditions . . . . . . 106 f...

Page 15: Schedule of Tables

Rocketio™ transceiver user guide www.Xilinx.Com 15 ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview table 1-1: number of rocketio cores per device type . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 table 1-2: communications standards supported by rocketio transceive...

Page 16

16 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r chapter 3: analog design considerations table 3-1: differential transmitter parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103 table 3-2: pre-emphasis values . . . . . . . . . . . . . ...

Page 17: About This Guide

Rocketio™ transceiver user guide www.Xilinx.Com 17 ug024 (v3.0) february 22, 2007 r preface about this guide the rocketio transceiver user guide provides the product designer with the detailed technical information needed to successfully implement the rocketio™ multi-gigabit transceiver in virtex-ii...

Page 18: For More Information

18 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 preface: about this guide r • chapter 4, “simulation and implementation” — simulation models; implementation tools; debugging and diagnostics. • appendix a, “rocketio transceiver timing model” — timing parameters assoc...

Page 19: Conventions

Rocketio™ transceiver user guide www.Xilinx.Com 19 ug024 (v3.0) february 22, 2007 conventions r conventions this document uses the following conventions. An example illustrates each typographical and online convention. Port and attribute names input and output ports of the rocketio transceiver primi...

Page 21

Rocketio™ transceiver user guide www.Xilinx.Com 21 ug024 (v3.0) february 22, 2007 r chapter 1 rocketio transceiver overview basic architecture and capabilities the rocketio transceiver is based on mindspeed’s skyrail™ technology. Figure 1-1, page 22 , depicts an overall block diagram of the transcei...

Page 22

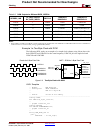

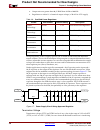

22 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r table 1-3: serial baud rates and the serdes_10b attribute serdes_10b serial baud rate false 1.0 gb/s – 3.125 gb/s true 600 mb/s – 1.0 gb/s figure 1-1: rocketio transceiver blo...

Page 23

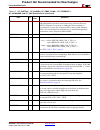

Rocketio™ transceiver user guide www.Xilinx.Com 23 ug024 (v3.0) february 22, 2007 rocketio transceiver instantiations r table 1-4 lists the sixteen gigabit transceiver primitives provided. These primitives carry attributes set to default values for the communications protocols listed in table 1-2 . ...

Page 24: List of Available Ports

24 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r list of available ports the rocketio transceiver primitives contain 50 ports, with the exception of the 46-port gt_ethernet and gt_fibre_chan primitives. The differential seri...

Page 25

Rocketio™ transceiver user guide www.Xilinx.Com 25 ug024 (v3.0) february 22, 2007 list of available ports r refclk i 1 high-quality reference clock driving transmission (reading tx fifo, and multiplied for parallel/serial conversion) and clock recovery. Refclk frequency is accurate to ±100 ppm. When...

Page 26

26 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r rxlossofsync o 2 status related to byte-stream synchronization (rx_loss_of_sync_fsm) if rx_loss_of_sync_fsm = true, rxlossofsync indicates the state of the fsm: bit 1 = loss o...

Page 27

Rocketio™ transceiver user guide www.Xilinx.Com 27 ug024 (v3.0) february 22, 2007 list of available ports r txchardispmode (3) i 1, 2, 4 if 8b/10b encoding is enabled, this bus determines what mode of disparity is to be sent. When 8b/10b is bypassed, this becomes the first bit transmitted (bit “a”) ...

Page 28

28 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r txusrclk2 i 1 clock output from a dcm that clocks transmission data and status and reconfiguration data between the transceiver an the fpga core. The ratio between txusrclk an...

Page 29: Primitive Attributes

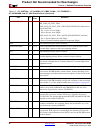

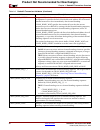

Rocketio™ transceiver user guide www.Xilinx.Com 29 ug024 (v3.0) february 22, 2007 primitive attributes r primitive attributes the primitives also contain attributes set by default to specific values controlling each specific primitive’s protocol parameters. Included are channel-bonding settings (for...

Page 30

30 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r chan_bond_offset integer 0-15 that defines offset (in bytes) from channel bonding sequence for realignment. It specifies the first elastic buffer read address that all channel...

Page 31

Rocketio™ transceiver user guide www.Xilinx.Com 31 ug024 (v3.0) february 22, 2007 primitive attributes r clk_cor_insert_idle_flag true/false controls whether rxrundisp input status denotes running disparity or inserted-idle flag. False: rxrundisp denotes running disparity when rxdata is decoded data...

Page 32

32 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r crc_end_of_pkt note: this attribute is only valid when crc_format = user_mode. K28_0, k28_1, k28_2, k28_3, k28_4, k28_5, k28_6, k28_7, k23_7, k27_7, k29_7, k30_7. End-of-packe...

Page 33

Rocketio™ transceiver user guide www.Xilinx.Com 33 ug024 (v3.0) february 22, 2007 primitive attributes r rx_buffer_use always set to true. Rx_crc_use, tx_crc_use true/false determines if crc is used or not. Rx_data_width, tx_data_width integer (1, 2, or 4). Relates to the data width of the fpga fabr...

Page 34: Modifiable Primitives

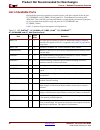

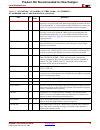

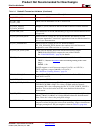

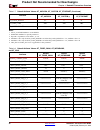

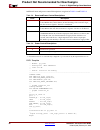

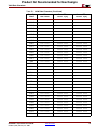

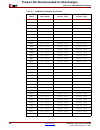

34 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r modifiable primitives as shown in table 1-7 and table 1-8 , only certain attributes are modifiable for any primitive. These attributes help to define the protocol used by the ...

Page 35

Rocketio™ transceiver user guide www.Xilinx.Com 35 ug024 (v3.0) february 22, 2007 modifiable primitives r clk_cor_seq_2_2 00000000000 00000000000 00000000000 clk_cor_seq_2_3 00000000000 00000000000 00000000000 clk_cor_seq_2_4 00000000000 00000000000 00000000000 clk_cor_seq_2_use false false false cl...

Page 36

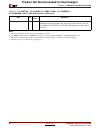

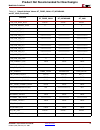

36 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r tx_data_width n (3) 2 n (3) tx_diff_ctrl 500 (2) 500 500 (2) tx_preemphasis 0 (2) 0 0 (2) notes: 1. All gt_custom attributes are modifiable. 2. Modifiable attribute for specif...

Page 37

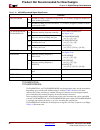

Rocketio™ transceiver user guide www.Xilinx.Com 37 ug024 (v3.0) february 22, 2007 modifiable primitives r clk_cor_keep_idle false (1) false (1) false (1) clk_cor_repeat_wait 2 (1) 1 (1) 1 (1) clk_cor_seq_1_1 00110111100 00100011100 00100011100 clk_cor_seq_1_2 00010010101 00000000000 00000000000 clk_...

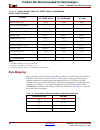

Page 38: Byte Mapping

38 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 1: rocketio transceiver overview r byte mapping most of the 4-bit wide status and control buses correlate to a specific byte of txdata or rxdata. This scheme is shown in table 1-9 . This creates a way to tie al...

Page 39: Clocking

Rocketio™ transceiver user guide www.Xilinx.Com 39 ug024 (v3.0) february 22, 2007 r chapter 2 digital design considerations clocking clock signals there are eight clock inputs into each rocketio transceiver instantiation ( table 2-1 ). Refclk and brefclk are reference clocks generated from an extern...

Page 40

40 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r ±100 ppm or better, with jitter as low as possible. Module 3 of the virtex-ii pro data sheet gives further details. Table 2-1: clock ports clock i/os description brefclk input...

Page 41

Rocketio™ transceiver user guide www.Xilinx.Com 41 ug024 (v3.0) february 22, 2007 clocking r brefclk at speeds of 2.5 gb/s or greater, refclk configuration introduces more than the maximum allowable jitter to the rocketio transceiver. For these higher speeds, brefclk configuration is required. The b...

Page 42

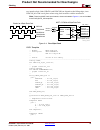

42 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r clock ratio usrclk2 clocks the data buffers. The ability to send/receive parallel data to/from the transceiver at three different widths requires the user to change the freque...

Page 43

Rocketio™ transceiver user guide www.Xilinx.Com 43 ug024 (v3.0) february 22, 2007 clocking r example 1a: two-byte clock with dcm the following hdl codes are examples of a simple clock scheme using 2-byte data with both usrclk and usrclk2 at the same frequency. Usrclk_m is the input for both usrclk a...

Page 44

44 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r rst : in std_logic; usrclk_m : buffer std_logic; refclk : buffer std_logic; lock : out std_logic ); end two_byte_clk; -- architecture two_byte_clk_arch of two_byte_clk is -- -...

Page 45

Rocketio™ transceiver user guide www.Xilinx.Com 45 ug024 (v3.0) february 22, 2007 clocking r u_dcm: dcm port map ( clkin => refclk, clkfb => usrclk_m, dssen => gnd, psincdec => gnd, psen => gnd, psclk => gnd, rst => rst, clk0 => clk0_w, locked => lock ); -- -- bufg instantiation u_bufg: ibufg port m...

Page 46

46 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r .Dssen ( 1'b0 ), .Psclk ( 1'b0 ), .Psen ( 1'b0 ), .Psincdec ( 1'b0 ), .Rst ( 1'b0 ), .Clk0 ( clk_i ), .Clk90 ( ), .Clk180 ( ), .Clk270 ( ), .Clk2x ( ), .Clk2x180 ( ), .Clkdv (...

Page 47

Rocketio™ transceiver user guide www.Xilinx.Com 47 ug024 (v3.0) february 22, 2007 clocking r any interface logic. Both usrclk and usrclk2 are aligned on the falling edge, since usrclk_m is 180 ° out of phase when using local inverters with the transceiver. Note: these local mgt clock input inverters...

Page 48

48 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r i : in std_logic; o : out std_logic ); end component; -- component dcm port ( clkin : in std_logic; clkfb : in std_logic; dssen : in std_logic; psincdec : in std_logic; psen :...

Page 49

Rocketio™ transceiver user guide www.Xilinx.Com 49 ug024 (v3.0) february 22, 2007 clocking r o => refclk ); u2_bufg: bufg port map ( i => clk0_w, o => usrclk_m ); u3_bufg: bufg port map ( i => clkdv_w, o => usrclk2_m_w ); end four_byte_clk_arch; verilog template // module: four_byte_clk // descripti...

Page 50

50 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r .Clk180 ( ), .Clk270 ( ), .Clk2x ( ), .Clk2x180 ( ), .Clkdv ( clkdv2 ), .Clkfx ( ), .Clkfx180 ( ), .Locked ( dcm_locked ), .Psdone ( ), .Status ( ) ); bufg buf1 ( .I ( clkdv2 ...

Page 51

Rocketio™ transceiver user guide www.Xilinx.Com 51 ug024 (v3.0) february 22, 2007 clocking r -- -- pragma translate_off library unisim; use unisim.Vcomponents.All; -- pragma translate_on -- entity one_byte_clk is port ( refclkin : in std_logic; rst : in std_logic; usrclk_m : out std_logic; usrclk2_m...

Page 52

52 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r -- signal gnd : std_logic; signal clk0_w : std_logic; signal clk2x180_w : std_logic; signal usrclk2_m_w : std_logic; signal usrclk_m_w : std_logic; begin gnd '0'; usrclk2_m us...

Page 53

Rocketio™ transceiver user guide www.Xilinx.Com 53 ug024 (v3.0) february 22, 2007 clocking r usrclk_m, usrclk2_m, dcm_locked ); input refclkin; output refclk; output usrclk_m; output usrclk2_m; output dcm_locked; wire refclkin; wire refclk; wire usrclk_m; wire usrclk2_m; wire dcm_locked; wire refclk...

Page 54

54 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r half-rate clocking scheme some applications require serial speeds between 600 mb/s and 1 gb/s. ( refer to xapp572 when considering running in this serial range. ) the transcei...

Page 55

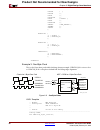

Rocketio™ transceiver user guide www.Xilinx.Com 55 ug024 (v3.0) february 22, 2007 clocking r multiplexed clocking scheme with dcm following configuration of the fpga, some applications might need to change the frequency of its refclk depending on the protocol used. Figure 2-9 shows how the design ca...

Page 56

56 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r rxrecclk rxrecclk is a recovered clock derived by dividing by 20 the received data stream bit rate (whether full-rate or half-rate). If clock correction is bypassed, it is not...

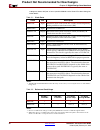

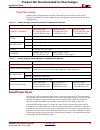

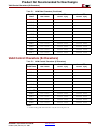

Page 57: Reset/power Down

Rocketio™ transceiver user guide www.Xilinx.Com 57 ug024 (v3.0) february 22, 2007 reset/power down r data path latency with the many configurations of the mgt, the both transmit and receive data path latencies vary. Below are several tables that provide approximate latencies for common configuration...

Page 58

58 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r additional reset and power control descriptions are given in table 2-8 and table 2-9 . Vhdl template -- module: gt_reset -- description: vhdl submodule -- reset for gt -- -- d...

Page 59

Rocketio™ transceiver user guide www.Xilinx.Com 59 ug024 (v3.0) february 22, 2007 reset/power down r process (usrclk2_m, dcm_locked) begin if (usrclk2_m' event and usrclk2_m = '1') then if(dcm_locked = '0') then startup_count elsif (dcm_locked = '1') then startup_count end if; end if; if (usrclk2_m'...

Page 60: 8B/10B Encoding/decoding

60 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r 8b/10b encoding/decoding overview the rocketio transceiver has the ability to encode eight bits into a 10-bit serial stream using standard 8b/10b encoding. This guarantees a d...

Page 61

Rocketio™ transceiver user guide www.Xilinx.Com 61 ug024 (v3.0) february 22, 2007 8b/10b encoding/decoding r ports and attributes txbypass8b10b, rx_decode_use one port and one attribute enable 8b/10b encoding/decoding in the transceiver. Txbypass8b10b is a byte-mapped port that is 1, 2, or 4 bits wi...

Page 62

62 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r txchardispval, txchardispmode txchardispval and txchardispmode are dual-purpose ports for the transmitter depending upon whether 8b/10b encoding is enabled. Table 2-10 shows t...

Page 63

Rocketio™ transceiver user guide www.Xilinx.Com 63 ug024 (v3.0) february 22, 2007 8b/10b encoding/decoding r when txchardispmode is set low, the running disparity is maintained if txchardispval is also set low, but the disparity is inverted before encoding the byte when txcahrdispval is set high. Mo...

Page 64

64 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r in the 8b/10b decoding configuration, rxcharisk asserted high indicates the received byte of data is a control (k) character. Otherwise, the received byte of data is a data ch...

Page 65

Rocketio™ transceiver user guide www.Xilinx.Com 65 ug024 (v3.0) february 22, 2007 8b/10b encoding/decoding r the rocketio core receives this data, but for cases where txchardispval is set high during data transmission, the disp_err bit in chan_bond_seq must also be set high. Receiving vitesse channe...

Page 66

66 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r 8b/10b serial output format the 8b/10b encoding translates a 8-bit parallel data byte to be transmitted into a 10-bit serial data stream. This conversion and data alignment ar...

Page 67: Serdes Alignment

Rocketio™ transceiver user guide www.Xilinx.Com 67 ug024 (v3.0) february 22, 2007 serdes alignment r serdes alignment overview serializer the multi-gigabit transceiver multiplies the reference frequency provided on the reference clock input (refclk) by 20, or by 10 if half-rate operation is selected...

Page 68

68 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r when align_comma_msb is true, the pcs places the comma into the most significant byte (msb) of rxdata in the 2-byte mode. Because the pcs is optimized for the 2-byte mode, som...

Page 69

Rocketio™ transceiver user guide www.Xilinx.Com 69 ug024 (v3.0) february 22, 2007 serdes alignment r figure 2-18 and figure 2-19 show floorplanner layouts for the two examples given above. Figure 2-18: top mgt comma control flip-flop ideal locations figure 2-19: bottom mgt comma control flip-flop id...

Page 70

70 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r pcomma_detect, mcomma_detect these two control attributes define when rxcommadet signals that a comma has been received. When only pcomma_detect is true, rxcommadet signals wh...

Page 71: Clock Recovery

Rocketio™ transceiver user guide www.Xilinx.Com 71 ug024 (v3.0) february 22, 2007 clock recovery r enpcommaalign and enmcommaalign are both set to zero then this signal should not go high. See table 2-13 . Rxchariscomma this signal is similar to rxcharisk, except that it signals that a specific byte...

Page 72

72 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r clock and data recovery the clock/data recovery (cdr) circuits lock to the reference clock automatically if the data is not present. For proper operation, txusrclk must have t...

Page 73

Rocketio™ transceiver user guide www.Xilinx.Com 73 ug024 (v3.0) february 22, 2007 clock recovery r similarly, if rxusrclk is slower than rxrecclk, the buffer fills up over time. The clock correction logic corrects for this by incrementing the read pointer to skip over a removable byte sequence that ...

Page 74

74 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r clock correction may be used with other encoding protocols, but they must have a 10-bit alignment scheme. This is required so the comma detection logic can properly align the ...

Page 75

Rocketio™ transceiver user guide www.Xilinx.Com 75 ug024 (v3.0) february 22, 2007 clock recovery r clk_cor_seq_len to define the ccs length, this attribute takes the integer value 1, 2, 3, or 4. Table 2-16 shows which sequences are used for the four possible settings of clk_cor_seq_len. Clk_cor_inse...

Page 76: Synchronization Logic

76 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r clock correction must occur before another clock correction sequence can occur. If this attribute is 0, no limit is placed on how frequently clock correction can occur. Exampl...

Page 77

Rocketio™ transceiver user guide www.Xilinx.Com 77 ug024 (v3.0) february 22, 2007 synchronization logic r rx_los_invalid_incr, rx_los_threshold these two signals determine how fast an invalid character advances the rxlossofsync fsm counter before loss of sync is considered to have occurred. Rx_los_i...

Page 78

78 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r . Sync_acquired (rxlossofsync = 00) in this state, a counter is decremented by 1 (but not past 0) for a valid received symbol and incremented by rx_los_invalid_incr for an inv...

Page 79

Rocketio™ transceiver user guide www.Xilinx.Com 79 ug024 (v3.0) february 22, 2007 channel bonding (channel alignment) r channel bonding (channel alignment) overview some gigabit i/o standards such as xaui specify the use of multiple transceivers in parallel for even higher data rates. Words of data ...

Page 80

80 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r channel bonding (alignment) operation channel bonding is the technique of tying several serial channels together to create one aggregate channel. Several channels are fed on t...

Page 81

Rocketio™ transceiver user guide www.Xilinx.Com 81 ug024 (v3.0) february 22, 2007 channel bonding (channel alignment) r table 2-19 shows different settings for chan_bond_one_shot and enchansync in master and slave applications. Ports and attributes chan_bond_mode an mgt can be designated as one of t...

Page 82

82 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r these cbss should be unique from other delimiters in the data stream, including clock correction sequence, idle, start of frame, and end of frame. As with clock correction, th...

Page 83

Rocketio™ transceiver user guide www.Xilinx.Com 83 ug024 (v3.0) february 22, 2007 channel bonding (channel alignment) r chbonddone this port indicates when a channel alignment has occurred in the mgt. When it is asserted, rxdata is valid after rxclkcorcnt goes to a 101 . Note: the slave's rxclkcorcn...

Page 84

84 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r crc (cyclic redundancy check) overview cyclic redundancy check (crc) is a procedure to detect errors in the received data. The rocketio transceiver crc logic supports the 32-b...

Page 85

Rocketio™ transceiver user guide www.Xilinx.Com 85 ug024 (v3.0) february 22, 2007 crc (cyclic redundancy check) r crc latency enabling crc increases the transmission latency from txdata to txp and txn. The enabling of crc does not affect the latency from rxp and rxn to rxdata. The typical and maximu...

Page 86

86 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r signals an error by asserting rxcrcerr high at the same time rxcheckingcrc goes high. User logic determines the procedure that is invoked when a crc error occurs. Note: data l...

Page 87

Rocketio™ transceiver user guide www.Xilinx.Com 87 ug024 (v3.0) february 22, 2007 crc (cyclic redundancy check) r designs should generate only the /k28.5/d16.2/ idle sequence for transmission, never /k28.5/d5.6/. When the rocketio crc determines that the running disparity must be inverted to satisfy...

Page 88

88 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r the crc is calculated with certain bits masked in lrh and grh, depending on whether the packet is local or global. The size of these headers is shown in table 2-21 . The crc c...

Page 89: Fabric Interface (Buffers)

Rocketio™ transceiver user guide www.Xilinx.Com 89 ug024 (v3.0) february 22, 2007 fabric interface (buffers) r txforcecrcerr, tx_crc_force_value to test the crc logic in either the mgt or the fpga fabric, txforcecrcerr and tx_crc_force_value may be used to invoke a crc error. When txforcecrcerr is a...

Page 90: Miscellaneous Signals

90 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r ports and attributes txbuferr when high, this port indicates that a transmit buffer underflow or overflow has occurred. Once set high, txreset must be asserted to clear this b...

Page 91

Rocketio™ transceiver user guide www.Xilinx.Com 91 ug024 (v3.0) february 22, 2007 miscellaneous signals r termination_imp receive termination on-chip termination is provided at the receiver, eliminating the need for external termination. The receiver includes programmable on-chip termination circuit...

Page 92

92 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r the second loopback path is a parallel path that checks only the digital circuitry. When the parallel option is enabled, the serial loopback path is disabled. However, the tra...

Page 93: Other Important Design Notes

Rocketio™ transceiver user guide www.Xilinx.Com 93 ug024 (v3.0) february 22, 2007 other important design notes r other important design notes receive data path 32-bit alignment the rocketio transceiver uses the attribute align_comma_msb to align protocol delimiters with the use of comma characters (...

Page 94

94 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r when rxdata is 32-bit aligned, the logic should pass rxdata though to the protocol logic without modification. A properly aligned data flow is shown in figure 2-29 . When rxda...

Page 95

Rocketio™ transceiver user guide www.Xilinx.Com 95 ug024 (v3.0) february 22, 2007 other important design notes r 32-bit alignment design the following example code illustrates one way to create the logic to properly align 32-bit wide data with a comma in bits [31:24] for brevity, most status bits ar...

Page 96

96 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r // rxchariscomma3 -- rxchariscomma[3] // rxchariscomma1 -- rxchariscomma[1] // module align_comma_32 ( aligned_data, aligned_rxisk, sync, usrclk2, rxreset, rxdata, rxisk, rxre...

Page 97

Rocketio™ transceiver user guide www.Xilinx.Com 97 ug024 (v3.0) february 22, 2007 other important design notes r end else begin if ( count && ( wait_to_sync != 4'b0000 ) ) wait_to_sync if ( rxcommadet ) count end end // this process maintains output sync, which indicates // when outgoing aligned_dat...

Page 98

98 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r aligned_data[31:0] }; aligned_rxisk[3:0] byte_sync end else begin aligned_data[31:0] aligned_rxisk end end end endmodule // align_comma_32 vhdl -- * -- ***********************...

Page 99

Rocketio™ transceiver user guide www.Xilinx.Com 99 ug024 (v3.0) february 22, 2007 other important design notes r -- usrclk2 -- rxusrclk2 -- rxreset -- rxreset -- rxdata[31:0] rxdata[31:0] -- (commas aligned to -- [31:24] or [15:8]) -- rxisk[3:0] - rxcharisk[3:0] -- rxrealign -- rxrealign -- rxcommad...

Page 100

100 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r -- is, upon an asserted rxrealign -- or rxcommadet. Process (usrclk2) begin if (usrclk2'event and usrclk2 = '1') then if (rxreset = '1') then wait_to_sync count else if (rxre...

Page 101

Rocketio™ transceiver user guide www.Xilinx.Com 101 ug024 (v3.0) february 22, 2007 other important design notes r -- byte_sync=0 state. Process (usrclk2, rxreset) begin if (rxreset = '1') then rxdata_reg rxdata_hold rxisk_reg rxisk_hold byte_sync elsif (usrclk2'event and usrclk2 = '1') then rxdata_r...

Page 102

102 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 2: digital design considerations r product not recommended for new designs.

Page 103: Analog Design Considerations

Rocketio™ transceiver user guide www.Xilinx.Com 103 ug024 (v3.0) february 22, 2007 r chapter 3 analog design considerations serial i/o description the rocketio transceiver transmits and receives serial differential signals. This feature operates at a nominal supply voltage of 2.5 vdc. A serial diffe...

Page 104: Pre-Emphasis Techniques

104 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r pre-emphasis techniques in pre-emphasis, the initial differential voltage swing is boosted to create a stronger rising or falling waveform. This method compensates for high fr...

Page 105

Rocketio™ transceiver user guide www.Xilinx.Com 105 ug024 (v3.0) february 22, 2007 pre-emphasis techniques r figure 3-2: alternating k28.5+ with no pre-emphasis figure 3-3: k28.5+ with pre-emphasis ug024_17_020802 ug024_18_020802 logic high strong high strong low logic low product not recommended fo...

Page 106

106 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r figure 3-4: eye diagram, 10% pre-emphasis, 20" fr4, worst-case conditions figure 3-5: eye diagram, 33% pre-emphasis, 20" fr4, worst-case conditions ug024_36_031803 ug024_37_03...

Page 107: Differential Receiver

Rocketio™ transceiver user guide www.Xilinx.Com 107 ug024 (v3.0) february 22, 2007 differential receiver r differential receiver the differential receiver accepts the v p and v n signals, carrying out the difference calculation v p – v n electronically. All input data must be differential and nomina...

Page 108: Clock and Data Recovery

108 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r deterministic jitter (dj) is data pattern dependant jitter, attributed to a unique source (e.G., inter symbol interference (isi) due to loss effects of the media). Dj is linea...

Page 109: Pcb Design Requirements

Rocketio™ transceiver user guide www.Xilinx.Com 109 ug024 (v3.0) february 22, 2007 pcb design requirements r an additional feature of cdr is its ability to accept an external precision clock, refclk, which either acts to clock incoming data or to assist in synchronizing the derived rxrecclk. For fur...

Page 110

110 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r ♦ output noise no greater than 40 μ v rms from 10 hz to 100 khz ♦ regulation to within 2% of nominal output voltage (± 50 mv for 2.5v supply) voltage regulators in this catego...

Page 111

Rocketio™ transceiver user guide www.Xilinx.Com 111 ug024 (v3.0) february 22, 2007 pcb design requirements r with a transceiver from another vendor, termination voltage can be dictated by the specifications of the other transceiver. In cases where the rocketio transceiver is interfacing with another...

Page 112

112 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r cases, as ferrite beads are not included inside the package in any device. Table boxes labeled “external” denote a device for which the user must provide power filtering capac...

Page 113

Rocketio™ transceiver user guide www.Xilinx.Com 113 ug024 (v3.0) february 22, 2007 pcb design requirements r avccauxtx, and avccauxrx supplies. The ferrite beads are mounted at the sixteen “l[ n ]” locations. The device in figure 3-10 and figure 3-11 is an fg456 package, which also has eight transce...

Page 114

114 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r figure 3-10: example power filtering pcb layout for four mgts, in device with external capacitors, top layer product not recommended for new designs.

Page 115

Rocketio™ transceiver user guide www.Xilinx.Com 115 ug024 (v3.0) february 22, 2007 pcb design requirements r high-speed serial trace design routing serial traces all rocketio transceiver i/os are placed on the periphery of the bga package to facilitate routing and inspection (since jtag is not avail...

Page 116

116 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r routing of high-speed serial traces should be on signal layers that share a reference plane. If the signal layers do not share a reference plane, a capacitor of value 0.01 μ f...

Page 117

Rocketio™ transceiver user guide www.Xilinx.Com 117 ug024 (v3.0) february 22, 2007 pcb design requirements r ac and dc coupling ac coupling (use of dc blocking capacitors in the signal path) should be used in cases where transceiver differential voltages are compatible, but common mode voltages are ...

Page 118

118 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r the rocketio differential receiver produces the best bit-error rates when its common- mode voltage falls between 1.6v and 1.8v. When the receiver is ac-coupled to the line, v ...

Page 119

Rocketio™ transceiver user guide www.Xilinx.Com 119 ug024 (v3.0) february 22, 2007 pcb design requirements r reference clock a high degree of accuracy is required from the reference clock. For this reason, it is required that one of the oscillators listed in this section be used: epson eg-2121ca 2.5...

Page 120: Other Important Design Notes

120 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 3: analog design considerations r other important design notes powering the rocketio transceivers important! All rocketio transceivers in the fpga, whether instantiated in the design or not, must be connected ...

Page 121: Simulation Models

Rocketio™ transceiver user guide www.Xilinx.Com 121 ug024 (v3.0) february 22, 2007 r chapter 4 simulation and implementation simulation models smartmodels smartmodels are encrypted versions of the actual hdl code. These models allow the user to simulate the actual functionality of the design without...

Page 122

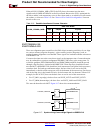

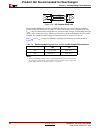

122 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 4: simulation and implementation r figure 4-1: xc2vp2 implementation chbondi chbondo chbondi chbondo chbondi chbondo chbondi chbondo slave_2_hops slave_1_hop slave_1_hop master ug024_08_020802 top of device bo...

Page 123: Mgt Package Pins

Rocketio™ transceiver user guide www.Xilinx.Com 123 ug024 (v3.0) february 22, 2007 mgt package pins r mgt package pins the mgt is a hard core placed in the fpga fabric; all package pins for the mgts are dedicated on the virtex-ii pro device. This is shown in the package pin diagrams in the virtex-ii...

Page 124

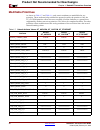

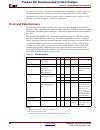

124 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 4: simulation and implementation r . Table 4-2: loc grid & package pins correlation for fg676, ff896, and ff1152 loc constraints fg676 ff896 ff1152 2vp20 /2vp30 2vp40 2vp7 /2vp20 2vp30 2vp20 /2vp30 2vp40 2vp50...

Page 125

Rocketio™ transceiver user guide www.Xilinx.Com 125 ug024 (v3.0) february 22, 2007 mgt package pins r table 4-3: loc grid & package pins correlation for ff1517 and ff1704 loc constraints ff1517 ff1704 2vp40 2vp50 2vp70 2vp70/2vp100 gt_x0_y0 aw36, aw35, aw34, aw33 aw36, aw35, aw34, aw33 aw36, aw35, a...

Page 126

126 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 chapter 4: simulation and implementation r product not recommended for new designs.

Page 127

Rocketio™ transceiver user guide www.Xilinx.Com 127 ug024 (v3.0) february 22, 2007 r appendix a rocketio transceiver timing model this appendix explains all of the timing parameters associated with the rocketio™ transceiver core. It is intended to be used in conjunction with module 3 of the virtex-i...

Page 128

128 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix a: rocketio transceiver timing model r figure a-1: rocketio transceiver block diagram fpga fabric multi-gigabit transceiver core serializer rxp txp clock manager power down package pins deserializer comma det...

Page 129: Timing Parameters

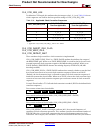

Rocketio™ transceiver user guide www.Xilinx.Com 129 ug024 (v3.0) february 22, 2007 timing parameters r timing parameters parameter designations are constructed to reflect the functions they perform, as well as the i/o signals to which they are synchronous. The following subsections explain the meani...

Page 130

130 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix a: rocketio transceiver timing model r clock pulse width parametername format: t x pwh = minimum pulse width, high state t x pwl = minimum pulse width, low state where x = ref (refclk) tx (txusrclk) tx2 (txus...

Page 131

Rocketio™ transceiver user guide www.Xilinx.Com 131 ug024 (v3.0) february 22, 2007 timing parameter tables and diagram r table a-3: parameters relative to the rx user clock2 (rxusrclk2) parameter function signals setup/hold: t gcck _rrst/t gckc _rrst control input rxreset t gcck _rpol/t gckc _rpol c...

Page 132

132 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix a: rocketio transceiver timing model r t gcck _trst/t gckc _trst control inputs txreset t gcck _tkch/t gckc _tkch control inputs txcharisk[3:0] t gcck _tcdm/t gckc _tcdm control inputs txchardispmode[3:0] t g...

Page 133

Rocketio™ transceiver user guide www.Xilinx.Com 133 ug024 (v3.0) february 22, 2007 timing parameter tables and diagram r figure a-2: rocketio transceiver timing relative to clock edge clock control inputs control outputs data outputs data inputs t xgwh t gcck t xgwl t gckc t gckco t gckdo t gdck t g...

Page 134

134 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix a: rocketio transceiver timing model r product not recommended for new designs.

Page 135: 8B/10B Valid Characters

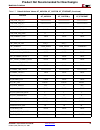

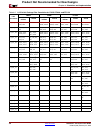

Rocketio™ transceiver user guide www.Xilinx.Com 135 ug024 (v3.0) february 22, 2007 r appendix b 8b/10b valid characters 8b/10b encoding includes a set of data characters and k-characters. Eight-bit values are coded into 10-bit values keeping the serial line dc balanced. K-characters are special data...

Page 136

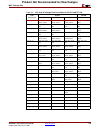

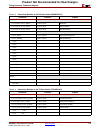

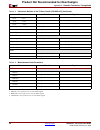

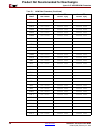

136 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix b: 8b/10b valid characters r d19.0 000 10011 110010 1011 110010 0100 d20.0 000 10100 001011 1011 001011 0100 d21.0 000 10101 101010 1011 101010 0100 d22.0 000 10110 011010 1011 011010 0100 d23.0 000 10111 111...

Page 137

Rocketio™ transceiver user guide www.Xilinx.Com 137 ug024 (v3.0) february 22, 2007 valid data characters r d18.1 001 10010 010011 1001 010011 1001 d19.1 001 10011 110010 1001 110010 1001 d20.1 001 10100 001011 1001 001011 1001 d21.1 001 10101 101010 1001 101010 1001 d22.1 001 10110 011010 1001 01101...

Page 138

138 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix b: 8b/10b valid characters r d17.2 010 10001 100011 0101 100011 0101 d18.2 010 10010 010011 0101 010011 0101 d19.2 010 10011 110010 0101 110010 0101 d20.2 010 10100 001011 0101 001011 0101 d21.2 010 10101 101...

Page 139

Rocketio™ transceiver user guide www.Xilinx.Com 139 ug024 (v3.0) february 22, 2007 valid data characters r d16.3 011 10000 011011 0011 100100 1100 d17.3 011 10001 100011 1100 100011 0011 d18.3 011 10010 010011 1100 010011 0011 d19.3 011 10011 110010 1100 110010 0011 d20.3 011 10100 001011 1100 00101...

Page 140

140 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix b: 8b/10b valid characters r d17.4 100 10001 100011 1101 100011 0010 d18.4 100 10010 010011 1101 010011 0010 d19.4 100 10011 110010 1101 110010 0010 d20.4 100 10100 001011 1101 001011 0010 d21.4 100 10101 101...

Page 141

Rocketio™ transceiver user guide www.Xilinx.Com 141 ug024 (v3.0) february 22, 2007 valid data characters r d18.5 101 10010 010011 1010 010011 1010 d19.5 101 10011 110010 1010 110010 1010 d20.5 101 10100 001011 1010 001011 1010 d21.5 101 10101 101010 1010 101010 1010 d22.5 101 10110 011010 1010 01101...

Page 142

142 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix b: 8b/10b valid characters r d19.6 110 10011 110010 0110 110010 0110 d20.6 110 10100 001011 0110 001011 0110 d21.6 110 10101 101010 0110 101010 0110 d22.6 110 10110 011010 0110 011010 0110 d23.6 110 10111 111...

Page 143

Rocketio™ transceiver user guide www.Xilinx.Com 143 ug024 (v3.0) february 22, 2007 valid control characters (k-characters) r valid control characters (k-characters) d20.7 111 10100 001011 0111 001011 0001 d21.7 111 10101 101010 1110 101010 0001 d22.7 111 10110 011010 1110 011010 0001 d23.7 111 10111...

Page 144

144 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix b: 8b/10b valid characters r product not recommended for new designs.

Page 145: Related Online Documents

Rocketio™ transceiver user guide www.Xilinx.Com 145 ug024 (v3.0) february 22, 2007 r appendix c related online documents the documents described in this appendix are accessible on the xilinx website at www.Xilinx.Com . Document links shown in blue are clickable in this pdf file, providing easy acces...

Page 146

146 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix c: related online documents r a backplane bus. Utilization of a hardware test-and-set lock mechanism, along with a software protocol to test for a semaphore grant prior to accessing the shared memory, guarant...

Page 147

Rocketio™ transceiver user guide www.Xilinx.Com 147 ug024 (v3.0) february 22, 2007 application notes r in this document uses the ppc405 core device control register (dcr) bus interface to implement a simple solution with a minimum of fpga resources. Xapp661: rocketio transceiver bit-error rate teste...

Page 148

148 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix c: related online documents r xapp670: minimizing receiver elastic buffer delay in the virtex-ii pro rocketio transceiver this application note describes a design that reduces latency through the receive elas...

Page 149: Characterization Reports

Rocketio™ transceiver user guide www.Xilinx.Com 149 ug024 (v3.0) february 22, 2007 characterization reports r this application note describes how to use the rocketio multi-gigabit transceivers available in the virtex-ii pro family of fpga devices to implement a transmitter that can support both sd-s...

Page 150: White Papers

150 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix c: related online documents r spice models can be accessed from the xilinx download center at: http://www.Xilinx.Com/xlnx/xil_sw_updates_home.Jsp . Select hspice and eldo models and then virtex-ii pro from th...

Page 151

Rocketio™ transceiver user guide www.Xilinx.Com 151 ug024 (v3.0) february 22, 2007 white papers r wp160: emulating external serdes devices with embedded rocketio transceivers the virtex-ii pro platform fpga provides an attractive single-chip solution to serial transceiver design problems that previo...

Page 152

152 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 appendix c: related online documents r product not recommended for new designs.

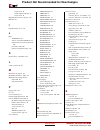

Page 153: Numerics

Rocketio™ transceiver user guide www.Xilinx.Com 153 ug024 (v3.0) february 22, 2007 numerics 8b/10b encoding/decoding bypassing 66 decoder 60 encoder 60 overview 60 ports and attributes 61 serial output format 66 8b/10b valid characters 135 a ac and dc coupling 117 attributes & ports (by function) 8b...

Page 154

154 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r 2-byte clock 43 32-bit alignment design 98 4-byte clock 47 high-speed serial trace design 115 hspice 121 i implementation tools 121 j jitter and brefclk 41 and use of dcm with refclk 39 deterministic and random, def...

Page 155

Rocketio™ transceiver user guide www.Xilinx.Com 155 ug024 (v3.0) february 22, 2007 r t termination voltage 110 timing parameters 129 total jitter (dj + rj) 107 transmitter and elastic (receiver) buffers 89 transmitter buffer (fifo) 89 u user guide conventions online references 20 port and attribute ...

Page 156

156 www.Xilinx.Com rocketio™ transceiver user guide ug024 (v3.0) february 22, 2007 r product not recommended for new designs.