- DL manuals

- Xilinx

- Transceiver

- RocketIO

- User Manual

Xilinx RocketIO User Manual

Summary of RocketIO

Page 1

R rocketio™ transceiver user guide ug024 (v1.5) october 16, 2002.

Page 2

Rocketio™ transceiver user guide www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 the xilinx logo shown above is a registered trademark of xilinx, inc. The shadow x shown above is a trademark of xilinx, inc. "xilinx" and the xilinx logo are registered trademarks of xilinx, inc. Any rights...

Page 3

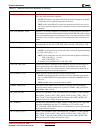

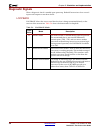

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com rocketio™ transceiver user guide 1-800-255-7778 rocketio™ transceiver user guide ug024 (v1.5) october 16, 2002 the following table shows the revision history for this document. Date version revision 11/20/01 1.0 initial xilinx release. 01/23/02 1.1 update...

Page 4

Rocketio™ transceiver user guide www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778.

Page 5: Contents

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 5 rocketio™ transceiver user guide 1-800-255-7778 schedule of figures ................................................................................................................... 9 schedule of tables ...................................................

Page 6

6 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide r brefclk ................................................................................................................................ 50 half-rate clocking scheme ........................................

Page 7

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 7 rocketio™ transceiver user guide 1-800-255-7778 r high-speed serial trace design.......................................................................................... 91 routing serial traces ............................................................

Page 8

8 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide r.

Page 9: Figures

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 9 rocketio™ transceiver user guide 1-800-255-7778 chapter 1: introduction chapter 2: rocketio transceiver overview figure 2-1: rocketio transceiver block diagram ................................................................. 16 figure 2-2: clock correc...

Page 10

10 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide r figure 4-9: example power filtering pcb layout for four mgts, bottom layer ........... 91 figure 4-10: single-ended trace geometry ..........................................................................

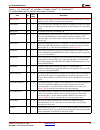

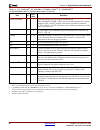

Page 11: Tables

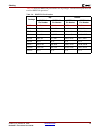

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 11 rocketio™ transceiver user guide 1-800-255-7778 chapter 1: introduction chapter 2: rocketio transceiver overview table 2-1: rocketio cores ........................................................................................................... 15 ta...

Page 12

12 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide r table 4-4: cdr parameters ......................................................................................................... 88 table 4-5: transceiver power supplies ................................

Page 13: Introduction

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 13 rocketio™ transceiver user guide 1-800-255-7778 r chapter 1 introduction rocketio features the rocketio™ transceiver’s flexible, programmable features allow a multi-gigabit serial transceiver to be easily integrated into any virtex-ii pro design: • var...

Page 14: In This User Guide

14 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 1: introduction r in this user guide the rocketio transceiver user guide contains these sections: • chapter 1, introduction — this chapter. • chapter 2, rocketio transceiver overview — an overview...

Page 15

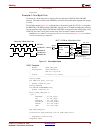

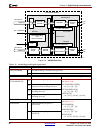

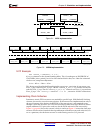

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 15 rocketio™ transceiver user guide 1-800-255-7778 r chapter 2 rocketio transceiver overview basic architecture and capabilities the rocketio transceiver is based on mindspeed’s skyrail™ technology. Figure 2-1, page 16 , depicts an overall block diagram o...

Page 16

16 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 2: rocketio transceiver overview r table 2-3: serial baud rates and the serdes_10b attribute serdes_10b serial baud rate false 800 mb/s – 3.125 gb/s true 622 mb/s – 1.0 gb/s figure 2-1: rocketio t...

Page 17: Clock Synthesizer

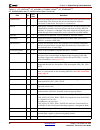

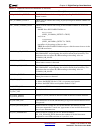

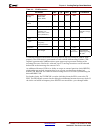

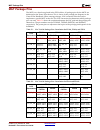

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 17 rocketio™ transceiver user guide 1-800-255-7778 clock synthesizer r table 2-4 lists the 16 gigabit transceiver primitives provided. These primitives carry attributes set to default values for the communications protocols listed in table 2-2 . Data widt...

Page 18: Clock and Data Recovery

18 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 2: rocketio transceiver overview r clock and data recovery the clock/data recovery (cdr) circuits lock to the reference clock automatically if the data is not present. For proper operation, freque...

Page 19: Receiver

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 19 rocketio™ transceiver user guide 1-800-255-7778 receiver r by specifying inverted running disparity for the second and fourth bytes. Transmit fifo proper operation of the circuit is only possible if the fpga clock (txusrclk) is frequency-locked to the ...

Page 20: Loopback

20 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 2: rocketio transceiver overview r receiver termination on-chip termination is provided at the receiver, eliminating the need for external termination. The receiver includes programmable on-chip t...

Page 21

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 21 rocketio™ transceiver user guide 1-800-255-7778 elastic and transmitter buffers r elastic and transmitter buffers both the transmitter and the receiver include buffers (fifos) in the data path. This section gives the reasons for including the buffers a...

Page 22

22 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 2: rocketio transceiver overview r similarly, if rxusrclk is slower than rxrecclk, the buffer fills up over time. The clock correction logic corrects for this by incrementing the read pointer to s...

Page 23: Crc

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 23 rocketio™ transceiver user guide 1-800-255-7778 crc r recognizes the "p" channel bonding character, and remembers its location in the buffer. At some point, one transceiver designated as the master instructs all the transceivers to align to the channel...

Page 24

24 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 2: rocketio transceiver overview r additional reset and power control descriptions are given in table 2-7 and table 2-8 . Table 2-7: reset and power control descriptions ports description rxreset ...

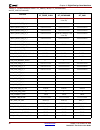

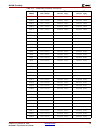

Page 25: List Of Available Ports

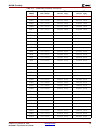

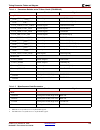

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 25 rocketio™ transceiver user guide 1-800-255-7778 r chapter 3 digital design considerations list of available ports the rocketio transceiver primitives contain 50 ports, with the exception of the 46-port gt_ethernet and gt_fibre_chan primitives. The diff...

Page 26

26 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r powerdown i 1 shuts down both the receiver and transmitter sides of the transceiver when asserted high. This decreases the power consumption while the transceive...

Page 27

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 27 rocketio™ transceiver user guide 1-800-255-7778 list of available ports r rxpolarity i 1 similar to txpolarity, but for rxn and rxp. When deasserted, assumes regular polarity. When asserted, reverses polarity. Rxrealign o 1 signal from the pma denoting...

Page 28

28 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r txforcecrcerr i 1 specifies whether to insert error in computed crc. When txforcecrcerr = true, the transmitter corrupts the correctly computed crc value by xori...

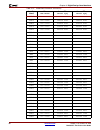

Page 29: Primitive Attributes

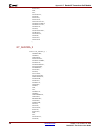

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 29 rocketio™ transceiver user guide 1-800-255-7778 primitive attributes r primitive attributes the primitives also contain attributes set by default to specific values controlling each specific primitive’s protocol parameters. Included are channel-bonding...

Page 30

30 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r chan_bond_offset integer 0-15 that defines offset (in bytes) from channel bonding sequence for realignment. It specifies the first elastic buffer read address th...

Page 31

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 31 rocketio™ transceiver user guide 1-800-255-7778 primitive attributes r clk_cor_keep_idle true/false controls whether or not the final byte stream must retain at least one clock correction sequence. False: transceiver can remove all clock correction seq...

Page 32

32 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r dec_mcomma_detect true/false controls the raising of per-byte flag rxchariscomma on minus-comma. Dec_pcomma_detect true/false controls the raising of per-byte fl...

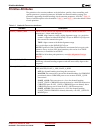

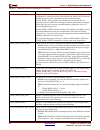

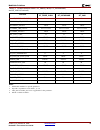

Page 33: Modifiable Primitives

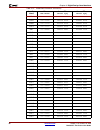

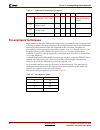

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 33 rocketio™ transceiver user guide 1-800-255-7778 modifiable primitives r modifiable primitives as shown in table 3-3 and table 3-4 , only certain attributes are modifiable for any primitive. These attributes help to define the protocol used by the primi...

Page 34

34 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r chan_bond_seq_1_3 00000000000 00000000000 00000000000 chan_bond_seq_1_4 00000000000 00000000000 00000000000 chan_bond_seq_2_1 00000000000 00000000000 00000000000...

Page 35

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 35 rocketio™ transceiver user guide 1-800-255-7778 modifiable primitives r pcomma_detect true true true ref_clk_v_sel (6) 0 0 0 rx_buffer_use true true true rx_crc_use false (2) false false (2) rx_data_width n (3) 2 n (3) rx_decode_use true true true rx_l...

Page 36

36 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r chan_bond_seq_1_2 00000000000 lane id (modify with lane id) 00000000000 chan_bond_seq_1_3 00000000000 00001001010 00000000000 chan_bond_seq_1_4 00000000000 00001...

Page 37

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 37 rocketio™ transceiver user guide 1-800-255-7778 modifiable primitives r lane id(infinband only) na 00000000000 (1) na mcomma_10b_value 1100000000 1100000000 1100000000 mcomma_detect true true true pcomma_10b_value 0011111000 0011111000 0011111000 pcomm...

Page 38: Byte Mapping

38 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r byte mapping most of the 4-bit wide status and control buses correlate to a specific byte of the txdata or rxdata. This scheme is shown in table 3-5 . This creat...

Page 39

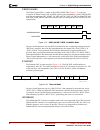

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 39 rocketio™ transceiver user guide 1-800-255-7778 clocking r clock ratio usrclk2 clocks the data buffers. The ability to send parallel data to the transceiver at three different widths requires the user to change the frequency of usrclk2. This creates a ...

Page 40

40 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r example 1: two-byte clock the following hdl codes are examples of a simple clock scheme using 2-byte data with both usrclk and usrclk2 at the same frequency. Usr...

Page 41

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 41 rocketio™ transceiver user guide 1-800-255-7778 clocking r ); end component; -- component dcm port ( clkin : in std_logic; clkfb : in std_logic; dssen : in std_logic; psincdec : in std_logic; psen : in std_logic; psclk : in std_logic; rst : in std_logi...

Page 42

42 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r u2_bufg: bufg port map ( i => clk0_w, o => usrclk_m ); end two_byte_clk_arch; verilog template //module: two_byte_clk //description: verilog submodule // dcm for...

Page 43

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 43 rocketio™ transceiver user guide 1-800-255-7778 clocking r .O ( refclkinbuf )); endmodule example 2: four-byte clock if a 4-byte or 1-byte data path is chosen, the ratio between usrclk and usrclk2 changes. The time it take for the serdes to serialize t...

Page 44

44 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r port ( i : in std_logic; o : out std_logic ); end component; -- component ibufg port ( i : in std_logic; o : out std_logic ); end component; -- component dcm por...

Page 45

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 45 rocketio™ transceiver user guide 1-800-255-7778 clocking r port map ( i => refclkin, o => refclk ); u2_bufg: bufg port map ( i => clk0_w, o => usrclk_m ); u3_bufg: bufg port map ( i => clkdv_w, o => usrclk2_m ); end four_byte_clk_arch; verilog template...

Page 46

46 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r .Clk2x180 ( ), .Clkdv ( clkdv2 ), .Clkfx ( ), .Clkfx180 ( ), .Locked ( dcm_locked ), .Psdone ( ), .Status ( ) ); bufg buf1 ( .I ( clkdv2 ), .O ( usrclk2_m ) ); b...

Page 47

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 47 rocketio™ transceiver user guide 1-800-255-7778 clocking r port ( refclkin : in std_logic; rst : in std_logic; usrclk_m : out std_logic; usrclk2_m : out std_logic; refclk : out std_logic; lock : out std_logic ); end one_byte_clk; -- architecture one_by...

Page 48

48 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r clk1x clk1x_w; -- -- dcm instantiation u_dcm: dcm port map ( clkin => refclk, clkfb => usrclk_m, dssen => gnd, psincdec => gnd, psen => gnd, psclk => gnd, rst =>...

Page 49

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 49 rocketio™ transceiver user guide 1-800-255-7778 clocking r wire refclk; wire usrclk_m; wire usrclk2_m; wire dcm_locked; wire refclkinbuf; wire clk_i; wire clk_2x_180; dcm dcm1 ( .Clkfb ( usrclk_m ), .Clkin ( refclkinbuf), .Dssen ( 1'b0 ), .Psclk ( 1'b0...

Page 50

50 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r brefclk at speeds of 2.5 gb/s or greater, the refclk configuration introduces more than the maximum allowable jitter to the rocketio transceiver. For these highe...

Page 51

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 51 rocketio™ transceiver user guide 1-800-255-7778 clocking r table 3-9 shows the brefclk pin numbers for all packages. Note that these pads must be used for brefclk operations table 3-9: brefclk pin numbers package top bottom brefclk pin number brefclk2 ...

Page 52

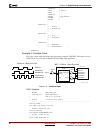

52 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r half-rate clocking scheme some applications require serial speeds between 622 mb/s and 1 gb/s. The transceiver attribute serdes_10b, which sets the refclk multip...

Page 53

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 53 rocketio™ transceiver user guide 1-800-255-7778 clocking r multiplexed clocking scheme following configuration of the fpga, some applications might need to change the frequency of its refclk depending on the protocol used. Figure 3-8 shows how the desi...

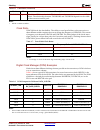

Page 54: Resets

54 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r receiver latency • latencies for rx_buffer_use = true • if rx elastic buffer is bypassed (rx_buffer_use = false), subtract 18. Clock dependency all signals used ...

Page 55

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 55 rocketio™ transceiver user guide 1-800-255-7778 resets r architecture rtl of gt_reset is -- signal startup_count : std_logic_vector (7 downto 0); begin process (usrclk2_m, dcm_locked) begin if (usrclk2_m' event and usrclk2_m = '1') then if(dcm_locked =...

Page 56

56 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r rocketio transceiver instantiations for the different clocking schemes, several things must change, including the clock frequency for usrclk and usrclk2 discusse...

Page 57

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 57 rocketio™ transceiver user guide 1-800-255-7778 pll operation and clock recovery r rx_loss_of_sync_fsm the transceivers fsm is driven by rxreclk and uses status from the data stream prior to the elastic buffer. This is intended to give early warning of...

Page 58

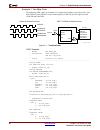

58 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r figure 3-9: 8b/10b data flow ug024_09_020802 tx+ tx − rx+ rx − channel bonding and clock correction tx clock generator rx clock recovery refclk deserializer comm...

Page 59

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 59 rocketio™ transceiver user guide 1-800-255-7778 pll operation and clock recovery r during transmit, while 8b/10b encoding is enabled, the disparity of the serial transmission can be controlled with the txchardispval and txchardispmode ports. When 8b/10...

Page 61: Status Signals

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 61 rocketio™ transceiver user guide 1-800-255-7778 status signals r status signals whether the 8b/10b encoding is enabled or disabled, there are several status signals for error indication. If an invalid k-character is sent to the transceiver, the txkerr ...

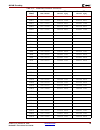

Page 62

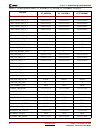

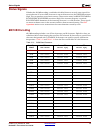

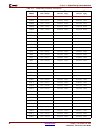

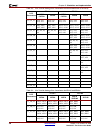

62 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r d22.0 000 10110 011010 1011 011010 0100 d23.0 000 10111 111010 0100 000101 1011 d24.0 000 11000 110011 0100 001100 1011 d25.0 000 11001 100110 1011 100110 0100 d...

Page 63

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 63 rocketio™ transceiver user guide 1-800-255-7778 8b/10b encoding r d23.1 001 10111 111010 1001 000101 1001 d24.1 001 11000 110011 1001 001100 1001 d25.1 001 11001 100110 1001 100110 1001 d26.1 001 11010 010010 1001 010110 1001 d27.1 001 11011 110110 100...

Page 64

64 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r d24.2 010 11000 110011 0101 001100 0101 d25.2 010 11001 100110 0101 100110 0101 d26.2 010 11010 010010 0101 010110 0101 d27.2 010 11011 110110 0101 001001 0101 d...

Page 65

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 65 rocketio™ transceiver user guide 1-800-255-7778 8b/10b encoding r d25.3 011 11001 100110 1100 100110 0011 d26.3 011 11010 010110 1100 010110 0011 d27.3 011 11011 110110 0011 001001 1100 d28.3 011 11100 001110 1100 001110 0011 d29.3 011 11101 101110 001...

Page 66

66 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r d26.4 100 11010 010010 1101 010110 0010 d27.4 100 11011 110110 0010 001001 1101 d28.4 100 11100 001110 1101 001110 0010 d29.4 100 11101 101110 0010 010001 1101 d...

Page 67

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 67 rocketio™ transceiver user guide 1-800-255-7778 8b/10b encoding r d27.5 101 11011 110110 1010 001001 1010 d28.5 101 11100 001110 1010 001110 1010 d29.5 101 11101 101110 1010 010001 1010 d30.5 101 11110 011110 1010 100001 1010 d31.5 101 11111 101011 101...

Page 68

68 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r d28.6 110 11100 001110 0110 001110 0110 d29.6 110 11101 101110 0110 010001 0110 d30.6 110 11110 011110 0110 100001 0110 d31.6 110 11111 101011 0110 010100 0110 d...

Page 69

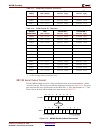

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 69 rocketio™ transceiver user guide 1-800-255-7778 8b/10b encoding r 8b/10b serial output format the 8b/10b encoding translates a 8-bit parallel data byte to be transmitted into a 10-bit serial data stream. This conversion and data alignment are shown in ...

Page 70: Crc Operation

70 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r the serial data bit sequence is dependent on the width of the parallel data. The most significant byte is always sent first regardless of the whether 1-byte, 2-b...

Page 71

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 71 rocketio™ transceiver user guide 1-800-255-7778 crc operation r the transmitter computes 4-byte crc on the packet data between the sop and eop (excluding the crc placeholder bytes). The transmitter inserts the computed crc just before the eop. The tran...

Page 72

72 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r fibrechannel the fibre channel crc is similar to the user_mode crc ( figure 3-15 ) with one exception: in fibrechannel, sop and eop are the protocol delimiters, ...

Page 73

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 73 rocketio™ transceiver user guide 1-800-255-7778 channel bonding (channel-to-channel alignment) r there are also two infiniband architecture (iba) packets, a local and a global. Both of these iba packets are shown in figure 3-17 . The crc is calculated ...

Page 74

74 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r master that can also be daisy chained to a slave_2_hops. A slave_2_hops can only be a slave to a slave_1_hop and its chbondo does not connect to another transcei...

Page 75

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 75 rocketio™ transceiver user guide 1-800-255-7778 other important design notes r other important design notes receive data path 32-bit alignment the rocketio transceiver uses the attribute align_comma_msb to align protocol delimiters with the use of comm...

Page 76

76 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r when rxdata is 32-bit misaligned, the word requiring alignment is split between consecutive rxdata words in the data stream, as shown in figure 3-20 . This condi...

Page 77

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 77 rocketio™ transceiver user guide 1-800-255-7778 other important design notes r // this module reads rxdata[31:0] from a rocketio transceiver // and copies it to // its output, realigning it if necessary so that commas // are aligned to the msb position...

Page 78

78 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r // counter is set to a high value // whenever the elastic buffer is reinitialized; // that is, upon asserted rxreset or // rxrealign. Count-down is enabled whene...

Page 79

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 79 rocketio™ transceiver user guide 1-800-255-7778 other important design notes r rxisk_reg aligned_rxisk byte_sync end else begin rxdata_reg[15:0] rxisk_reg[1:0] if ( rxchariscomma3 ) begin aligned_data[31:0] aligned_rxisk[3:0] byte_sync end else if ( rx...

Page 80

80 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r -- are aligned to the msb position -- [31:24]. The module assumes align_comma_msb is true, -- so that the comma -- is already aligned to [31:24] or [15:8]. -- --...

Page 81

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 81 rocketio™ transceiver user guide 1-800-255-7778 other important design notes r -- which are used only to -- maintain output sync; this provides some idea -- of when the output is properly -- aligned, with the comma in aligned_data[31:24]. -- the counte...

Page 82

82 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 3: digital design considerations r end process; -- this process generates aligned_data with commas -- aligned in [31:24], -- assuming that incoming commas are aligned -- to [31:24] or [15:8]. -- h...

Page 83: Analog Design Considerations

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 83 rocketio™ transceiver user guide 1-800-255-7778 r chapter 4 analog design considerations serial i/o description the rocketio transceiver transmits and receives serial differential signals. This feature operates at a nominal supply voltage of 2.5 vdc. A...

Page 84: Pre-Emphasis Techniques

84 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r pre-emphasis techniques in pre-emphasis, the initial differential voltage swing is boosted to create a stronger rising or falling waveform. This method compensate...

Page 85

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 85 rocketio™ transceiver user guide 1-800-255-7778 pre-emphasis techniques r figure 4-2: alternating k28.5+ with no pre-emphasis figure 4-3: k28.5+ with pre-emphasis ug024_17_020802 ug024_18_020802 logic high strong high strong low logic low.

Page 86

86 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r figure 4-4: eye diagram, 10% pre-emphasis figure 4-5: eye diagram, 33% pre-emphasis ug024_36_091802 ug024_37_091802.

Page 87: Differential Receiver

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 87 rocketio™ transceiver user guide 1-800-255-7778 differential receiver r differential receiver the differential receiver accepts the v p and v n signals, carrying out the difference calculation v p - v n electronically. All input data must be differenti...

Page 88

88 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r a sufficient number of transitions must be present in the data stream for cdr to work properly. The cdr circuit is guaranteed to work with 8b/10b encoding. Furthe...

Page 89: Pcb Design Requirements

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 89 rocketio™ transceiver user guide 1-800-255-7778 pcb design requirements r pcb design requirements in order to ensure reliable operation of the rocketio transceivers, certain requirements must be met by the designer. This section outlines these requirem...

Page 90

90 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r for the adjustable version of the lt1963 device with values for a 2.5 v supply, as would be used for avccauxrx and avccauxtx. Alternatively, fixed output voltage ...

Page 91

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 91 rocketio™ transceiver user guide 1-800-255-7778 pcb design requirements r all avccauxtx and avccauxrx pins in a virtex-ii pro device must be connected to 2.5 v, regardless of whether or not they are used. See powering the rocketio transceivers and the ...

Page 92

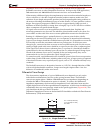

92 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r impedance traces with a corresponding impedance should be used to connect the rocketio transceiver to other compatible transceivers. In chip-to-chip pcb applicati...

Page 93

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 93 rocketio™ transceiver user guide 1-800-255-7778 pcb design requirements r tight coupling of differential traces is recommended. Tightly coupled traces (as opposed to loosely coupled) maintain a very close proximity to one another along their full lengt...

Page 94

94 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r capacitors of value 0.01 µ f in a 0402 package are suitable for ac coupling at 3.125 gb/s when 8b/10b encoding is used. Different data rates and different encodin...

Page 95

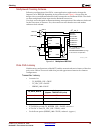

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 95 rocketio™ transceiver user guide 1-800-255-7778 other important design notes r other important design notes powering the rocketio transceivers important! All rocketio transceivers in the fpga, whether instantiated in the design or not, must be connecte...

Page 96

96 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 4: analog design considerations r.

Page 97: Simulation Models

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 97 rocketio™ transceiver user guide 1-800-255-7778 r chapter 5 simulation and implementation simulation models smartmodels smartmodels are encrypted versions of the actual hdl code. These models allow the user to simulate the actual functionality of the d...

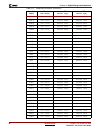

Page 98

98 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 5: simulation and implementation r ucf example net "chbond_*" maxdelay = 4.2 ns ; 4.2 ns is estimated as the channel bonding delay. This is based upon an rxusrclk of 156.25 mhz (6.4 ns period), le...

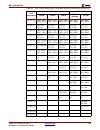

Page 99: Mgt Package Pins

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 99 rocketio™ transceiver user guide 1-800-255-7778 mgt package pins r mgt package pins the mgts are a hard core placed in the fpga fabric; all package pins for the mgts are dedicated on the virtex-ii pro device. This is shown in the package pin diagrams i...

Page 100

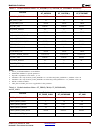

100 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 5: simulation and implementation r gt_x2_y1 a14, a13, a12, a11 a14, a13, a12, a11 a17, a16, a15, a14 a21, a20, a19, a18 a25, a24, a23, a22 gt_x3_y0 ak7, ak6, ak5, ak4 ak7, ak6, ak5, ak4 ap13, ap1...

Page 101

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 101 rocketio™ transceiver user guide 1-800-255-7778 mgt package pins r gt_x2_y0 aw24, aw23, aw22, aw21 aw28, aw27, aw26, aw25 aw32, aw31, aw30, aw29 bb33, bb32, bb31, bb30 bb37, bb36, bb35, bb34 gt_x2_y1 a24, a23, a22, a21 a28, a27, a26, a25 a32, a31, a30...

Page 102: Diagnostic Signals

102 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide chapter 5: simulation and implementation r diagnostic signals often a diagnostic check is needed upon power-up. Rocketio transceivers have several inputs and outputs to run these checks. Loopback loopbac...

Page 103

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 103 rocketio™ transceiver user guide 1-800-255-7778 r appendix a rocketio transceiver timing model this appendix explains all of the timing parameters associated with the rocketio™ transceiver core. It is intended to be used in conjunction with module 3 o...

Page 104: Timing Parameters

104 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix a: rocketio transceiver timing model r timing parameters parameter designations are constructed to reflect the functions they perform, as well as the i/o signals to which they are synchronous. T...

Page 105

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 105 rocketio™ transceiver user guide 1-800-255-7778 timing parameters r setup/hold times of inputs relative to clock basic format: parametername _ signal where parametername = t with subscript string defining the timing relationship signal = name of rocke...

Page 106

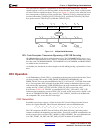

106 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix a: rocketio transceiver timing model r timing parameter tables and diagram the following four tables list the timing parameters as reported by the implementation tools relative to the clocks giv...

Page 107

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 107 rocketio™ transceiver user guide 1-800-255-7778 timing parameter tables and diagram r table a-4: parameters relative to the tx user clock2 (txusrclk2) parameter function signals setup/hold: t gcck _cfgen/t gckc _cfgen control inputs configenable t gcc...

Page 108

108 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix a: rocketio transceiver timing model r figure a-2: rocketio transceiver timing relative to clock edge clock control inputs control outputs data outputs data inputs t xgwh t gcck t xgwl t gckc t ...

Page 109: Summary

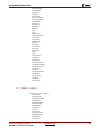

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 109 rocketio™ transceiver user guide 1-800-255-7778 r appendix b rocketio transceiver cell models summary this appendix documents the rocketio™ multi-gigabit transceiver cell models. The following information lists the verilog module declarations of the m...

Page 110

110 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r brefclk2, rxn, rxp, rxpolarity, rxreset, rxusrclk, rxusrclk2, txbypass8b10b, txchardispmode, txchardispval, txcharisk, txdata, txforcecrcerr, txinhibit, txp...

Page 111

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 111 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r rxusrclk, rxusrclk2, txbypass8b10b, txchardispmode, txchardispval, txcharisk, txdata, txforcecrcerr, txinhibit, txpolarity, txreset, txusrclk, txusrclk2 ); gt_aurora_4 modul...

Page 112

112 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r txcharisk, txdata, txforcecrcerr, txinhibit, txpolarity, txreset, txusrclk, txusrclk2 ); gt_custom module gt_custom ( chbonddone, chbondo, configout, rxbufs...

Page 113

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 113 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r txreset, txusrclk, txusrclk2 ); gt_ethernet_1 module gt_ethernet_1 ( configout, rxbufstatus, rxchariscomma, rxcharisk, rxcheckingcrc, rxclkcorcnt, rxcommadet, rxcrcerr, rxda...

Page 114

114 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r gt_ethernet_2 module gt_ethernet_2 ( configout, rxbufstatus, rxchariscomma, rxcharisk, rxcheckingcrc, rxclkcorcnt, rxcommadet, rxcrcerr, rxdata, rxdisperr, ...

Page 115

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 115 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r rxclkcorcnt, rxcommadet, rxcrcerr, rxdata, rxdisperr, rxlossofsync, rxnotintable, rxrealign, rxrecclk, rxrundisp, txbuferr, txkerr, txn, txp, txrundisp, configenable, config...

Page 116

116 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r rxrundisp, txbuferr, txkerr, txn, txp, txrundisp, configenable, configin, loopback, powerdown, refclk, refclk2, refclksel, brefclk, brefclk2, rxn, rxp, rxpo...

Page 117

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 117 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r powerdown, refclk, refclk2, refclksel, brefclk, brefclk2, rxn, rxp, rxpolarity, rxreset, rxusrclk, rxusrclk2, txbypass8b10b, txchardispmode, txchardispval, txcharisk, txdata...

Page 118

118 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r rxreset, rxusrclk, rxusrclk2, txbypass8b10b, txchardispmode, txchardispval, txcharisk, txdata, txforcecrcerr, txinhibit, txpolarity, txreset, txusrclk, txus...

Page 119

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 119 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r txbypass8b10b, txchardispmode, txchardispval, txcharisk, txdata, txforcecrcerr, txinhibit, txpolarity, txreset, txusrclk, txusrclk2 ); gt_infiniband_2 module gt_infiniband_2...

Page 120

120 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r txforcecrcerr, txinhibit, txpolarity, txreset, txusrclk, txusrclk2 ); gt_infiniband_4 module gt_infiniband_4 ( chbonddone, chbondo, configout, rxbufstatus, ...

Page 121

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 121 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r txusrclk2 ); gt_xaui_1 module gt_xaui_1 ( chbonddone, chbondo, configout, rxbufstatus, rxchariscomma, rxcharisk, rxcheckingcrc, rxclkcorcnt, rxcommadet, rxcrcerr, rxdata, rx...

Page 122

122 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r gt_xaui_2 module gt_xaui_2 ( chbonddone, chbondo, configout, rxbufstatus, rxchariscomma, rxcharisk, rxcheckingcrc, rxclkcorcnt, rxcommadet, rxcrcerr, rxdata...

Page 123

Ug024 (v1.5) october 16, 2002 www.Xilinx.Com 123 rocketio™ transceiver user guide 1-800-255-7778 verilog module declarations r chbondo, configout, rxbufstatus, rxchariscomma, rxcharisk, rxcheckingcrc, rxclkcorcnt, rxcommadet, rxcrcerr, rxdata, rxdisperr, rxlossofsync, rxnotintable, rxrealign, rxrecc...

Page 124

124 www.Xilinx.Com ug024 (v1.5) october 16, 2002 1-800-255-7778 rocketio™ transceiver user guide appendix b: rocketio transceiver cell models r.