Icom IC-F33GS Service Manual - page 12

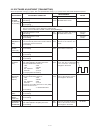

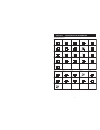

4-3 PLL CIRCUITS

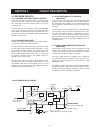

4-3-1 PLL CIRCUIT (MAIN UNIT)

A PLL circuit provides stable oscillation of the transmit fre-

quency and receive 1st LO frequency. The PLL output com-

pares the phase of the divided VCO frequency to the refer-

ence frequency. The PLL output frequency is controlled by

the divided ratio (N-data) of a programmable divider.

The PLL circuit contains the TX and RX VCO circuits (Q16,

Q17, D9–D11, D13, D500, D501). The oscillated signal is

amplified at the buffer amplifier (Q15). The output signal fre-

quency is doubled at Q14, and is then applied to the PLL IC

(IC21, pin 6) after being passed through the bandpass filter

(L32, C205, C507).

Q500, D502 and D503 switch the filtering frequencies

between TX and RX which is controlled by R5V.

The PLL IC contains a prescaler, programmable counter,

programmable divider and phase detector, etc. The applied

signal is divided at the prescaler and programmable counter

section by the N-data ratio from the CPU. The divided signal

is detected on phase at the phase detector using the refer-

ence frequency.

If the oscillated signal drifts, its phase changes from that of

the reference frequency, causing a lock voltage change to

compensate for the drift in the oscillated frequency.

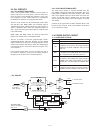

4-3-2 VCO CIRCUITS (MAIN UNIT)

The VCO circuits contains a separate RX VCO (Q17, D9,

D11, D500) and TX VCO (Q16, D10, D13, D501). The oscil-

lated signal is amplified at the buffer amplifiers (Q15, Q29)

and is then applied to the T/R switch (D16, D17). Then the

receive 1st LO (Rx) signal is applied to the 1st mixer (Q6)

and the transmit (Tx) signal to the YGR amplifier circuit (PA

unit; Q704).

A portion of the signal from the buffer amplifier (Q15) is fed

back to the PLL IC (IC21, pin 6) via the doubler circuit (Q14)

as the comparison signal.

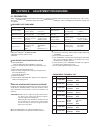

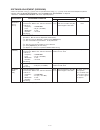

4-4 POWER SUPPLY CIRCUIT

4-1-1 MAIN UNIT VOLTAGE

LINE

DESCRIPTION

VCC

The voltage from the connected battery pack.

+5V

Common 5 V converted from the VCC line at the

+5 regulator circuit (IC17). The output voltage is

supplied to the buffer amplifiers (Q21), PLL IC

(IC21) etc.

S5V

Common 5 V converted from the VCC line at the

S5 regulator circuit (Q26–Q28). The output volt-

age is supplied to the ripple fi lter (Q20), etc.

R5V

Receive 5 V converted from the S5V line at the

R5 regulator circuit (Q25). The output voltage is

supplied to the tripler (Q22), FM IF IC (IC9), IF

amplifi er (Q7), 1st mixer (Q6), RF amplifi er (Q5),

etc.

T5V

Transmit 5 V converted from the S5V line at the

T5 regulator circuit (Q24). The output voltage is

supplied to the APC amplifi er (IC2), PA unit, etc.

Shift register

Prescaler

Phase

detector

Loop

filter

Programmable

counter

Programmable

divider

X2

15.3 MHz

10

Buffer

Q15

Buffer

Q21

Buffer

Q29

×

2

Q14

14

15

16

SCK

SO

PLST

to transmitter circuit

to 1st mixer circuit

D16

D17

4

6

Q16, D10, D13, D501

TX VCO

Q17, D9, D11, D500

RX VCO

IC21 LMX2352

3

45.9 MHz 2nd LO

signal to the FM IF IC

(IC9, pin 2)

Tripler

Q22

"LVIN" signal

to the CPU

(IC22, pin 49)

BPF

• PLL CIRCUIT

4 - 4