National Instruments NI 5782R User manual and specifications - page 7

NI 5782R User Manual and Specifications

|

© National Instruments

|

7

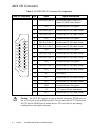

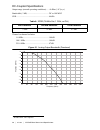

Block Diagram

Figure 3 shows the NI 5782 block diagram and signal flow to and from the NI 5782

component-level intellectual property (CLIP) by way of the adapter module and the

corresponding NI 5782 Multiple Sample CLIP in LabVIEW FPGA.

Figure 3.

NI 5782 Connector Signals and NI 5782 CLIP Signal Block Diagram

PFI Rd Data

LabVIEW FPGA CLIP

NI 5782 Adapter Module

PFI Wr Data

DIO Port Write Enable

PFI Write Enable

Trigger Input

SPI Read

SPI Write

SPI Address

SPI Write Data

SPI Read Data

SPI Device Select

Initialization Done

Reinitialize

Configuration Error

Sample Clock Select

Sample Clock Commit

SPI Idle

Data Clock

AI 0 Data N

AI 1 Data N

AO 0 Data N

AO 0 Data N–2

AI 0 Data N–1

AI 1 Data N–1

AO 0 Data N–1

AO 0 Data N–3

AO 1 Data N

AO 1 Data N–1

AO 1 Data N–2

AO 1 Data N–3

Data

Clock

Data

Sample

Clock

Clock

Buffer

Internal

Reference

Clock

Clock

Synthesizer

Switch

Switch

CLK IN

AUX I/O

TRIG

AI 0

AI 1

AO 0

AO 1

Switch

Clock

DAC

Interface

ADC

Interface

IOModSyncClock

ADC

DAC

Analog

Front End

Bus

Translator

Bus

Transceiver

2

4

DIO Port 0 Rd Data ,

DIO Port 1 Rd Data

DIO Port 0 Wr Data ,

DIO Port 1 Wr Data

8

8

4

4

Analog

Front End

Analog

Front End

Analog

Front End

AD9512

Synthesizer Locked

Analog front

end (FE)

Switches

ADCs

AD9512

SPI Engine

Interfacing

with:

DACs