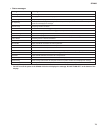

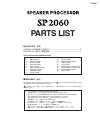

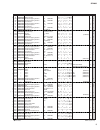

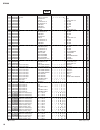

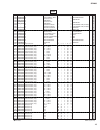

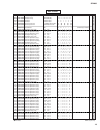

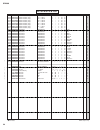

Yamaha SP2060 Service Manual - page 19

SP2060

19

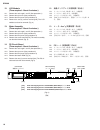

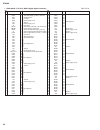

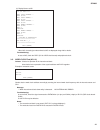

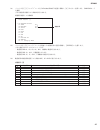

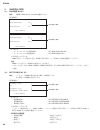

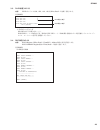

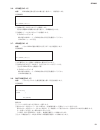

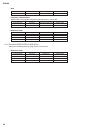

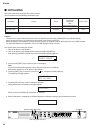

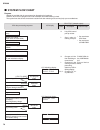

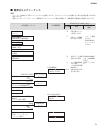

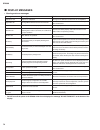

Pin

no.

Name

I/O

Function

Pin

no.

Name

I/O

Function

CPU: IC002

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

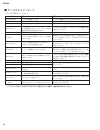

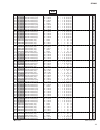

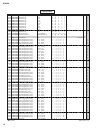

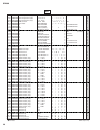

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

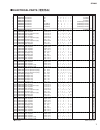

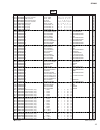

Reserved//CAS/PTJ[2]

VssQ

Reserved/PTJ[3]

VccQ

Reserved/PTJ[4]

Reserved/PTJ[5]

Vss

PTD[5]/CL1

Vcc

PTD[7]/DON

PTE[6]/M_DISP

PTE[3]/FLM

PTE[0]/TDO

PCC0RESET/DRACK0

PCC0DRV_/DACK0_

/WAIT

/RESETM

/ADTRG/PTH[5]

/IOIS16/PTG[7]

/ASEMD0

PTG[5]/ASEBRKAK_

PTG[4]

PCC0BVD2/PTG[3]/AUDATA[3]

PCC0BVD1/PTG[2]/AUDATA[2]

Vss

PCC0CD2/PTG[1]/AUDATA[1]

Vcc

PCC0CD1/PTG[0]/AUDATA[0]

VssQ

PTF[7]/PINT[15]/TRST_

VccQ

PTF[6]/PINT[14]/TMS

PTF[5]/PINT[13]/TDI

PTF[4]/PINT[12]/TCK

PTF[3]/PINT[11]/Reserved

PCCREG_/PTF[2]/Reserved

PCC0VS1_/PTF[1]/Reserved

PCC0VS2_/PTF[0]/Reserved

MD0

Vcc-PLL1

CAP1

Vss-PLL1

Vss-PLL2

CAP2

Vcc-PLL2

PCC0WAIT_/PTH[6]/AUDCK

Vss

Vcc

XTAL

EXTAL

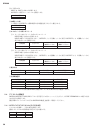

LCD15/PTM[3]/PINT[10]

LCD14/PTM[2]/PINT[9]

LCD13/PTM[1]/PINT[8]

LCD12/PTM[0]

STATUS0/PTJ[6]

STATUS1/PTJ[7]

CL2/PTH[7]

VssQ

CKIO

VccQ

TxD0/SCPT[0]

SCK0/SCPT[1]

TxD_SIO/SCPT[2]

SIOMCLK/SCPT[3]

TxD2/SCPT[4]

SCK_SIO/SCPT[5]

SIOFSYNC/SCPT[6]

RxD0/SCPT[0]

RxD_SIO/SCPT[2]

Vss

RxD2/SCPT[4]

Vcc

SCPT[7]/CTS2_/IRQ5

LCD11/PTC[7]/PINT[3]

LCD10/PTC[6]/PINT[2]

LCD9/PTC[5]/PINT[1]

VssQ

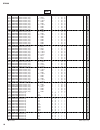

LCD8/PTC[4]/PINT[0]

VccQ

LCD7/PTD[3]

LCD6/PTD[2]

LCD5/PTC[3]

LCD4/PTC[2]

LCD3/PTC[1]

LCD2/PTC[0]

LCD1/PTD[1]

LCD0/PTD[0]

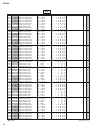

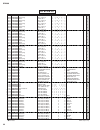

DREQ0_/PTD[4]

LCK/UCLK/PTD[6]

/RESETP

CA

MD3

MD4

/Scan_testen

Avcc_USB

USB1_P

USB1_M

Avss_USB

USB2_P

USB2_M

Avcc_USB

Avss

AN[2]/PTL[2]

AN[3]/PTL[3]

AN[4]/PTL[4]

AN[5]/PTL[5]

Avcc

AN[6]/PTL[6]/DA[1]

AN[7]/PTL[7]/DA[0]

Avss

CAS for SDRAM

VssQ

Output port (DAC Reset)

VccQ

Output port (SIO Reset)

Output port (DAC Mute)

Vss

LCD line clock

Vcc

LCD DISPLAY ON

LCD alternater

LCD frame line marker

JTAG (test data output)

DMA request acceptance

DMA acknowledge

Hardware wait request

Manual reset request

Analog A/D trigger

Not in use

Vss

Not in use

Vcc

Not in use

VssQ

Not in use

VccQ

Not in use

Clock mode setting

Power supply for Vcc_PLL1 - PLL1(1.9V)

External capacitance for CAP1 _ PLL1

Power supply for Vss_PLL1 _ PLL1(0V)

Power supply for Vss_PLL2 _ PLL2 (0V)

External capacitance for CAP2 _ PLL2

Power supply for Vcc_PLL2 _ PLL2 (1.9V)

Not in use

Vss

Vcc

Clock oscillator

External clock

Not in use

Input port (Flash ROM RY/BY)

Output port (Flash ROM write protect)

Output port (Flash ROM ACC)

LCD clock output

VssQ

System clock input/output (for SDRAM)

VccQ

Output port for SCI

Not in use

Output port for SCI

Not in use

Receiving data 0

Not in use

Vss

Receiving data 2

Vcc

Not in use

Output port (PLG CLOCK ON/OFF)

Not in use

VssQ

Not in use

VccQ

LCD DATA7

LCD DATA6

LCD DATA5

LCD DATA4

LCD DATA3

LCD DATA2

LCD DATA1

LCD DATA0

DMA request

USB clock

Power on reset request

Hardware standby request

Bus width setting for area0

Test pin (fixed to 3.3V)

USB analog power supply (3.3V)

USB1 data input/output (+)

USB1 data input/output (-)

USB analog power supply (0V)

USB2 data input/output (+)

USB2 data input/output (-)

USB analog power supply (3.3V)

A/D analog power supply (0V)

AD converter input

A/D analog power supply (3.3V)

AD converter input

DA converter output (LCD contrast)

A/D analog power supply (0V)

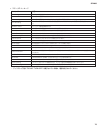

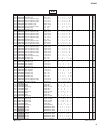

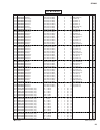

O

-

O

-

O

O

-

O

-

O

O

O

O

O

O

-

-

I

I

-

I

I

I

-

I

-

I

-

I

-

I

I

I

I

I

I

I

-

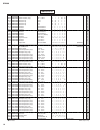

-

-

-

-

-

-

I

-

-

-

-

I

I

I

I

O

O

O

-

-

-

O

O

O

O

O

O

O

I

I

-

I

-

I

O

O

O

-

O

-

O

O

O

O

O

O

O

O

I

I

-

-

-

-

-

-

I/O

I/O

-

I/O

I/O

-

-

I

I

I

I

-

I

O

-