Garmin APOLLO GX SERIES Service Manual - page 34

Garmin AT

Rev --

6-2

GX Service Manual

© 2004 Garmin AT

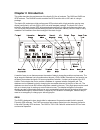

• Parallel

I/O

ports

• Watchdog Timer Unit (WDT)

• JTAG test-logic unit

The two serial I/O ports on the microprocessor connect directly to the GPS receiver (J1) and the

communication Comm board (J4) and are used for direct control and exchange of data between the

CPU and these devices.

The configuration jumper (J2) currently has only one function. The built-in test mode can be accessed

by shorting pins 7 and 8 together, then turning on the GX unit. The built-in test mode can also be

accessed by turning the unit on while depressing the two outermost smart keys, or by issuing a

command by PC through the serial port.

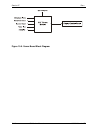

Reset/Watchdog/Battery Backup Circuit

The Maxim Max690A microprocessor supervisory IC (U1) provides a reset output (pin 7) during

power-up, power-down, or during failing power conditions. Additionally, a reset pulse is output (pin 7)

if the watchdog timer input (pin 6) has not been toggled within the specified time period (1-2.25 sec.).

The Max690A also provides Vcc to battery switchover (Vout pin 1) for SRAM backup power when the

GX unit is turned off. Backup power is supplied by a 3 V lithium backup battery.

Memory

Flash Code ROM

The NAV board is designed to accept 2 MBIT (128K x 16), 4 MBIT (256K x 16), or 8 MBIT (512K x

16) flash memories in the standard 48 pin TSOP package. There are two sites on the board (U102 &

U103) that can allow code flash memory in the range of 2 MBIT to 16 MBIT depending on the parts

populated.

The board design allows the use of Intel or AMD flash memories. Software routines are required for

programming the flash memories on the board, and both the Intel and AMD parts are supported. The

flash memories include device and manufacturer codes that can be read. Therefore, the software can

determine the device types and execute the appropriate programming algorithms.

The flash memories are soldered directly to the board; they are not placed in sockets. The flash must

be programmed in-circuit. The 386EX and the on-board hardware supports utilizing the JTAG port for

initial flash programming. The parts are programmed with +5 volts, so a +12 volt power supply is not

required.

SRAM

The NAV board design uses either one or two 1 MBIT (128K x 8) low-power SRAMs (U104 & U105).

The SRAM uses battery backup to save the contents when the unit is turned off.

When using a single SRAM, the device is connected for use in byte mode. The chip select

configuration must be set to byte access by software.

When using both SRAM devices, they are connected to allow word access. The BLE and BHE

connections allow for aligned and non-aligned word access as well as byte access.