IBM PPC750FX User Manual - page 36

Evaluation Board Manual

PPC750FX Evaluation Board

Preliminary

Programming the System Controller

Page 36 of 115

750FXebm_ch4.fm

June 10, 2003

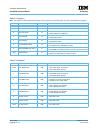

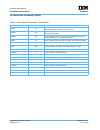

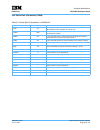

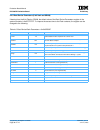

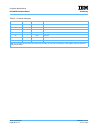

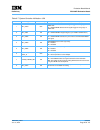

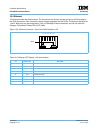

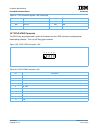

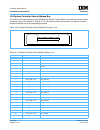

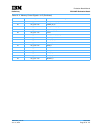

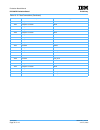

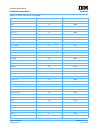

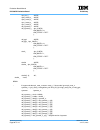

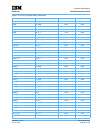

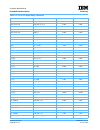

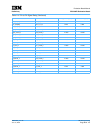

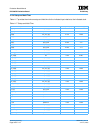

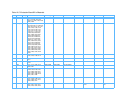

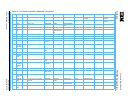

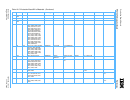

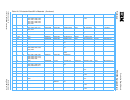

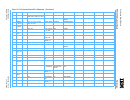

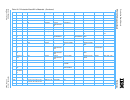

4.2.5 Boot Device Parameters (8 bit flash and SRAM)

If booting from the 8-bit Flash or SRAM, the default value of the Boot Device Parameters register in the

system controller is 0x8FCFFFFF. To improve the access time to the Flash contents, the register can be

changed to the following:

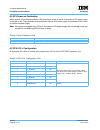

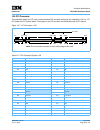

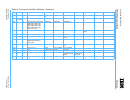

Table 4-6. Boot Device Bank Parameters = 0x8185D09E

Field

Value (bin)

Comment

TurnOff

110

Number of Sysclk cycles that the system controller does not drive the

address/data bus after completion of a device read

Acc2First

0011

Number of Sysclk cycles from the de-assertion of ALE to the cycle that the

first read data is sampled

Acc2Next

010

Number of Sysclk cycles in a burst read access between the cycle that

samples data N to the cycle that samples data N+1

ALE2Wr

010

Number of Sysclk cycles from ALE de-assertion to the assertion of Wr[0]

WrLow

111

Number of Sysclk cycles that Wr[0] is active

WrHigh

010

Number of Sysclk cycles between data beats of a burst write that Wr[0] is

held in-active. BAdr and data are held valid for WrHigh-1 cycles

DevWidth

00

Device width of 8 bits

TurnOffExt

0

TurnOff extension (most significant bit)

Acc2FirstExt

1

Acc2First extension (most significant bit)

Acc2NextExt

1

Acc2Next extension (most significant bit)

ALE2WrExt

0

ALE2Wr extension (most significant bit)

WrLowExt

0

WrLow extension (most significant bit)

WrHighExt

0

WrHigh extension (most significant bit)

BadrSkew

00

Number of Sysclk cycles from when BAdr changes to the read of the data

DPEn

0

Parity Disabled

Reserved

1