IBM PPC750FX User Manual - page 87

Evaluation Board Manual

Preliminary

PPC750FX Evaluation Board

750FXebm_ch11.fm

June 10, 2003

CPLD Programming

Page 87 of 115

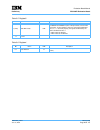

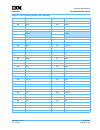

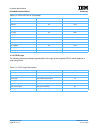

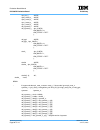

cpu0_smi_n = cpu0_smi_n_node; --

cpu1_smi_n = cpu1_smi_n_node; --

cpu_tben = cpu_tben_node; --

cpu_mcp0 = cpu_mcp0_node; --

cpu_mcp1 = cpu_mcp1_node; --

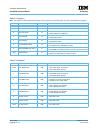

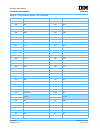

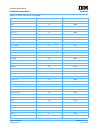

-- Register3, Write/Read

Register3.enable = Register3_sel & !ldevR_W_n;

Register3.aclr = !sysreset_n; -- !sysreset_n = 1 in reset, clears the output

Register3.clock = we_n0;

Register3.data[7..0] = dev_ad[7..0];

--

Register3.data[0] = dev_ad[0];-- mpp_block_n, 1 = pass mpp_Xreset pins

mpp_block_n

= Register3.q[0];-- mpp_block_n, 1 = pass mpp_Xreset pins

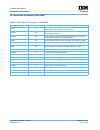

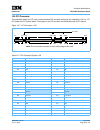

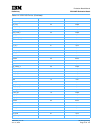

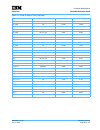

-- Register 0

if ((badr[2..0] == B"000")) then

PLDversion_sel = !fpga_cs_n;

data_sel[] = 0;

else

PLDversion_sel = gnd;

end if;

-- Register 1

if ((badr[2..0] == B"001")) then

Register1_sel = !fpga_cs_n;

data_sel[] = 1;

else

Register1_sel = gnd;

end if;

-- Register 2

if ((badr[2..0] == B"010")) then

Register2_sel = !fpga_cs_n;

data_sel[] = 2;

else

Register2_sel = gnd;

end if;

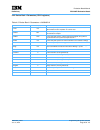

-- Register 3

if ((badr[2..0] == B"011")) then

Register3_sel = !fpga_cs_n;

data_sel[] = 3;

else

Register3_sel = gnd;

end if;