IBM PPC750FX User Manual - page 80

Evaluation Board Manual

PPC750FX Evaluation Board

Preliminary

CPLD Programming

Page 80 of 115

750FXebm_ch11.fm

June 10, 2003

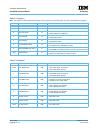

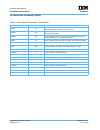

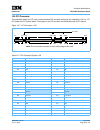

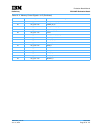

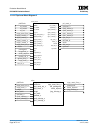

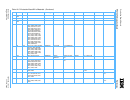

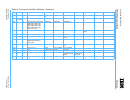

11.1.2.4 decode_block Program

The following code listing defines the function of the logic in the

decode_block

part of the CPLD:

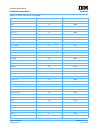

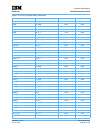

INCLUDE "lpm_ff.inc"; -- 10:30 AM Mar 26, 2003

INCLUDE "lpm_counter.inc";

SUBDESIGN decode_block

(

sysreset_n

: INPUT;

sysclk

: INPUT;

CSTiming_n

: INPUT;

LBootCS_n

: INPUT; -- 16 Bit flash/sram or 32 bit FLASH (32MB) chip select

lcs_n[3..0]

: INPUT; -- latched from upper address/data bus

ldev_addr[21..19] : INPUT; -- latched device address. Note that this is not the PowerPC conventional

-- address ordering. Device Addr0 is the LSB.

flash_n/sram_sel : INPUT;

bootsmall_n

: INPUT;

ldevR_W_n

: INPUT;

Dev_We_n0

: INPUT;

nvram_burst_cs_n: INPUT;

small_flash_lo_cs_n: OUTPUT; -- default lboot_cs_n, swappable to lcs_n[0]

small_flash_hi_cs_n: OUTPUT; -- default lboot_cs_n, swappable to lcs_n[0]

sram_lo_cs_n

: OUTPUT; -- default lboot_cs_n, swappable to lcs_n[0]

sram_hi_cs_n

: OUTPUT; -- default lboot_cs_n, swappable to lcs_n[0]

big_flash_cs_n

: OUTPUT; -- default lcs_n[0], swappable to lboot_cs_n

Read_n

: OUTPUT;

Write_n

: OUTPUT;

uart_cs_n

: OUTPUT; -- lcs_n[2]

nvram_cs_n

: OUTPUT; -- lcs_n[3]

test

: OUTPUT; -- test only

fpga_cs_n

: OUTPUT; -- lcs_n[1]

)

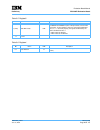

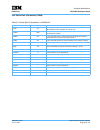

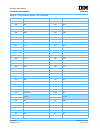

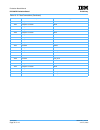

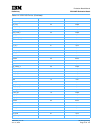

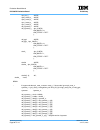

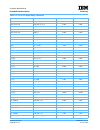

VARIABLE

abovebootarea

: NODE; -- memory above boot area

bootarea

: NODE; -- 750FX boots from this area

lowerarea

: NODE;

upperarea

: NODE;

hiarea

: NODE;

loarea

: NODE;

toparea

: NODE;

botarea

: NODE;

SRAM/FLASH/BIG : NODE; -- boot from small flash